Automatic reliability evaluation system and evaluation method based on Zynq FPGA

A technology for evaluating systems and reliability, applied in fault hardware testing methods, detecting faulty computer hardware, instruments, etc., can solve problems such as expensive equipment, inability to obtain statistical conclusions, and few faults, and achieve the effect of fast fault injection process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

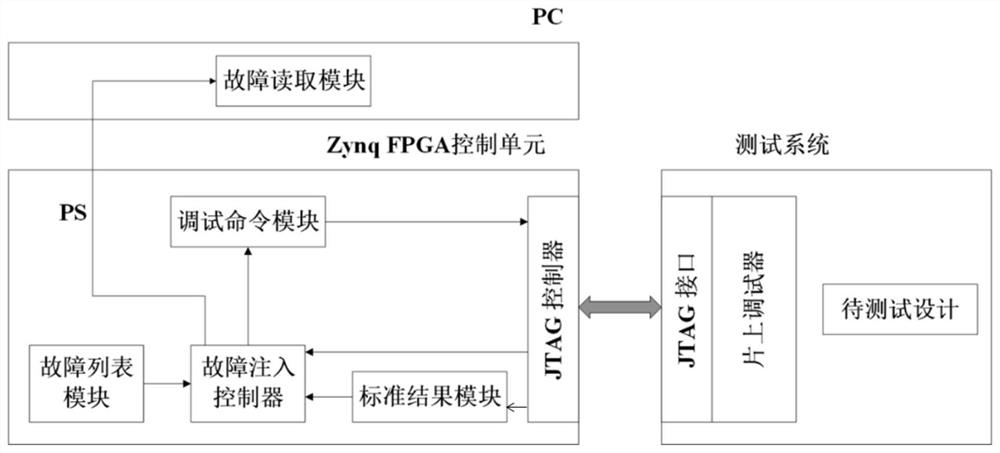

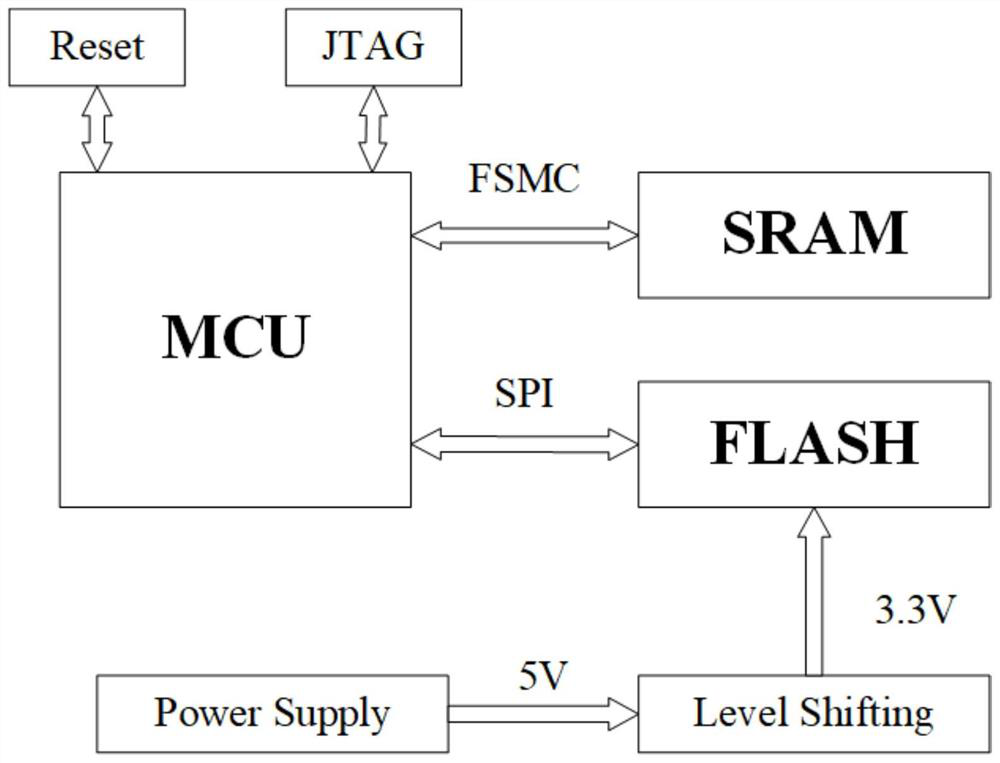

[0049] Take the 1024-point FFT implemented on the STM32F407ZGT6 processor as an example, such as figure 2 As shown, an automated reliability evaluation system based on ZynqFPGA is designed and tested, and the system framework for reliability evaluation of 1024-point FFT is as follows: figure 1 As shown, it includes the test system, FPGA control unit and PC-side fault reading module. The test system includes an on-chip debugger based on the JTAG interface, wherein the JTAG interface is used to link to the control unit JTAG controller; the on-chip debugger based on the JTAG interface includes four parts: data registers, instruction registers, interface ports and control modules. Each data register is associated with some part of the circuit. These data registers read information from the relevant circuit parts or provide input data. The test command loaded into the instruction register indicates the action to be performed and selects the data register to be used. . Data and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More