Systems and methods for performing dynamic on-chip calibration of memory control signals

A memory system, memory array technology, applied in the field of system-on-a-chip with improved calibration, can solve problems such as threats to multi-level cell capabilities, verification failures, failures, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

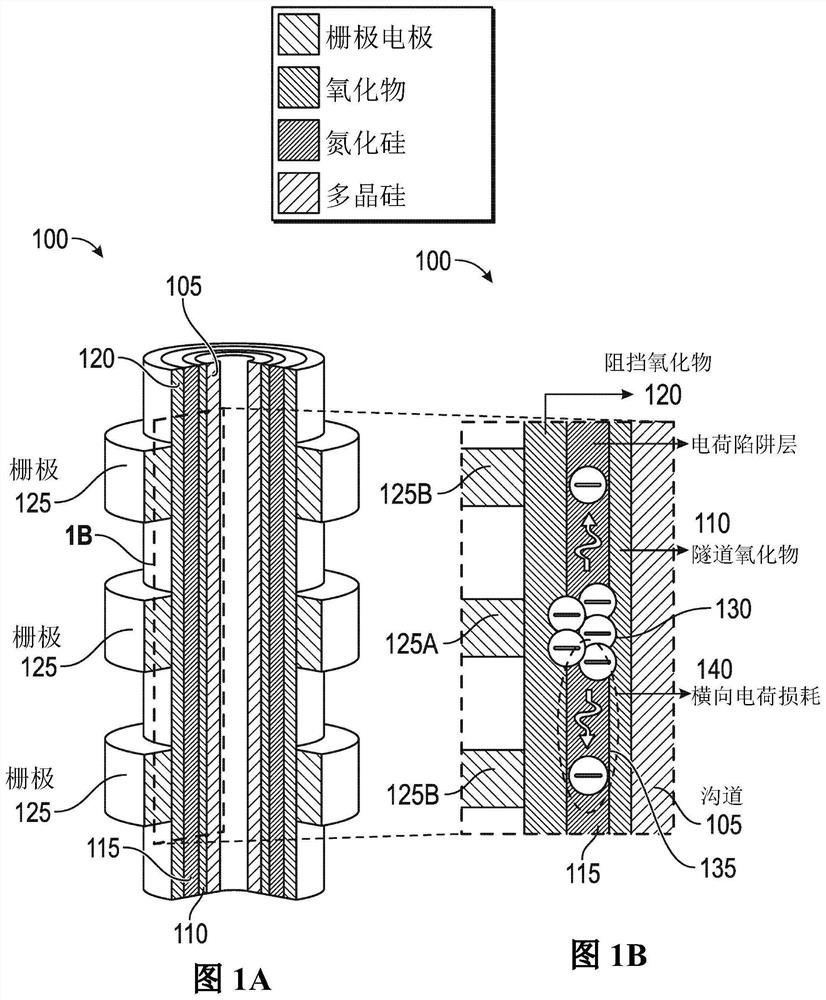

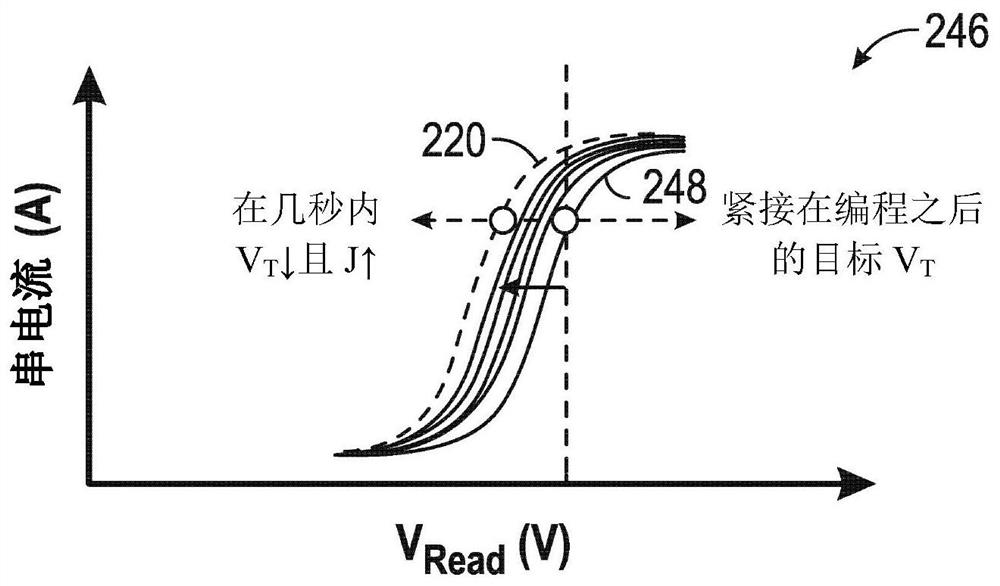

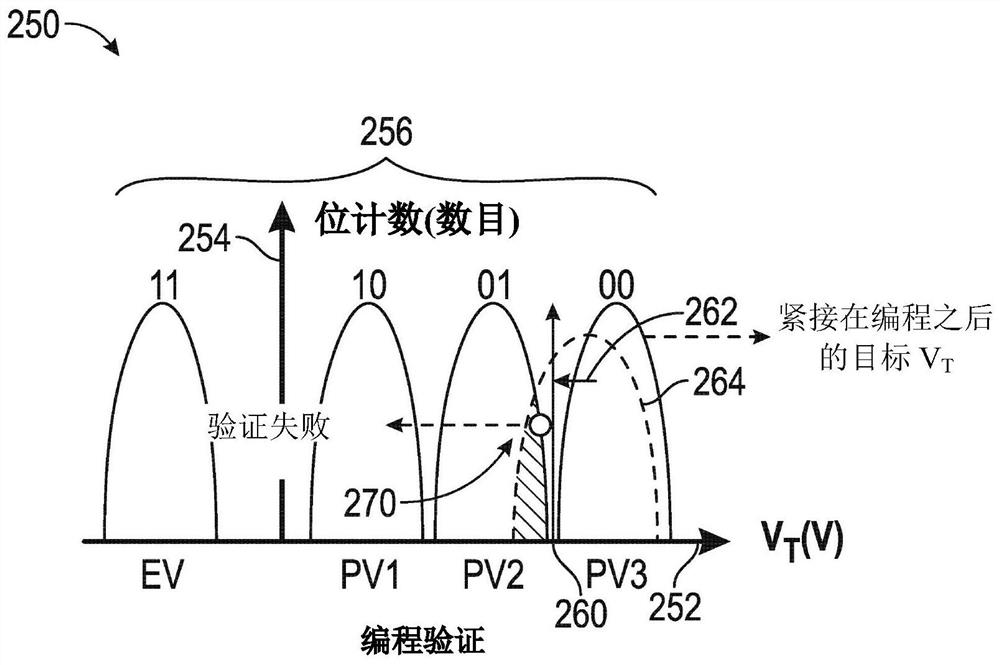

[0023] The following disclosure describes various embodiments of systems and methods of dynamically calibrating memory (read) control signals, eg, during increases in word line voltage. According to one embodiment, an exemplary method may include using an internal node, such as a wordline regulator output or return feedback line or a replica of the wordline, as a proxy for the local wordline voltage. In one or more other embodiments, the proxy signal may be converted to digital code and determined in the background even before it is needed for calibration. In accordance with the disclosed techniques, calibration of read control signals such as pass voltages and word line read verify voltages can be performed during the increase in the word line voltage without impact or loss in read / program time. Thus, systems and methods consistent with the disclosed techniques can avoid performance loss while enabling even NAND memory cells that exhibit the effects of rapid charge depletion ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com