FPGA on-chip clock duty ratio test method and clock self-test FPGA

A test method and technology of duty cycle, applied in the field of integrated circuits, can solve problems such as limiting the maximum measurement frequency, increasing test cost, and limited I/O interface performance, achieving the effect of reducing test cost and reducing index requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

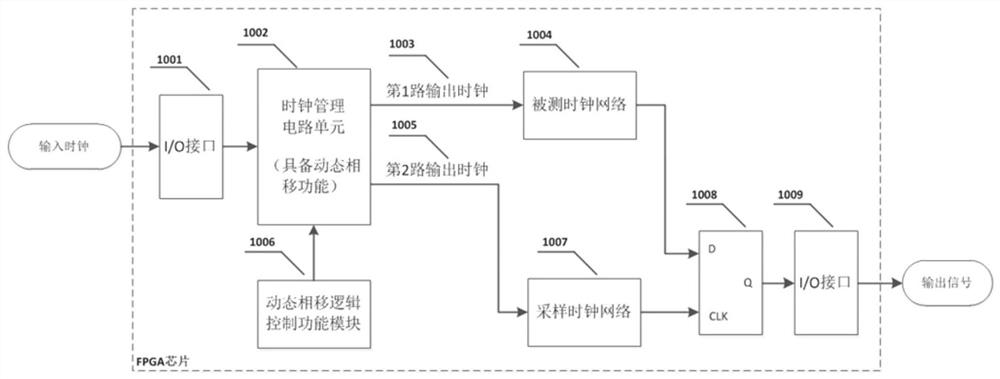

[0070] see Figure 8 , in this example figure 1 On the basis of a typical test system architecture, an output logic detection function circuit can be added without using an oscilloscope.

[0071] Because the maximum operating frequency that the logic circuit resources in the FPGA chip can achieve is far lower than the upper frequency limit that the clock management circuit unit can achieve. Therefore, the operating clock frequency of the output logic detection function circuit (8009) cannot be too high, and combined with engineering application experience, it can usually be set to an operating frequency of 200MHz or below. In order to meet this requirement, the operating frequency of the second output clock (8005) can be reduced, so that the frequency of the first output clock and the second output clock can maintain an integer multiple relationship, and the operating frequency of the second output clock can be lower than Outputting the operating clock frequency of the logi...

Embodiment 2

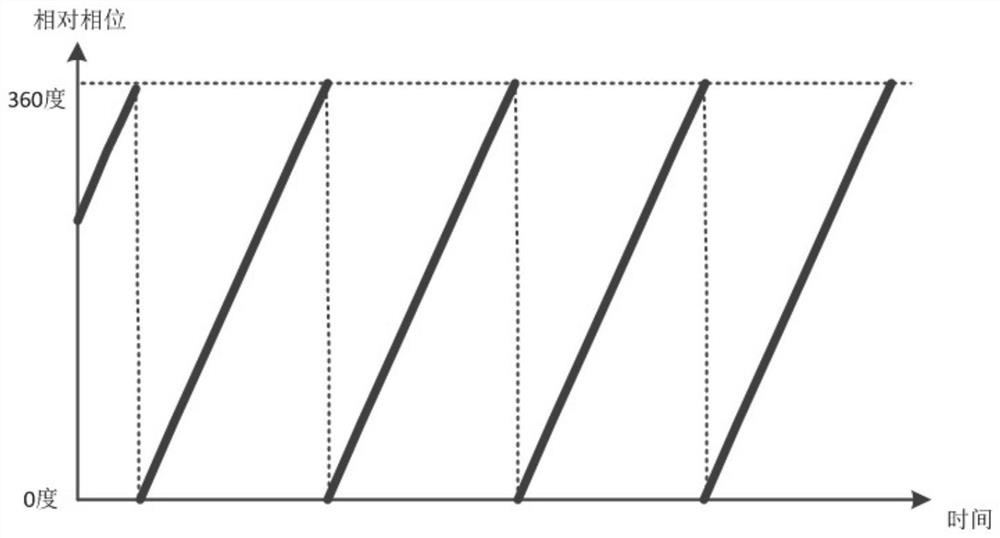

[0074] This embodiment describes the phase shift control process in detail, see Figure 9 ~ Figure 17 .

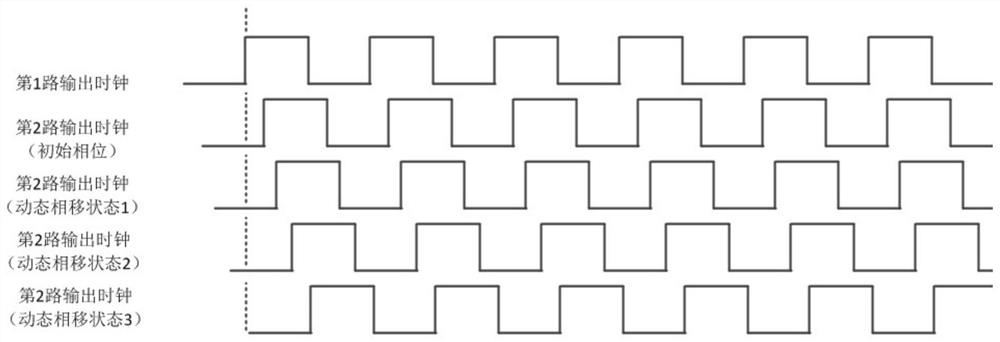

[0075] Figure 9 As shown, in the whole process of the duty cycle test, set Ps as a fixed phase adjustment step value, keep the CLK clock signal of the flip-flop for K clock cycles (K is an integer) in each phase state, and trigger The device samples the D input signal and outputs the Q signal.

[0076] Figure 10 ~ Figure 16 The principle of phase change between the CLK terminal input and the Q terminal output of the D flip-flop is shown in a step-by-step manner. The present invention scans the duty cycle of the high-frequency clock signal in the chip through low-speed phase scanning, greatly reduces the test cost, and can guarantee the test accuracy up to tens of picoseconds at the same time.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More