Hypergraph division method supporting interconnection constraints

A technology of graph division and resource constraints, which is applied in the fields of instruments, computing, and electrical digital data processing, etc., can solve the problems of performance degradation and cost increase, and achieve the effect of eliminating illegal line networks, reducing cost and ensuring performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

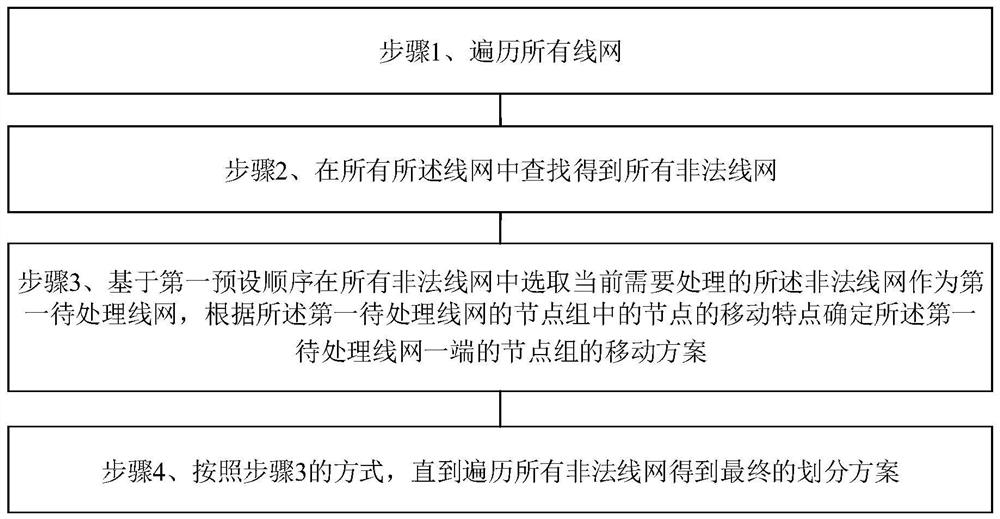

[0045] See figure 1 , figure 1 It is a schematic flowchart of a method for partitioning a hypergraph supporting interconnection constraints provided by an embodiment of the present invention. This embodiment provides a method for partitioning a hypergraph supporting interconnection constraints. The hypergraph partitioning method includes steps 1 to 4, wherein:

[0046] Step 1. Traverse all nets.

[0047] Step 1.1. Obtain the divided hypergraph.

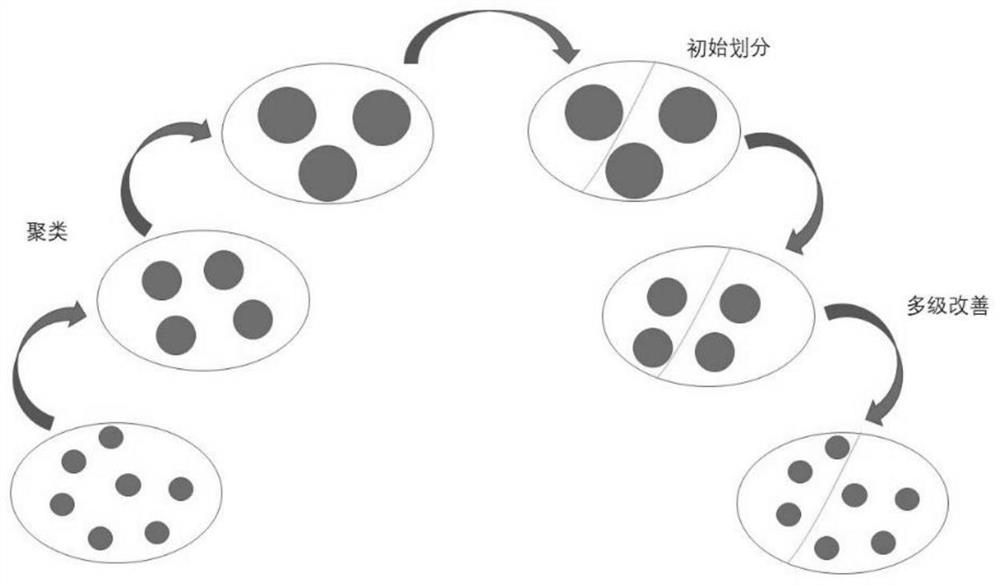

[0048] Specifically, see figure 2 , figure 2 It is a hypergraph after multi-level division, and the hypergraph can be a hypergraph obtained after the improvement is completed, or a hypergraph obtained during the multi-level improvement process.

[0049] Step 1.2, traverse all the nets in the hypergraph.

[0050]Specifically, there are generally multiple nets in each hypergraph, and each net has at least one node at each end.

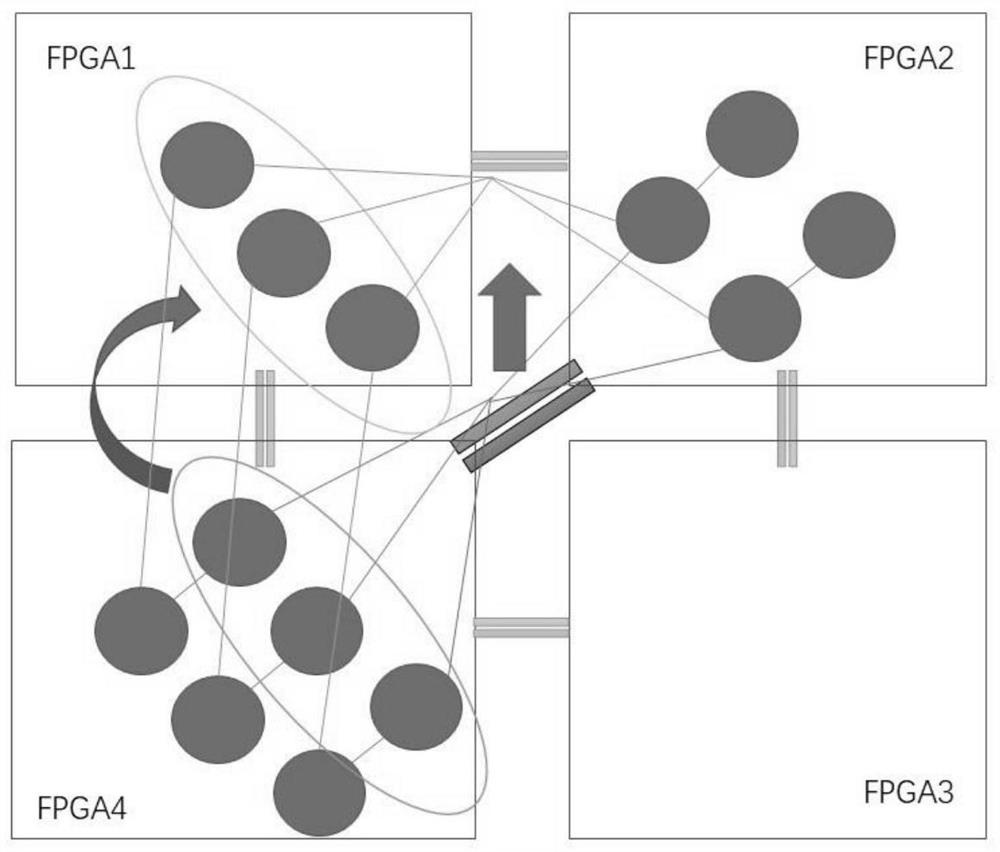

[0051] For example, see image 3 , the lines between FPGAs represent the interconnection resources...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More