Force steering layout method for expanding a crowded area based on maximum flow algorithm

A maximum flow and layout technology, applied in the field of FPGA layout, can solve the problems of long processing time, inability to completely eliminate the overlapping of layout results, and large volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

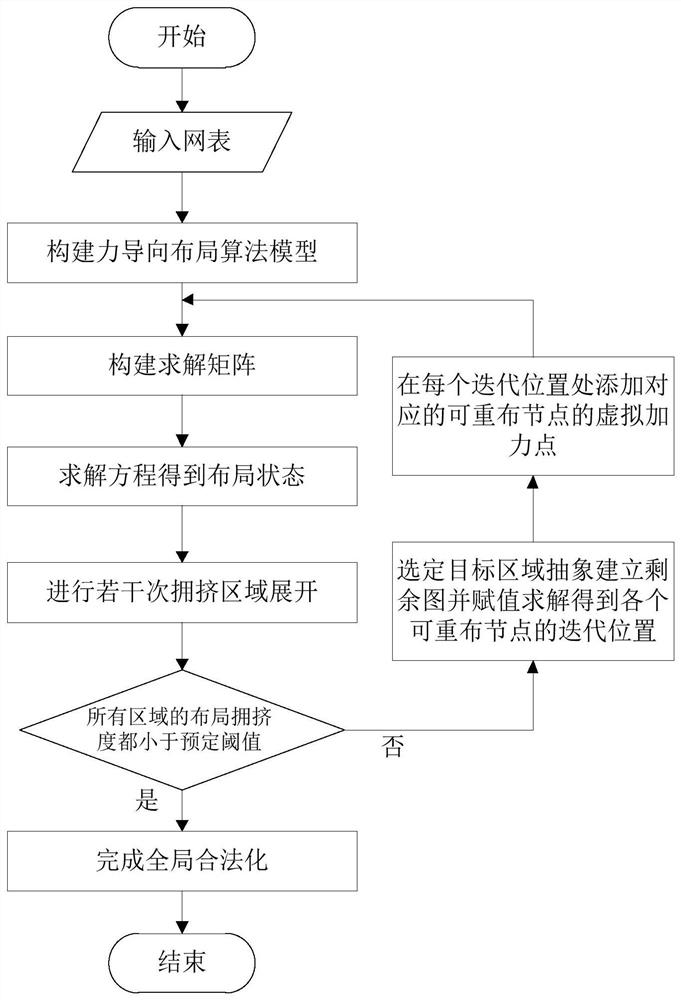

[0039] This application discloses a force-directed layout method based on the maximum flow algorithm for the expansion of crowded areas, please refer to figure 1 Shown in the flow chart, the method comprises the steps:

[0040] Step S1, obtain the input netlist corresponding to the FPGA chip, and solve the layout of the FPGA chip according to the input netlist using the force-directed layout algorithm model to obtain the layout state.

[0041] This application introduces the principle of the force-directed layout algorithm model (Quadratic algorithm model) as follows:

[0042] (1-1) Establishment of Quadratic netlist model.

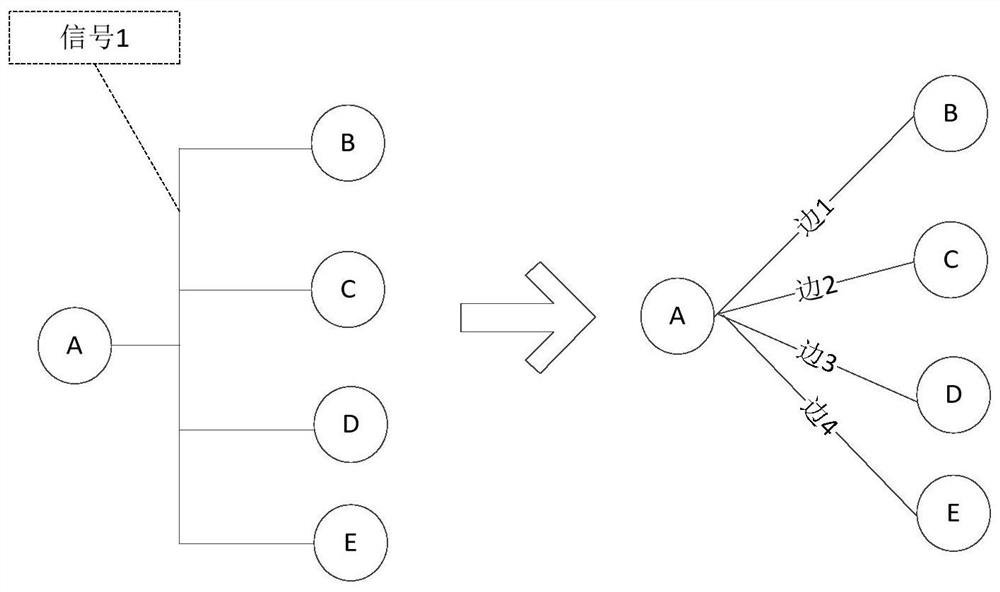

[0043] In the input netlist, all functional modules can be regarded as nodes, and the signal relationship between all nodes is established as a point-to-point edge relationship. Such as figure 2As shown, there are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com