Semiconductor device and method for manufacturing semiconductor element

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., to achieve the effect of component trace suppression

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

[0047] 1.1 Plane structure of semiconductor substrate

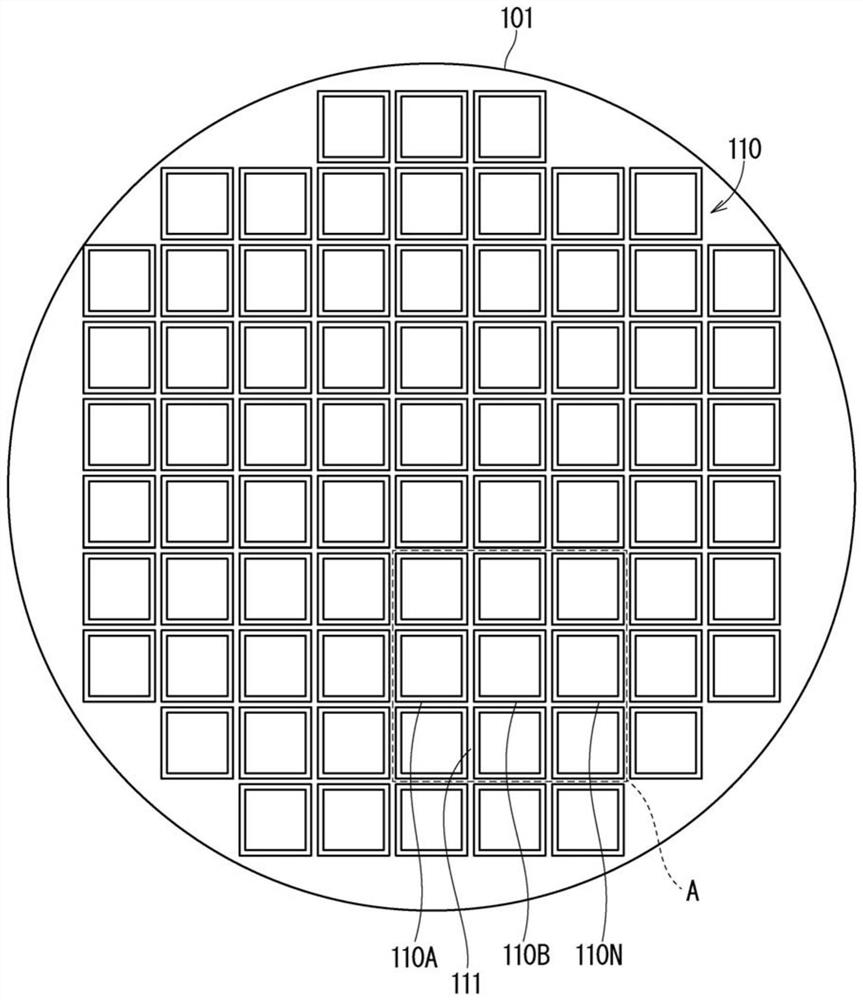

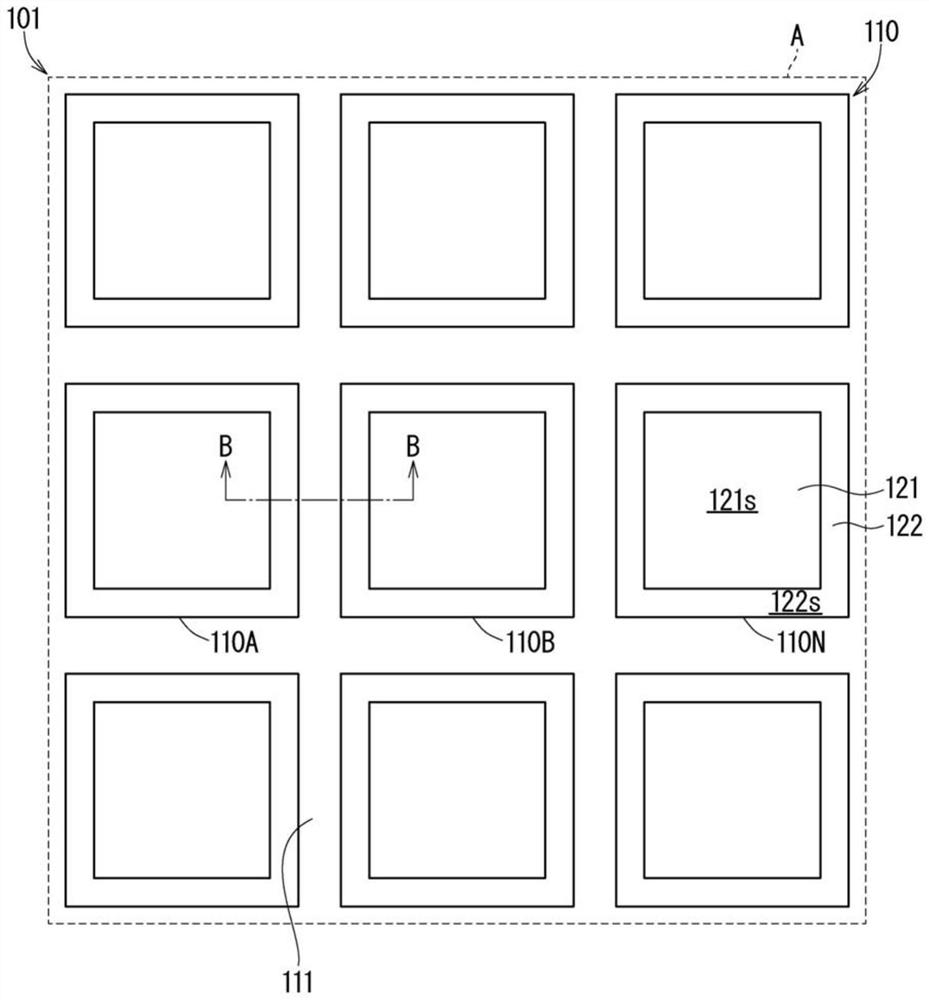

[0048] figure 1 It is a plan view schematically illustrating a semiconductor substrate included in the semiconductor device of the first embodiment. figure 2 It is an enlarged plan view schematically showing a part of the semiconductor substrate included in the semiconductor device according to the first embodiment. figure 2 right figure 1 Part A depicted in is shown enlarged.

[0049] figure 1 as well as figure 2 The illustrated semiconductor substrate 101 has a plurality of semiconductor elements 110 and inter-element portions 111 .

[0050] The plurality of semiconductor elements 110 are arranged in the direction in which the semiconductor substrate 101 spreads. exist figure 1 as well as figure 2 In the semiconductor substrate 101 shown, a plurality of semiconductor elements 110 are arranged in a matrix. The plurality of semiconductor elements 110 are formed by forming p-type diffusion layers, n-type diffu...

Embodiment approach 2

[0098] Figure 11 It is a flowchart illustrating the manufacturing method of the semiconductor element of the second embodiment.

[0099] The method of manufacturing a semiconductor element according to Embodiment 2 has Figure 11 Steps S1 to S6 are shown.

[0100] In step S1, the semiconductor substrate 101 is prepared.

[0101] When preparing the semiconductor substrate 101, a semiconductor wafer is prepared.

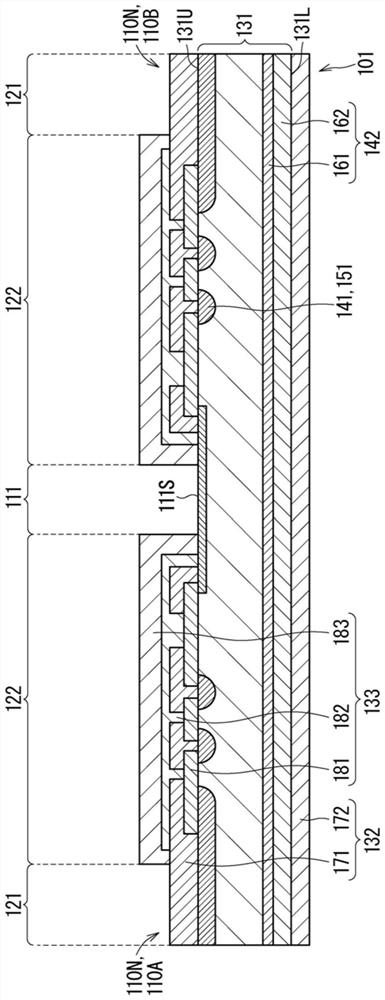

[0102] In addition, impurities are implanted into the prepared semiconductor wafer, and the prepared semiconductor wafer is heated. As a result, the p-type diffusion layer 141 and the n-type diffusion layer 142 are formed on the semiconductor wafer to obtain image 3 A semiconductor wafer 131 is shown.

[0103] In addition, electrodes 132 and an insulating layer 133 are formed on the obtained semiconductor wafer 131 . From this, get image 3 A semiconductor substrate 101 is shown.

[0104] The obtained semiconductor substrate 101 has a plurality of semiconduct...

PUM

| Property | Measurement | Unit |

|---|---|---|

| glass transition temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More