HJT battery with high photoelectric conversion efficiency and preparation method thereof

A technology for photoelectric conversion efficiency and battery, applied in the field of solar cells, can solve problems such as affecting the quality of the intrinsic layer of amorphous silicon and reducing the open circuit voltage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

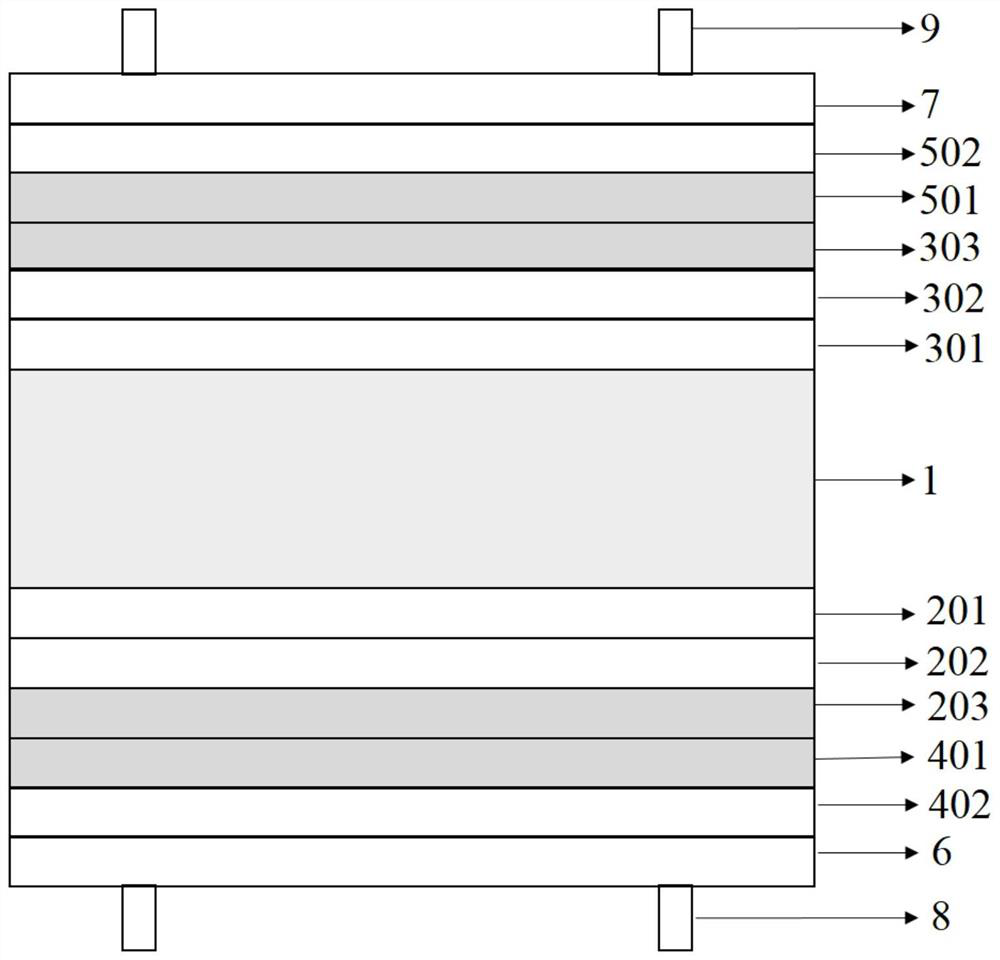

[0038] to combine figure 1 , a kind of high photoelectric conversion efficiency HJT cell of the present embodiment comprises N-type crystalline silicon chip 1, and the front of described N-type crystalline silicon chip 1 is provided with intrinsic amorphous silicon layer 301, SiO 2 Layer 302, C doped SiO 2 layer 303, an amorphous silicon doped N-type layer, a TCO conductive layer 7 and an electrode 9; the back of the N-type crystalline silicon wafer 1 is sequentially provided with an intrinsic amorphous silicon layer 201, SiO 2 Layer 202, C doped SiO 2 layer 203 , amorphous silicon doped P-type layer, TCO conductive layer 6 and electrode 8 . in:

[0039] The thickness of the intrinsic amorphous silicon layer is 3nm.

[0040] The SiO 2 layer and C-doped SiO 2 The thickness of each layer was 1 nm.

[0041] The thickness of the amorphous silicon-doped P-type layer is 10 nm, the thickness of the amorphous silicon-doped N-type layer is 10 nm; the thickness of the TCO conduct...

Embodiment 2

[0044] A HJT battery with high photoelectric conversion efficiency in this embodiment is basically the same as that in Embodiment 1, except that the thickness of the intrinsic amorphous silicon layer is 10 nm.

[0045] The SiO 2 layer and C-doped SiO 2 The thicknesses of the layers were all 5 nm.

[0046] The thickness of the amorphous silicon-doped P-type layer is 30nm, the thickness of the amorphous silicon-doped N-type layer is 30nm; the thickness of the TCO conductive layer is 110nm.

Embodiment 3

[0048] A HJT battery with high photoelectric conversion efficiency in this embodiment is basically the same as that in Embodiment 1, except that the thickness of the intrinsic amorphous silicon layer is 5 nm.

[0049] The SiO 2 Layer thickness 3nm, C-doped SiO 2 The thickness of the layer is 4 nm.

[0050] The thickness of the amorphous silicon-doped P-type layer is 20nm, the thickness of the amorphous silicon-doped N-type layer is 25nm; the thickness of the TCO conductive layer is 100nm.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More