A high-speed burst signal synchronization and equalization device and method

A burst signal, equalization device technology, applied in the field of optical access, to achieve high equalization and peak/valley detection efficiency, ensure payload bandwidth, and improve the effect of quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

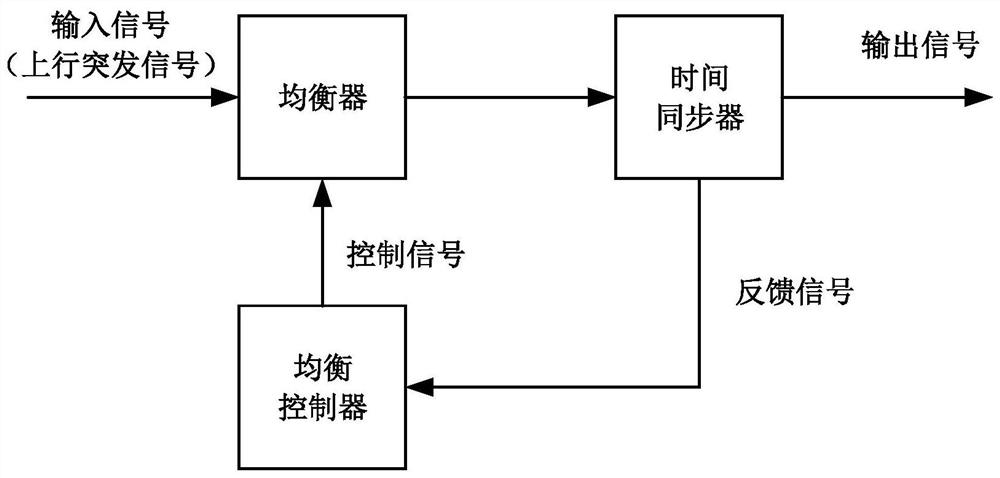

[0058] see figure 2 As shown, this embodiment provides a high-speed burst signal synchronization and equalization device, including an equalizer, a time synchronizer and an equalization controller.

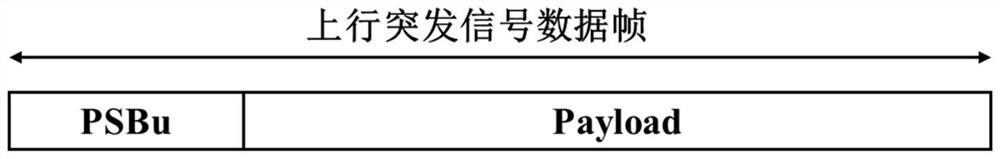

[0059] Wherein, the equalizer is used to: receive the uplink burst signal, and under the control of the equalization controller, transmit the calculated equalized output to the time synchronizer in the blind equalization mode or the training equalization mode; wherein, the uplink burst The signaled PSBu data pattern includes two parts, A+ and A-, and A+ and A- are negatively correlated. For example, taking the 32-bit PSBu data mode as an example, if the A+ part is expressed in binary as: [1,1,-1,1,-1,-1,1,-1,1,1,1,- 1,1,1,1,-1], then the A-part is expressed in binary as: [-1,-1,1,-1,1,1,-1,1,-1,-1,-1 ,1,-1,-1,-1,1]. It can be understood that the PSBu data pattern designed above has good autocorrelation characteristics, which is convenient for the time synchronizer to effective...

Embodiment 2

[0085] A high-speed burst signal synchronization and equalization device provided by this embodiment has the same basic structure as that of Embodiment 1, the difference being that this embodiment takes the 32-bit PSBu data mode as an example, as shown in Table 1. The A+ part of the PSBu data pattern is preferably expressed in binary as: [1,1,-1,1,-1,-1,1,-1,1,1,1,-1,1,1,1,- 1], then the A-part is preferably expressed in binary as: [-1,-1,1,-1,1,1,-1,1,-1,-1,-1,1,-1,-1 ,-1,1].

[0086] Table 1: 32-bit PSBu data pattern

[0087] Inx 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 bit 1 1 -1 1 -1 -1 1 -1 1 1 1 -1 1 1 1 -1 Inx 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 bit -1 -1 1 -1 1 1 -1 1 -1 -1 -1 1 -1 -1 -1 1

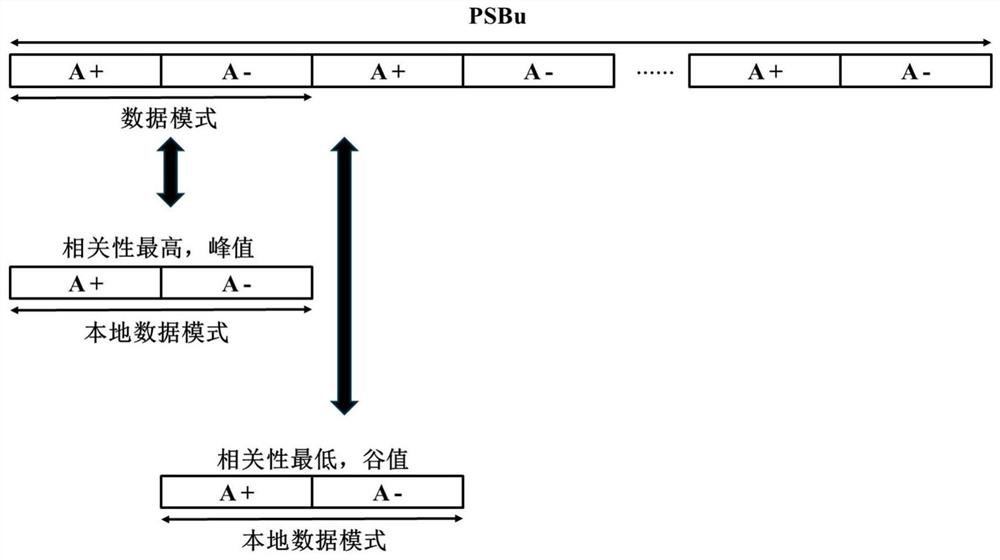

[0088] Based on the 32-bit PSBu data pattern in above-mentioned table 1, construct PSBu and local data pattern (refer to image 3 shown), and then carry out a correlation opera...

Embodiment 3

[0091] A high-speed burst signal synchronization and equalization device provided by this embodiment has the same basic structure as Embodiment 1, the difference is that this embodiment takes the 64-bit PSBu data mode as an example, as shown in Table 2, The A+ part of the PSBu data pattern is preferably expressed in binary as: [1,-1,1,-1,-1,-1,1,1,-1,1,1,1,-1,-1,1 ,1,1,1,-1,-1,1,-1,1,1,-1,-1,1,-1,1,-1,-1,-1], then A-part is preferred Expressed in binary as: [-1,1,-1,1,1,1,-1,-1,1,-1,-1,-1,1,1,-1,-1,-1, -1,1,1,-1,1,-1,-1,1,1,-1,1,-1,1,1,1].

[0092]Table 2: 64-bit PSBu data pattern

[0093] Inx 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 bit 1 -1 1 -1 -1 -1 1 1 -1 1 1 1 -1 -1 1 1 Inx 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 bit 1 1 -1 -1 1 -1 1 1 -1 -1 1 -1 1 -1 -1 -1 Inx 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 bit -1 1 -1 1 1 1 -1 -1 1 -1 -1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More