Graphical secondary development method of eda software in chip layout design

A layout design and secondary development technology, applied in CAD circuit design, visual/graphic programming, computer-aided design, etc., to achieve the effect of speeding up, improving flexibility, and reducing operation complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The specific implementation of the present invention will be described in further detail below in conjunction with the accompanying drawings of the embodiments, so as to make the technical solution of the present invention easier to understand and grasp, so as to define the protection scope of the present invention more clearly.

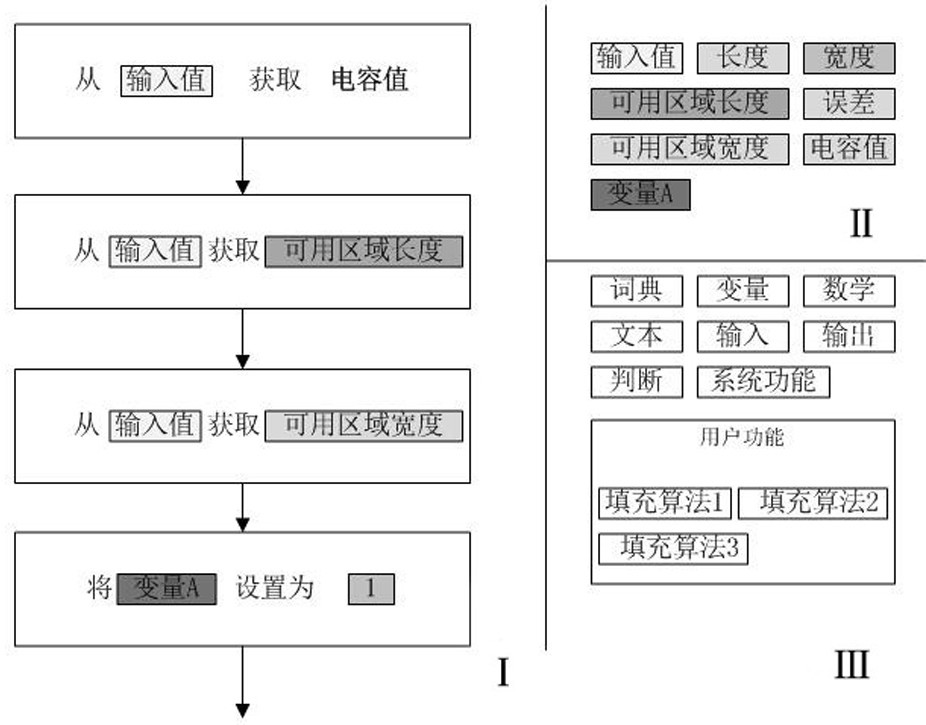

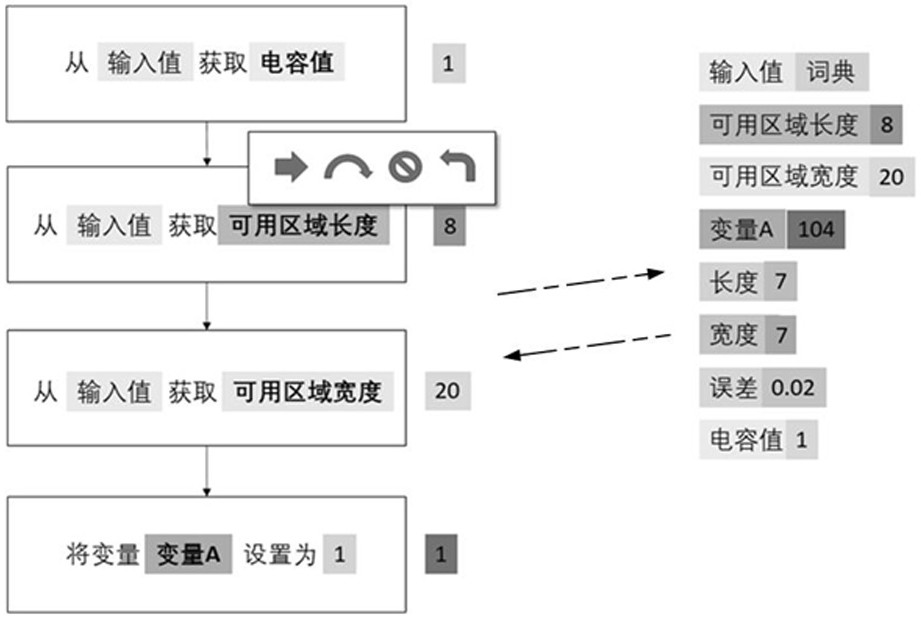

[0018] Aiming at many existing deficiencies, the designer of the present invention relies on long-term experience in chip design such as analog integrated circuits, and innovatively proposes a graphical secondary development method of EDA software in chip layout design, which is vivid, specific, and visualized. And the logical graphic editing method replaces the simple text input and editing in the past, and solves the problem of easy-to-use operation and optimized efficiency of chip layout design.

[0019] The above-mentioned graphical secondary development method of the present invention is implemented based on the system function call provid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More