Patents

Literature

147 results about "Graph design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

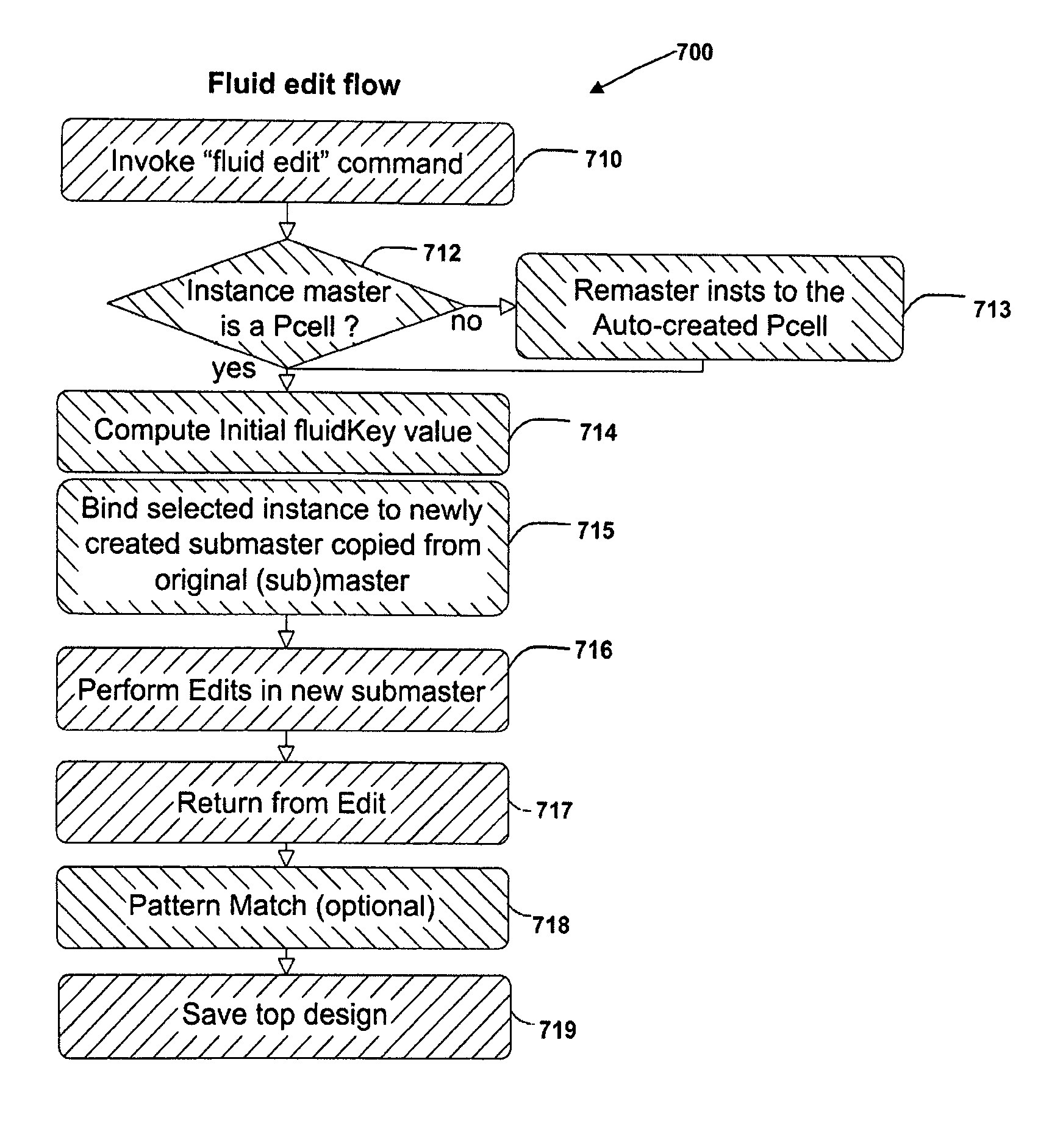

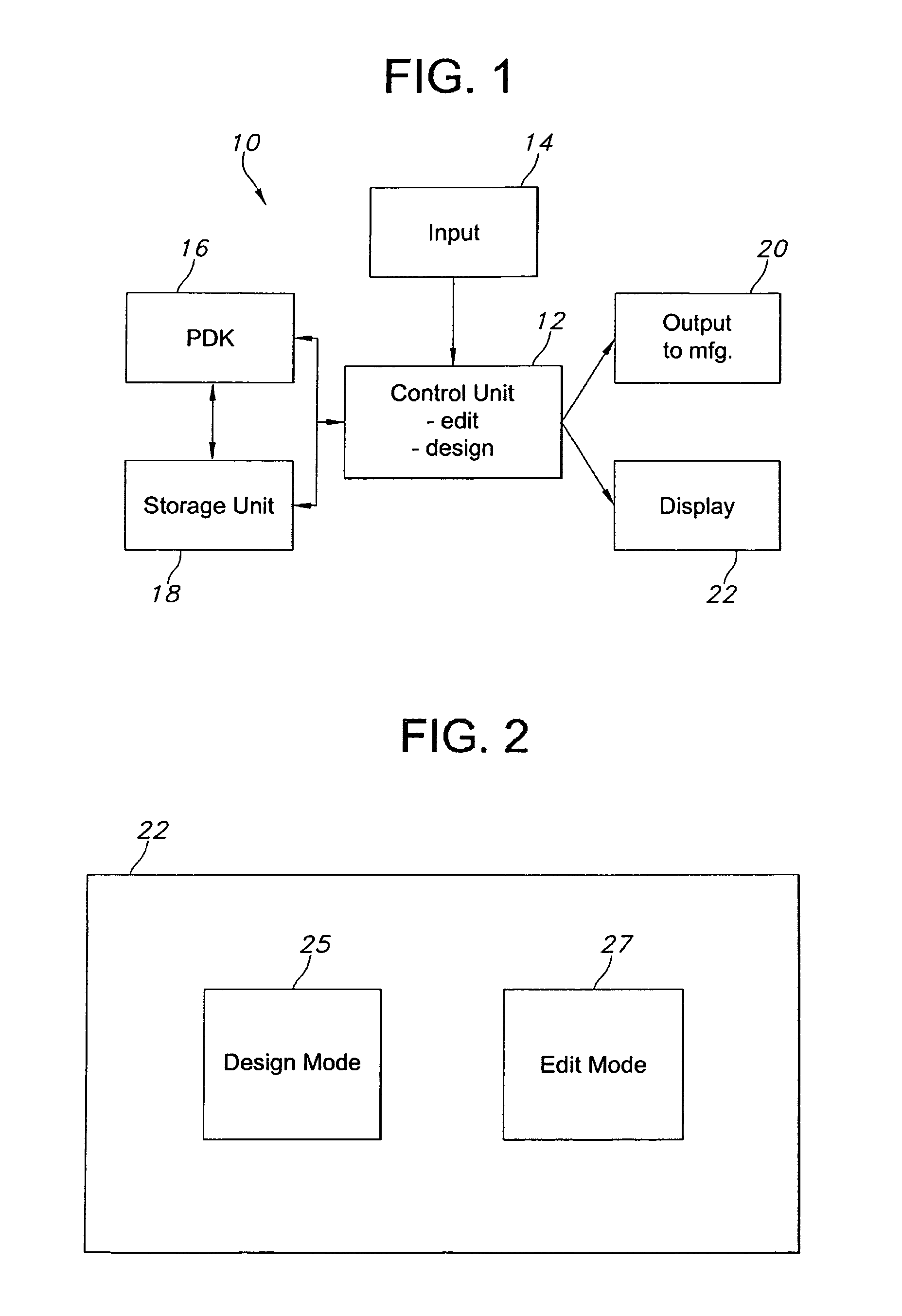

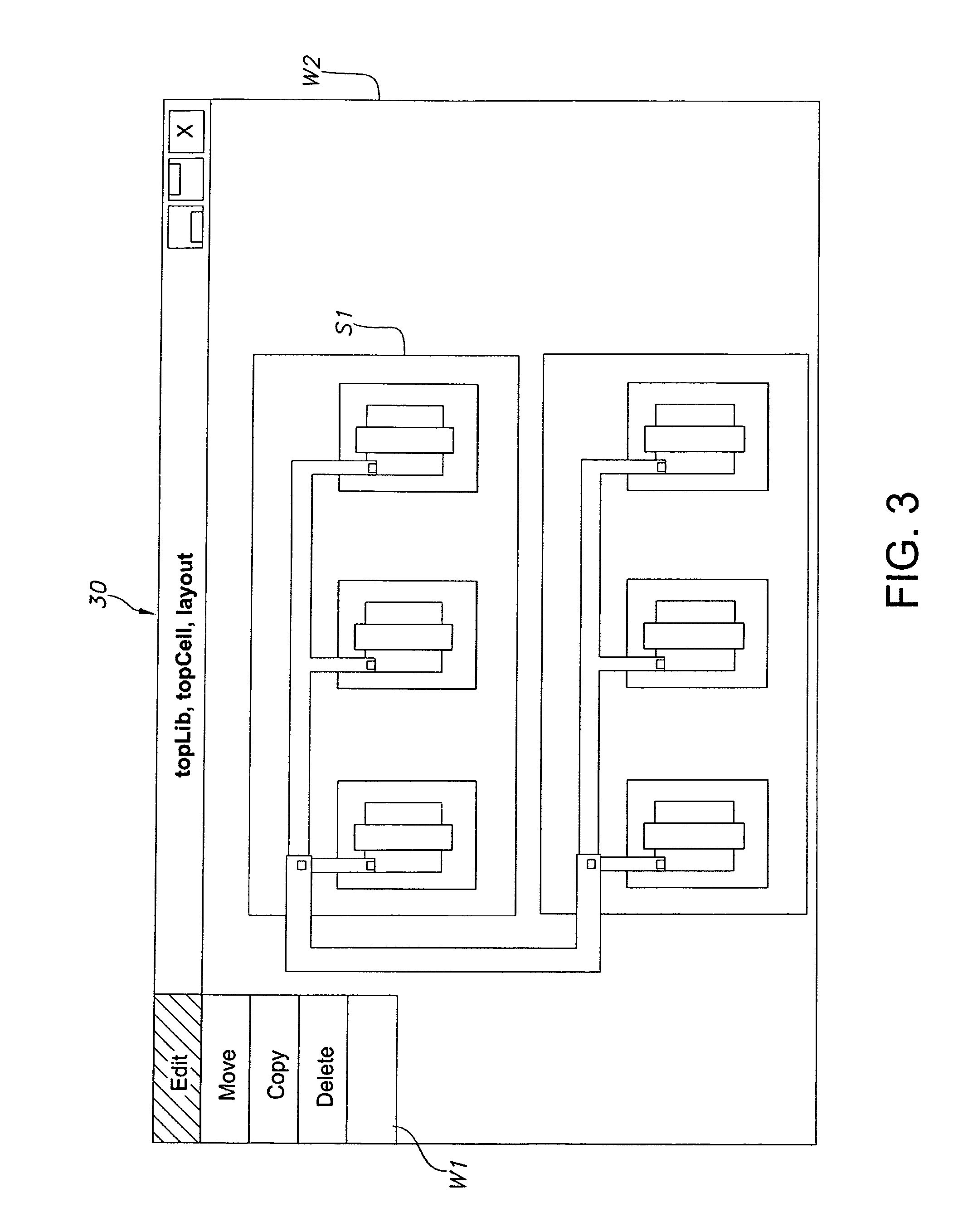

Systems and methods of editing cells of an electronic circuit design

InactiveUS8046730B1Computer programmed simultaneously with data introductionCAD circuit designComputer architectureElectronic circuit design

Systems and methods to enable a user to edit subMaster content of selected instances of an electronic layout design, including editing the contents of selected instances of an existing subMaster of an EDA design, generating a new subMaster to incorporate the modified contents of the selected instances, and binding the new subMaster to the selected instances without losing the design hierarchy of the layout design.

Owner:CADENCE DESIGN SYST INC

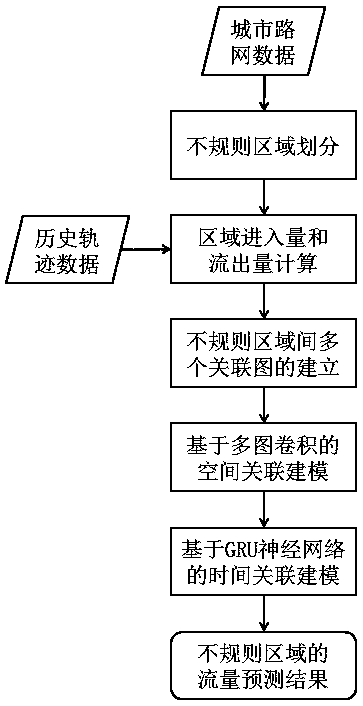

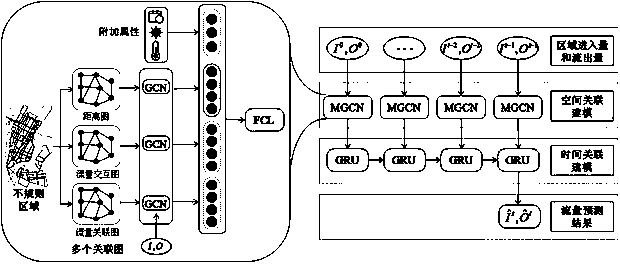

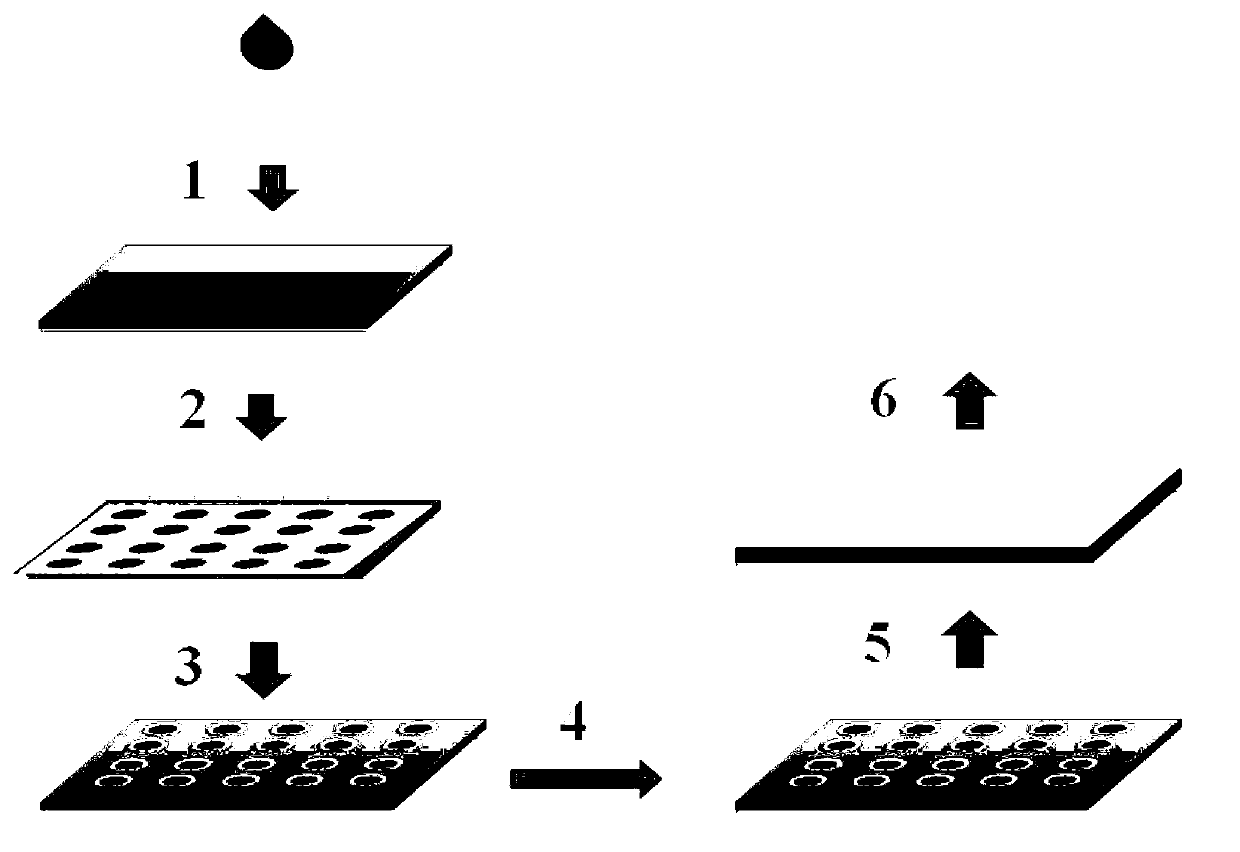

Irregular region flow prediction method based on multi-graph convolution and GRU

ActiveCN110991713AImprove practicalityImprove forecast accuracyForecastingCharacter and pattern recognitionAlgorithmNeural network nn

The invention discloses an irregular region flow prediction method based on multi-graph convolution and GRU. The method comprises the following steps: 1, dividing a region into N disconnected irregular regions; 2, performing space-time simplification on historical trajectory data, and performing calculating to obtain the inflow and outflow of all regions under each time step; 3, establishing a plurality of association graphs among the regions, constructing a corresponding adjacent matrix, and representing diversified spatial associations among the irregular regions; 4, designing a multi-graphconvolution neural network based on the association graph between the regions, and fusing the diversified spatial association features between the regions to obtain a multi-graph convolution fusion result; 5, capturing time correlation by adopting a GRU neural network based on a multi-graph convolution fusion result; 6, selecting a proper loss function, performing training to obtain a prediction model, and predicting through the prediction model to obtain the inflow amount and the outflow amount of each region.

Owner:HANGZHOU DIANZI UNIV

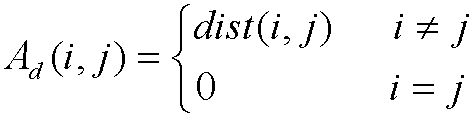

Simple preparation method and application of polydimethylsiloxane (PDMS) polymer microlens array

ActiveCN102967890AEasy to operateReduce experiment costPhotomechanical exposure apparatusMicrolithography exposure apparatusPolymer scienceLithographic artist

The invention discloses a simple preparation method and an application of a polydimethylsiloxane (PDMS) polymer microlens array. The preparation method comprises the following steps of: exposing a graph designed by a lithography method on an SU8 photoresist, developing the graph by employing a developing solution, and controlling the developing time, so that the unexposed SU8 photoresist part is removed; baking the unexposed SU8 photoresist part in an oven, so that the bottom is in an arc shape; taking the unexposed SU8 photoresist part out, cooling to room temperature, and performing secondary exposure, so that the SU8 is completely cured and is manufactured into a template for manufacturing a PDMS polymer lens; and pouring the non-cured PDMS polymer solution to the template, heating and curing the PDMS polymer solution, and stripping a PDMS chip to manufacture the PDMS polymer microlens array. The prepared PDMS can be applied to optical imaging; and the method is simply and rapidly operated, is low in experimental cost and can be integrated with other technologies.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

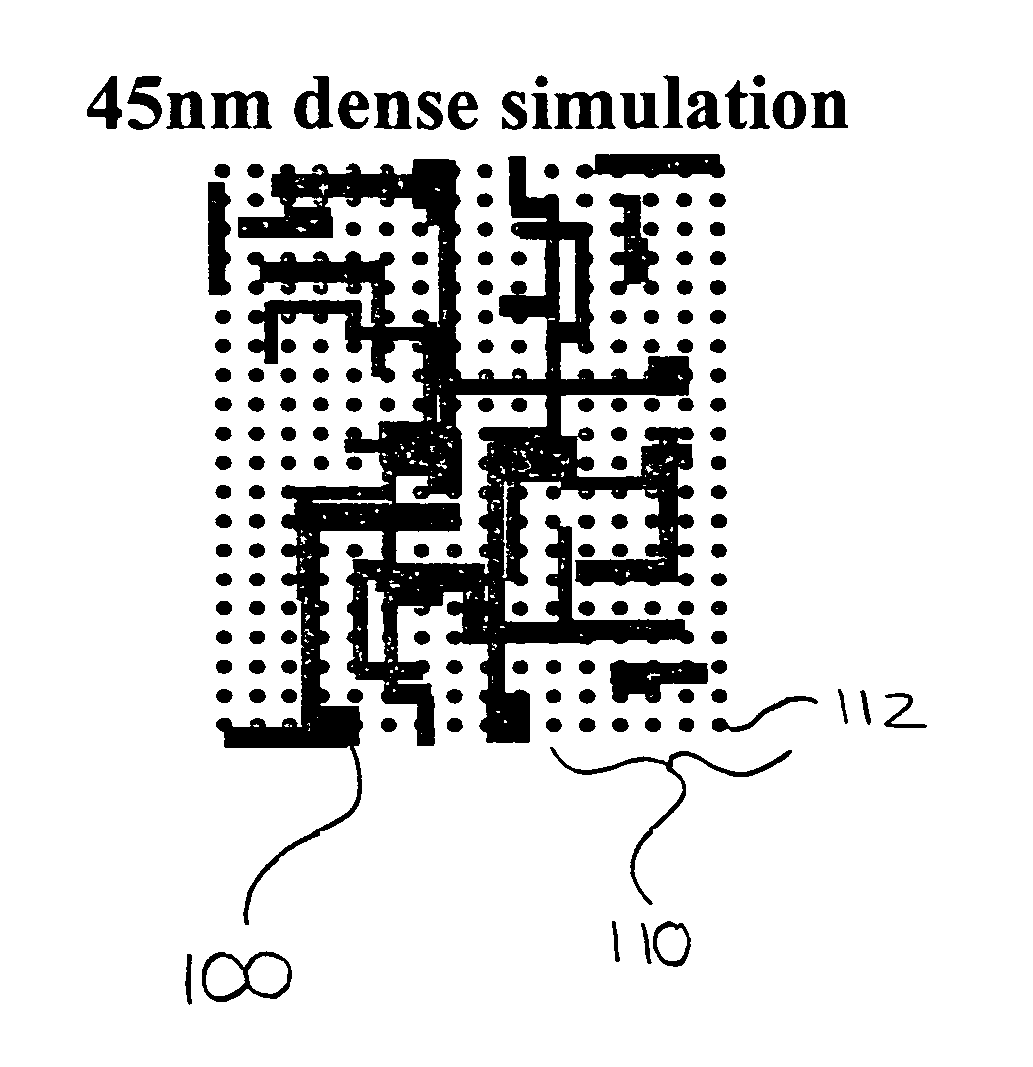

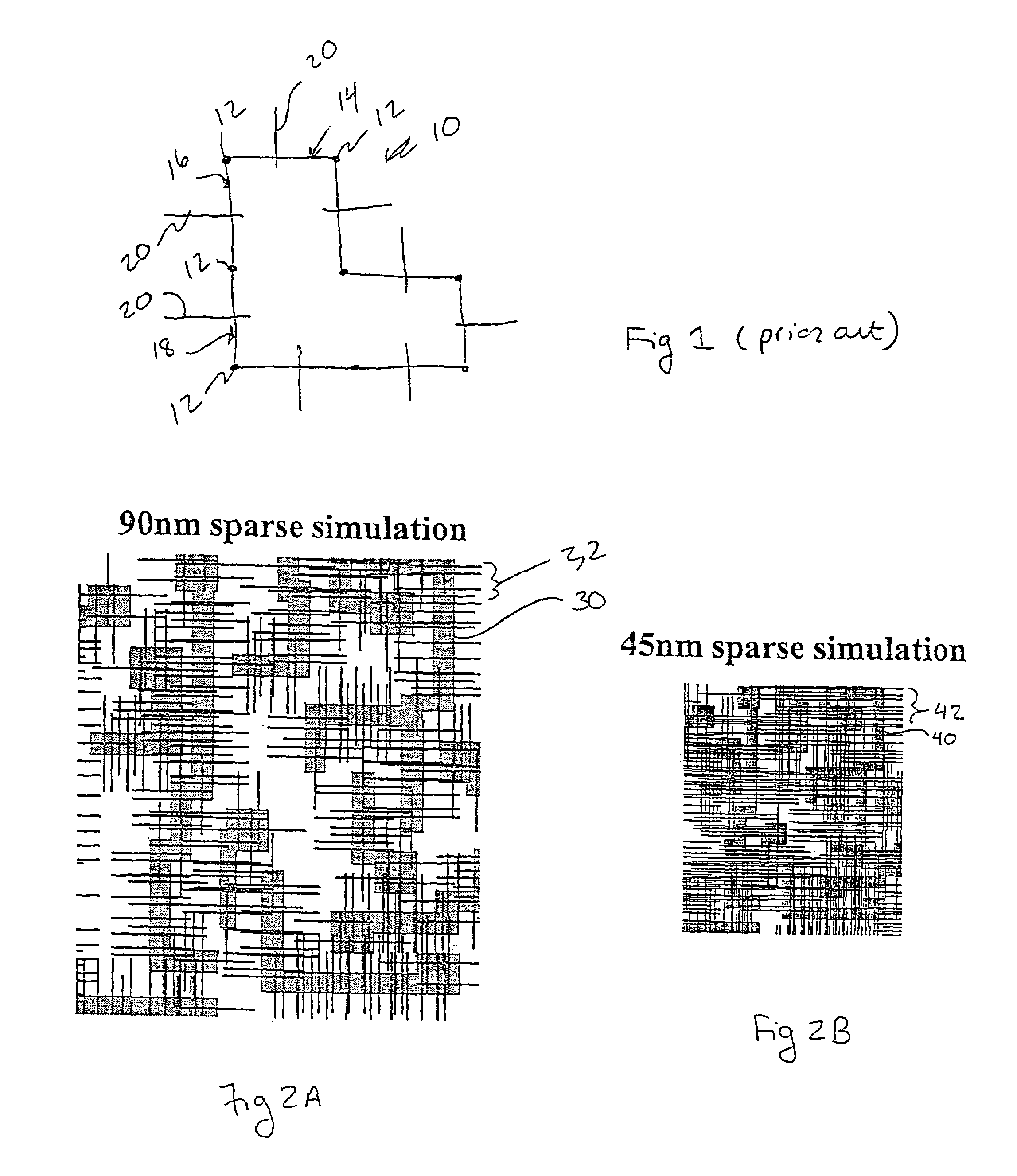

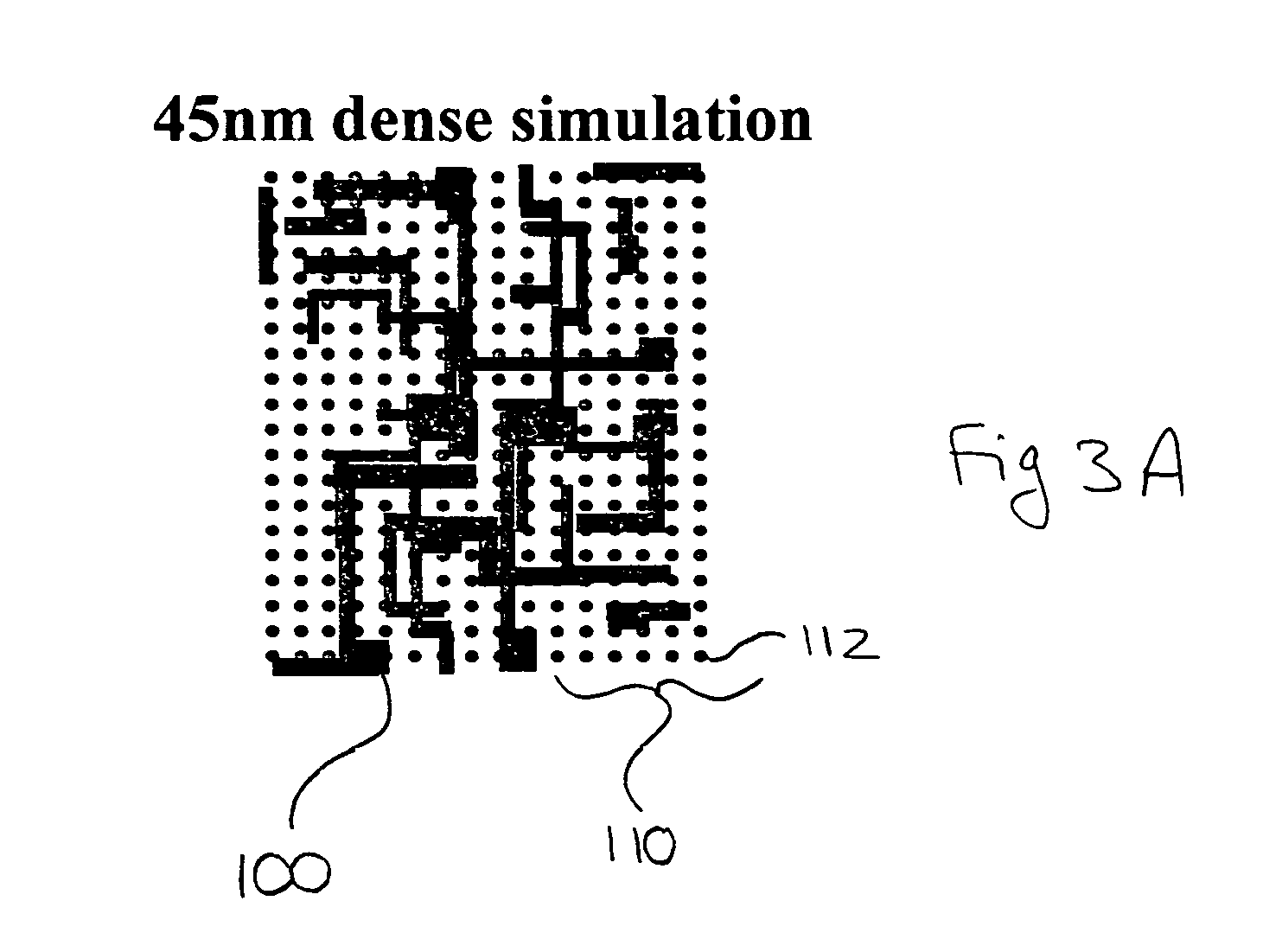

Dense OPC

ActiveUS7434199B2Photomechanical apparatusOriginals for photomechanical treatmentResolution enhancement technologiesAlgorithm

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

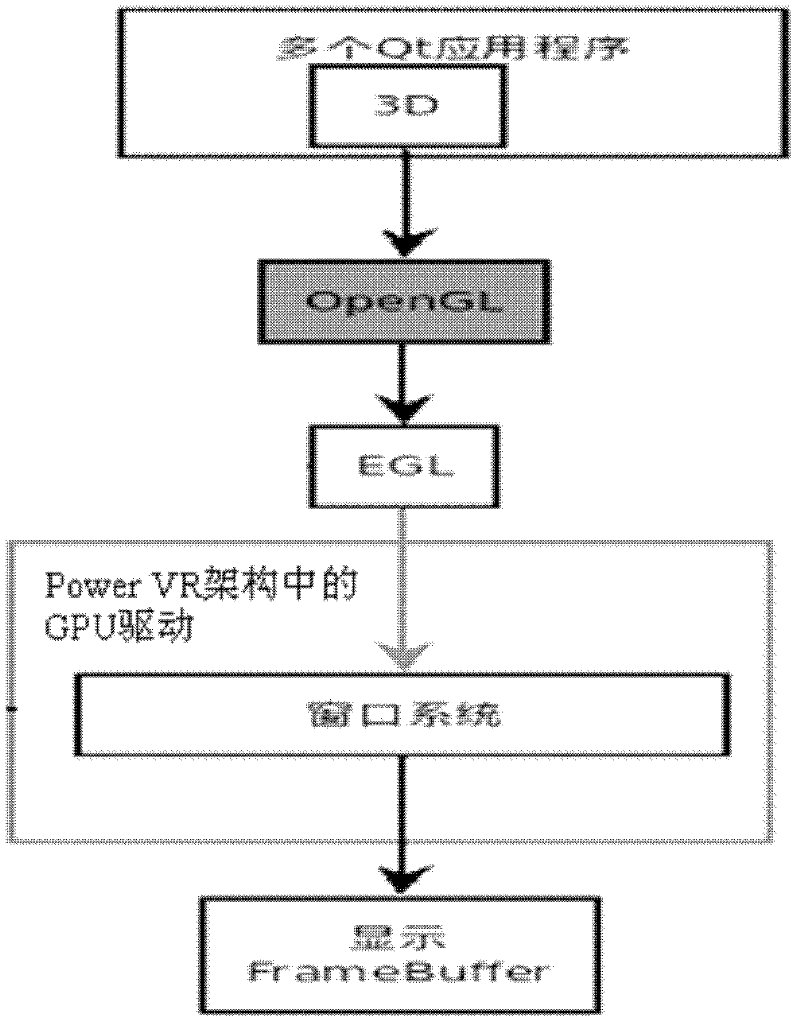

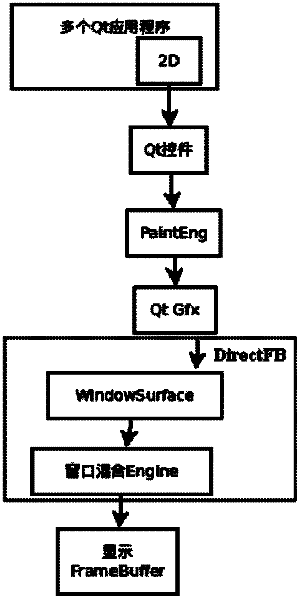

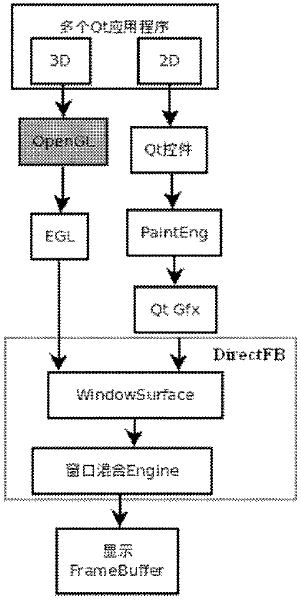

QT-based two-dimensional/three-dimensional (2D/3D) graph drawing method and device

InactiveCN102567025AAdd supportGuaranteed correctnessSpecific program execution arrangementsGraphicsGraphic card

The invention discloses a QT-based two-dimensional / three-dimensional (2D / 3D) graph drawing method and a QT-based 2D / 3D graph drawing device. The method comprises the following steps of: receiving a QT application, and performing corresponding processing according to an inherited object of the QT application; and establishing a corresponding application bottom layer according to the application type of the application, creating a corresponding window according to the application, and returning to a window handle, wherein the application type comprises 2D and 3D types. Support for OpenGL ES is increased in a mode of modifying QDirectFBScreen, and the correctness of drawing a 2D graph according to a principle can be ensured, so that research and development time is short, the design is simple, and a developer is not required to understand the writing mode of a graphics card driver. In addition, the graphics card driver can be written by a method provided by QT in spite of the 2D or 3D graph designed by a QT application layer.

Owner:SHENZHEN TCL NEW-TECH CO LTD

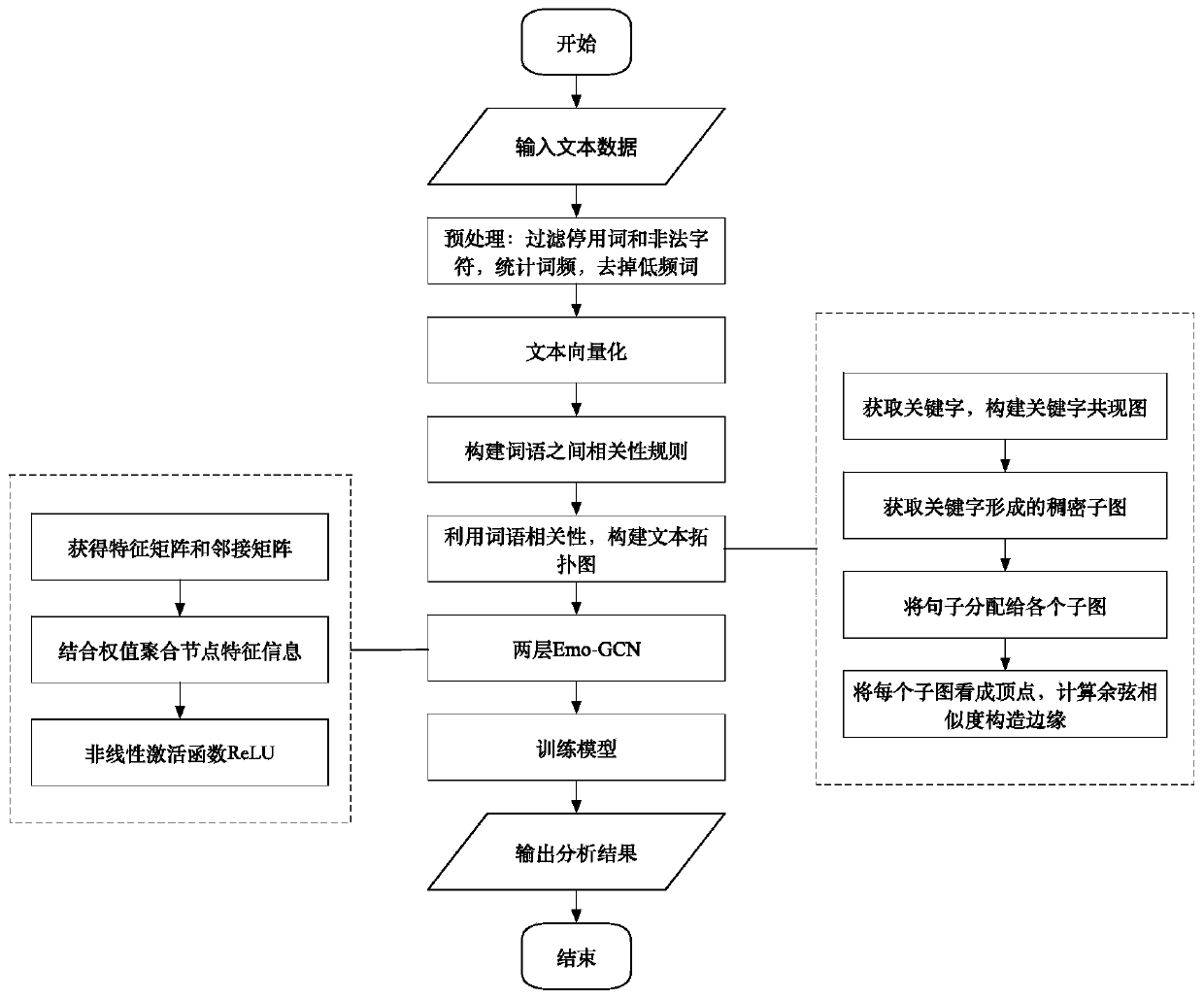

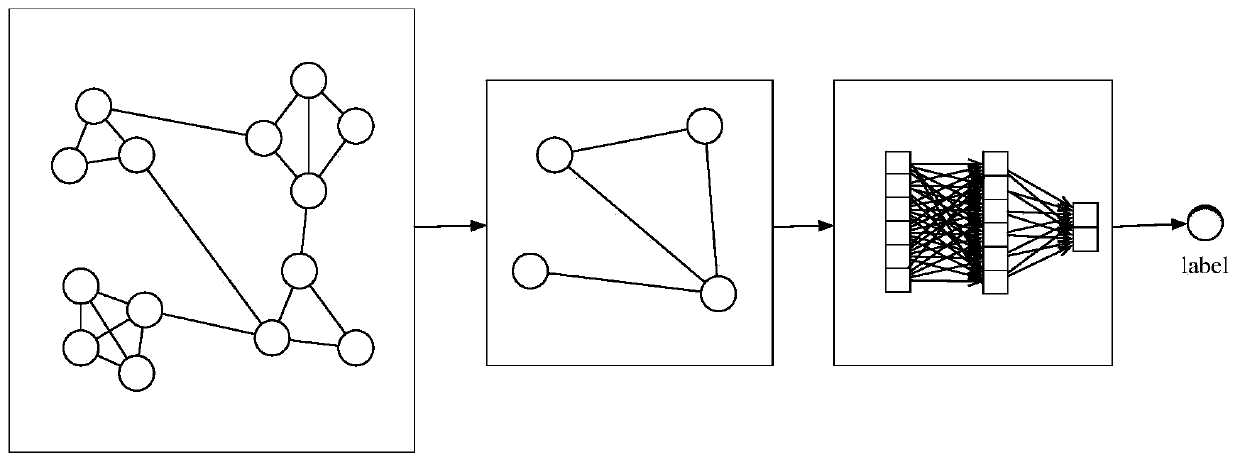

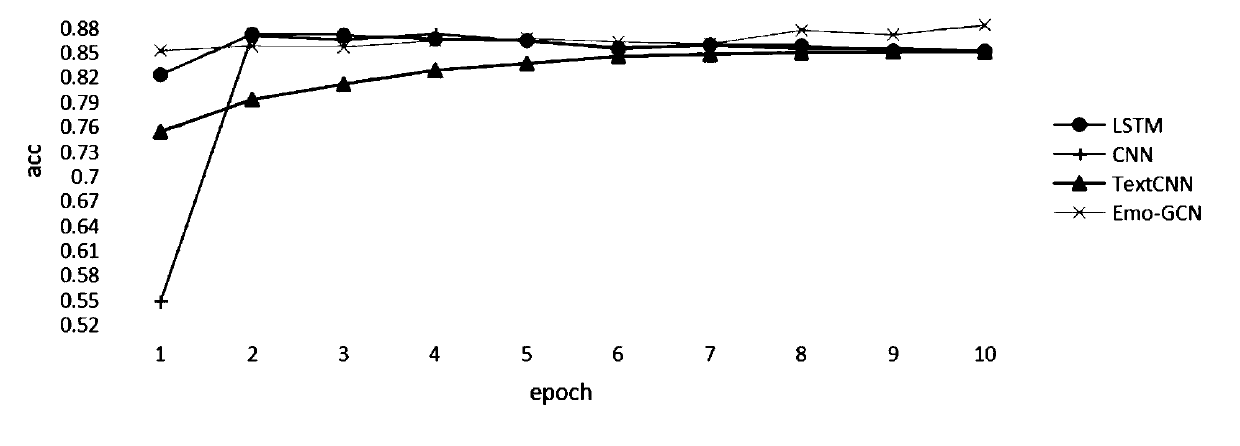

Text sentiment analysis method based on deep learning

ActiveCN110889282AThe analysis result is accurateBreak through limitationsNatural language data processingNeural architecturesAlgorithmTheoretical computer science

The invention provides a text sentiment analysis method based on deep learning. The method comprises the following steps: (1) inputting text data, removing stop words, and extracting keywords to forma keyword set; (2) forming a dense sub-graph by constructing a keyword co-occurrence graph; vector representations of sentences in the sub-graphs and the document are obtained, and then the sentencesare distributed to the sub-graphs; designing edge connection and edge weight between the sub-graphs to form topological interaction graph expression of the document; and (3) taking the topological interaction diagram as the input of an Emo-GCN model, carrying out node feature extraction transformation, and then fusing local structure information to obtain a node aggregation matrix. The nonlinear transformation is carried out on the aggregated information. The Emo-GCN model adopts a hierarchical structure, and the features are extracted layer by layer. According to the method, the novel topological interaction graph is adopted to express the text information, then the graph convolutional neural network is used for text sentiment analysis, and the method still has strong adaptability. The method is applied to product recommendation, market prediction and decision adjustment, and has extremely high commercial value.

Owner:HARBIN ENG UNIV

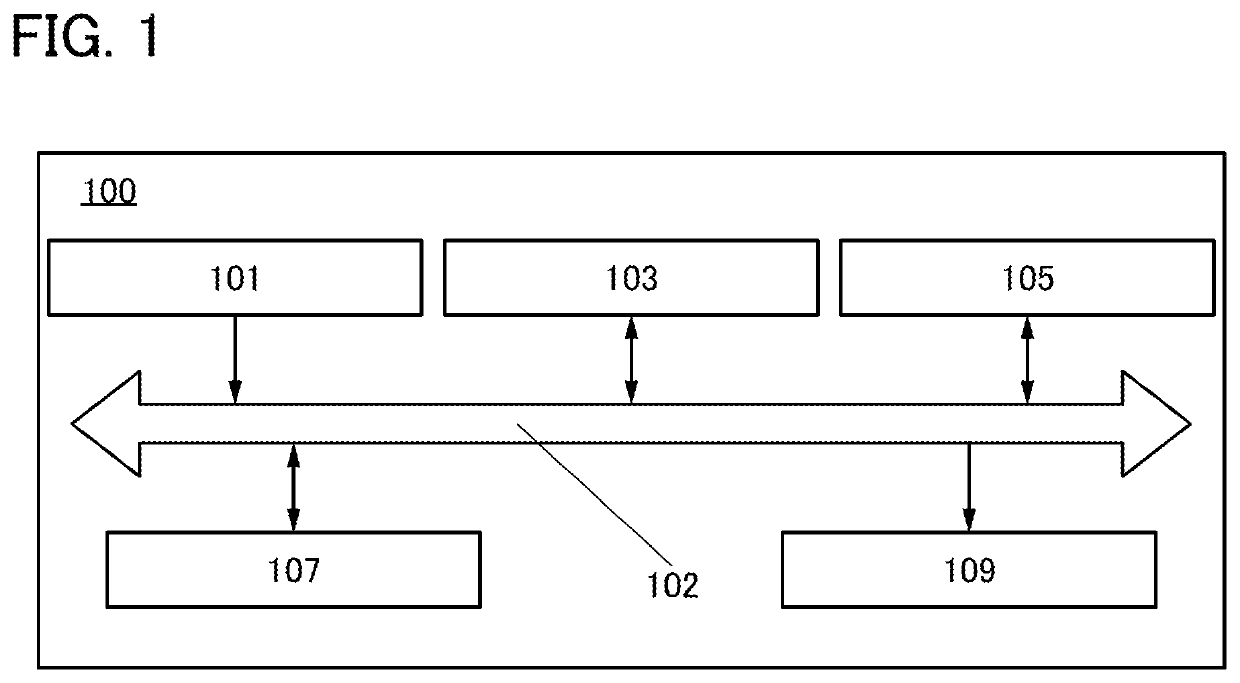

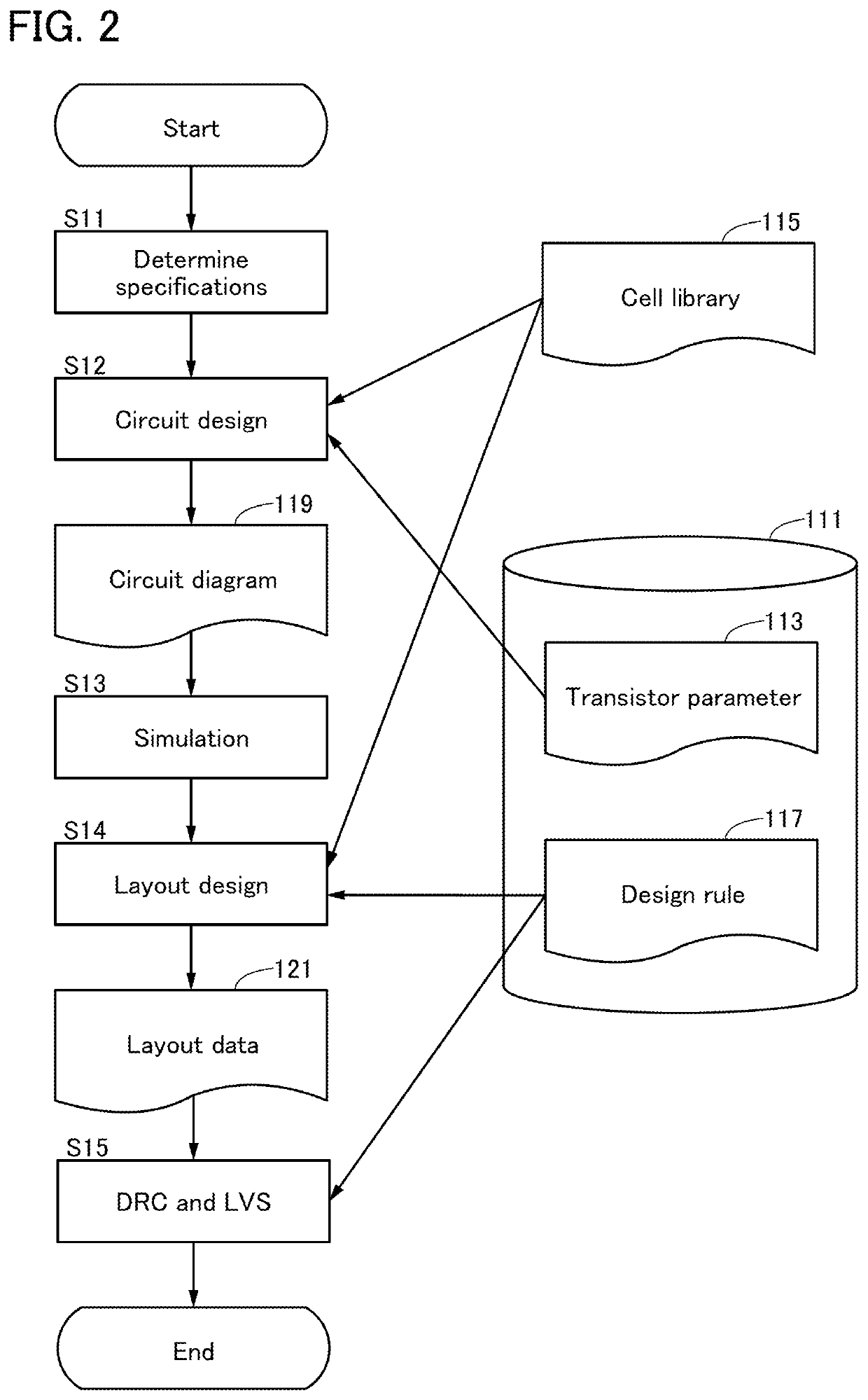

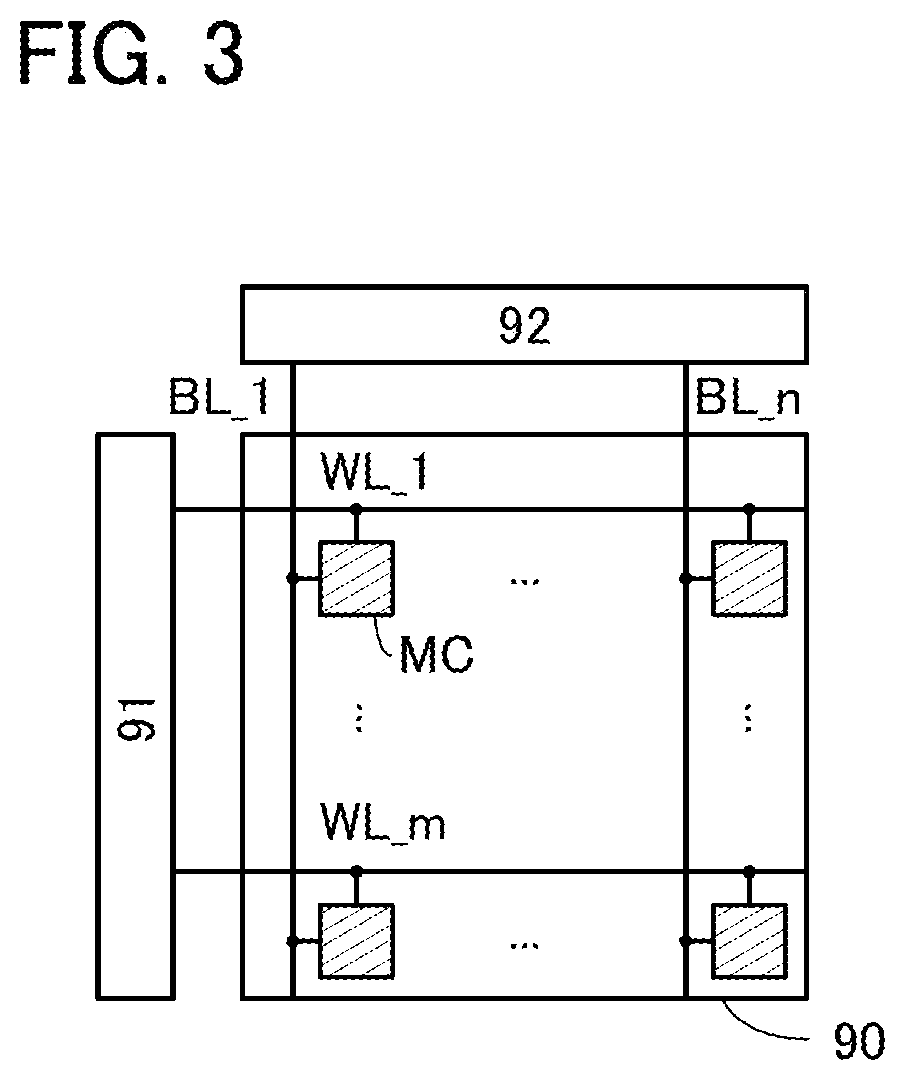

Layout design system and layout design method

ActiveUS20200184137A1Short timeReduce layout areaArtificial lifeDesign optimisation/simulationAlgorithmSoftware engineering

To perform layout design for a small area satisfying a design rule, within a short period of time. A layout design system which includes a processing portion and in which a circuit diagram and layout design information are input to the processing portion, the processing portion has a function of generating layout data from the circuit diagram and the layout design information by performing Q learning, the processing portion has a function of outputting the layout data, the processing portion includes a first neural network, and the first neural network estimates an action value function in the Q learning.

Owner:SEMICON ENERGY LAB CO LTD

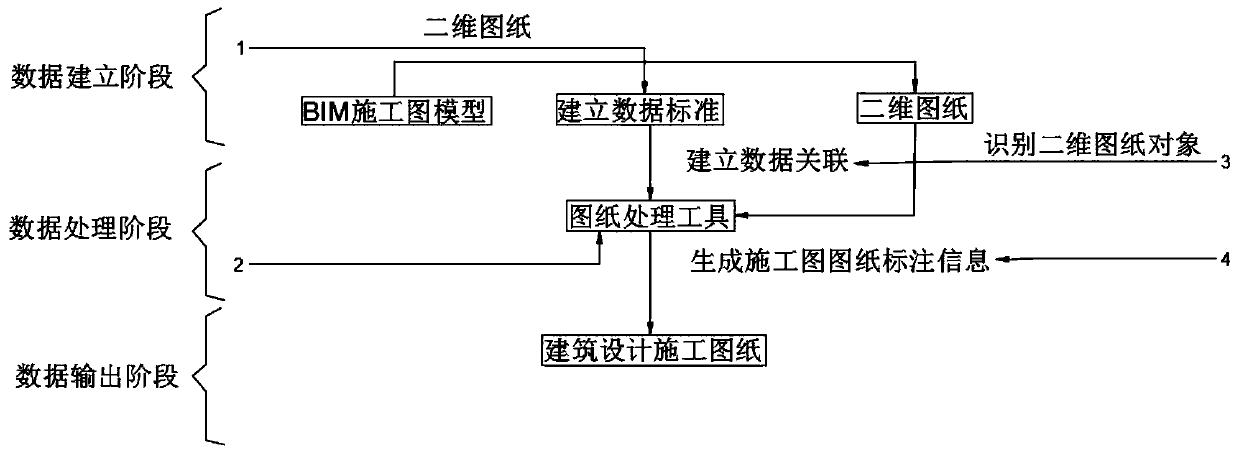

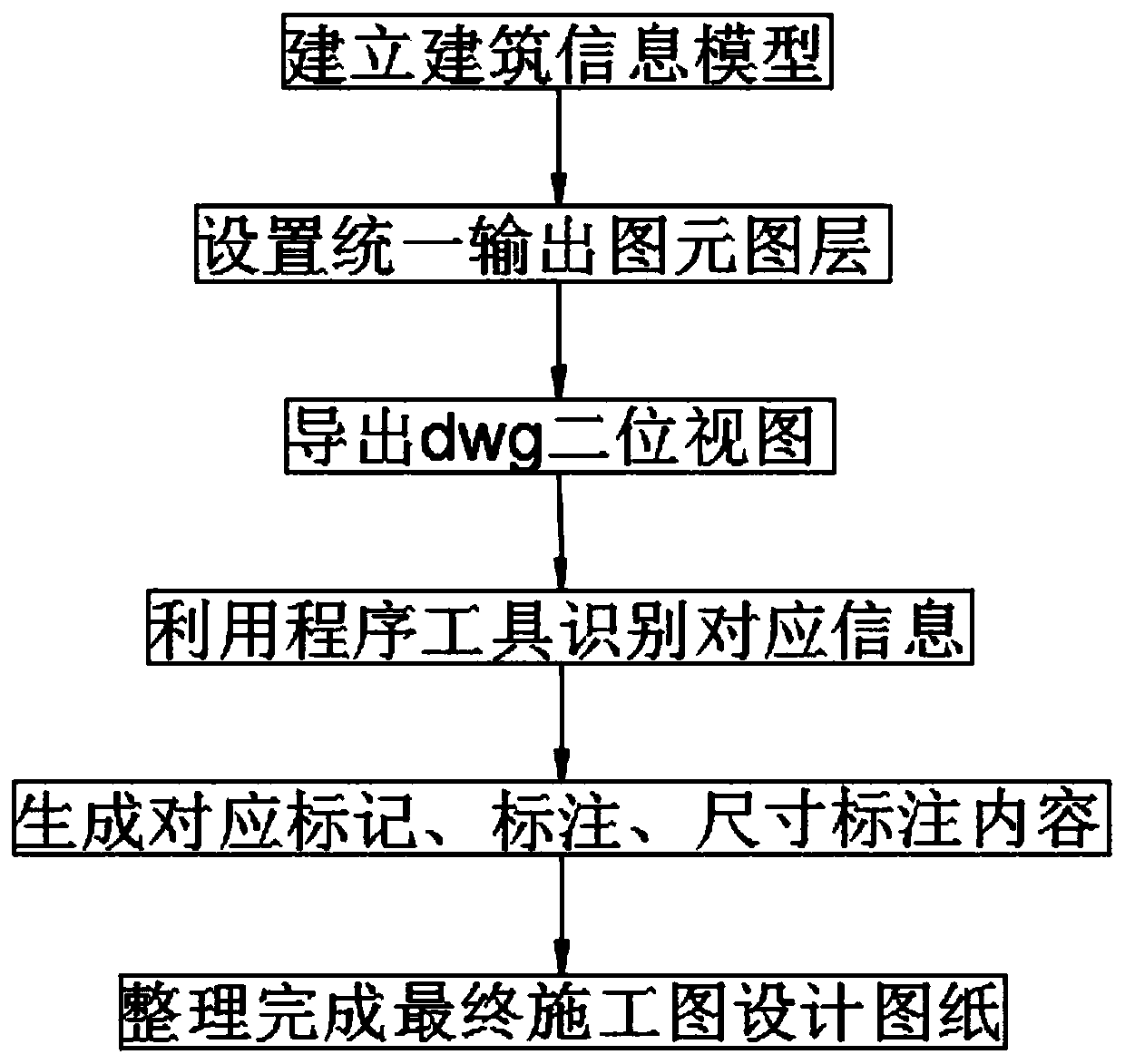

Architectural design drawing system based on BIM technology and drawing method thereof

PendingCN110765510AImprove design qualityImprove design efficiencyGeometric CADGraphicsEffective solution

The invention provides an architectural design drawing system and method based on a BIM technology. The architectural design drawing system and method combine achievements of a two-dimensional drawingprinciple and a three-dimensional building information model. The architectural design drawing method automatically identifies and generates the annotation content by utilizing the model information,so that the workload of repeated manual operation required by a traditional drawing method is reduced, and the originally manually drawn graph becomes uniform and neat. The architectural design drawing method also brings more possibility for the transformation from a traditional two-dimensional drawing platform to a three-dimensional drawing platform, and meanwhile, improves the production capacity of the design industry. According to the architectural design drawing method, unnecessary engineering rework is reduced for subsequent engineering, and the risks of construction period delay and cost waste are reduced, and meanwhile, an effective solution is provided for improving the design quality, optimizing the design scheme and improving the design efficiency in the design industry, and the technical defects in the BIM software and actual construction drawing design process are overcome.

Owner:CHONGQING ARCH AGE DESIGN

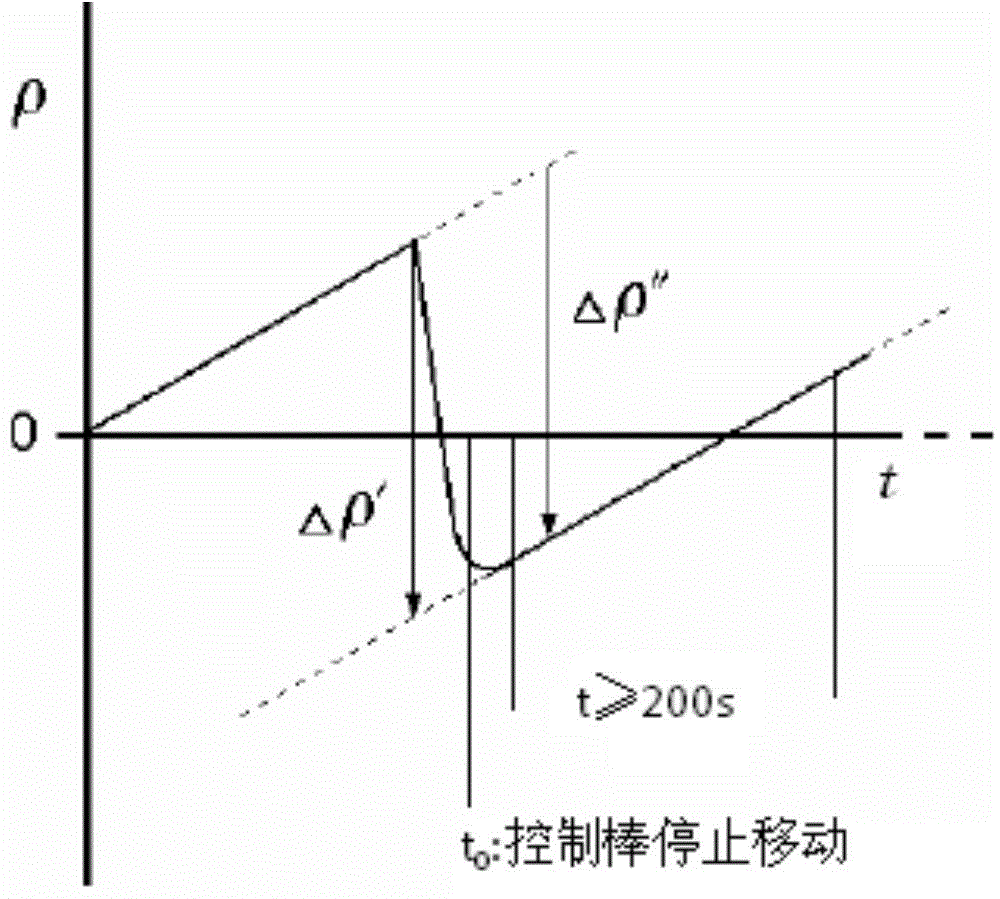

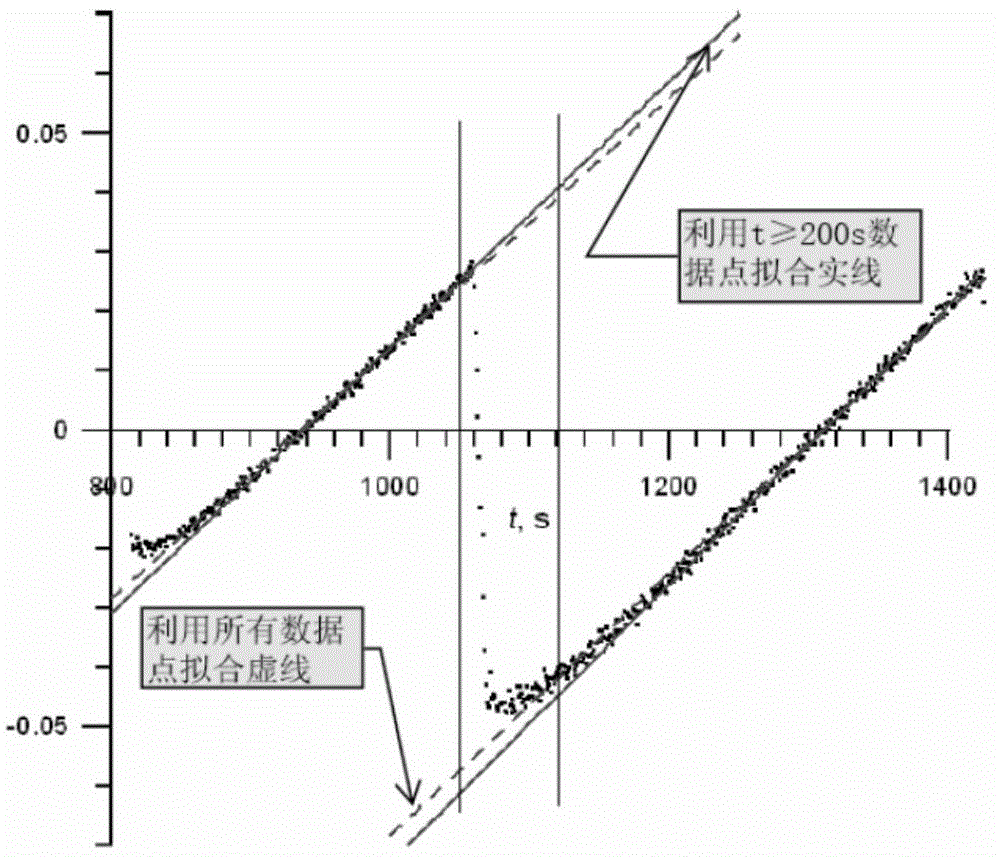

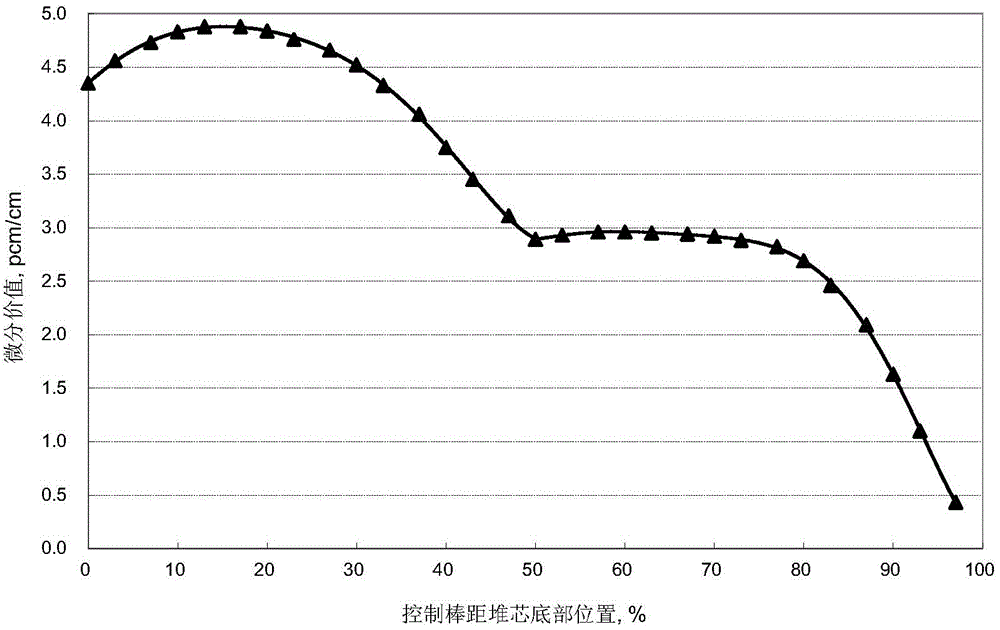

Data processing method for control rod calculus worth measurement test

ActiveCN104916337AReduce reactivity measurement errorHigh precisionNuclear energy generationNuclear monitoringMeasurement testMathematical Calculus

Belonging to the technical field of reactor startup test, the invention specifically relates to a data processing method for control rod calculus worth measurement test. The method includes the steps of: 1. conducting small flow injection of clear water or boric acid solution into a reactor core; 2. moving a control rod, and recording data points; 3. performing linear fitting of data points; 4. figuring out reactivity change; 5. working out reactivity differential worth and integral worth; 6. repeating step 2 to step 5; 7. graphing designed rod position and designed reactivity differential worth; 8. fitting the graph of step 5; and 9. comparing the measured value with a design value. The method reduces or even ignores the influence of spatial effect on the test result, reduces the error of reactivity measurement error, and improves the accuracy by about 5%. By means of unary sextic fitting, the error caused by traditional methods to measured value linear fitting is reduced, and the standard deviation is also reduced.

Owner:JIANGSU NUCLEAR POWER CORP

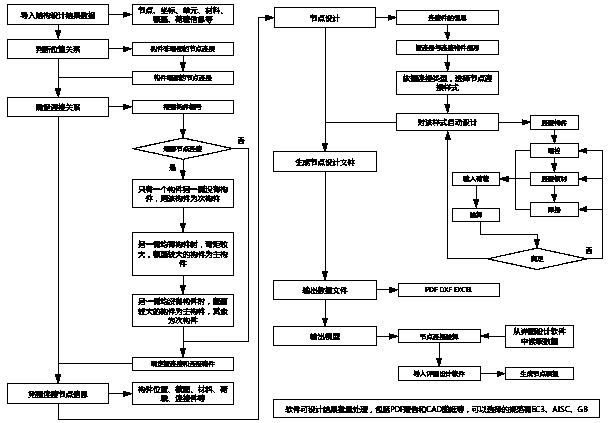

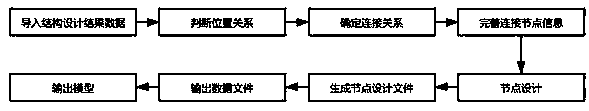

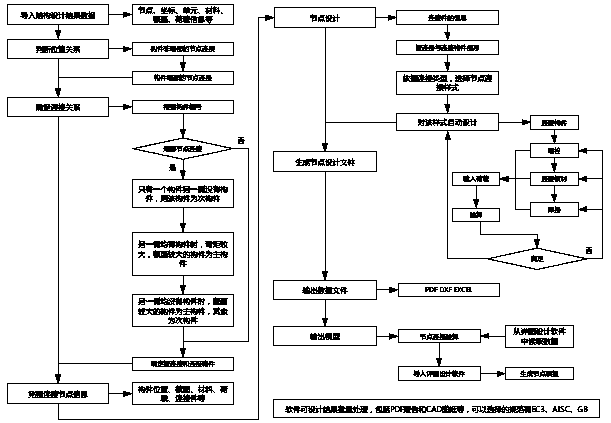

Steel structure node intelligent design method

ActiveCN109918860AShorten the construction periodRealize automatic generationSpecial data processing applicationsManufacturing computing systemsComponent LoadDesign software

The invention relates to the technical field of node design, and discloses a steel structure node intelligent design method, which comprises the following steps: importing structure design data: importing a structure design result as input data into node design software; and judging the position relation: combining units which are broken in the structural design stage according to the node number,the node coordinate information, the unit information, the component number, the component section and the component load information data, thereby combining the units to form a component, generatinga new component number, and carrying out attribute definition on the component to generate the position relation information. According to the steel structure node intelligent design method, an intelligent and automatic node design method is adopted, the whole process of intelligently judging a component relation, automatically selecting a node type, automatically designing, automatically drawingout, automatically generating a report and automatically importing a node model into commercial detail drawing software is achieved, and the relation between structural design and detail drawing design is established.

Owner:上海同煦工程咨询有限公司

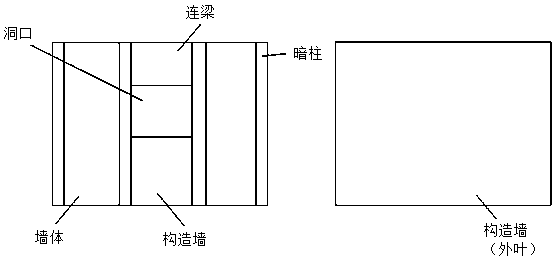

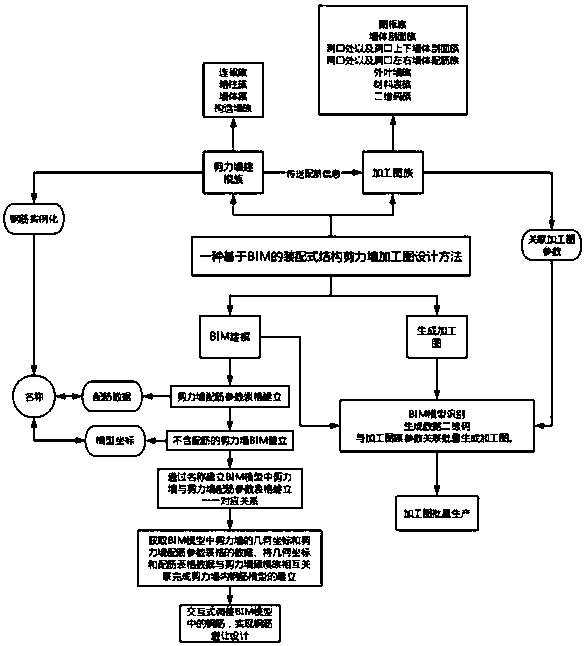

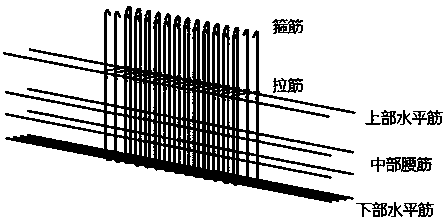

BIM-based fabricated structure shear wall machining drawing design method

The invention discloses a BIM-based fabricated structure shear wall machining drawing design method, and belongs to the technical field of intelligent buildings. The method mainly comprises a shear wall modeling family, a processing drawing family, BIM modeling and processing drawing generation. The modeling process comprises the following steps: establishing a shear wall reinforcement parameter table, building a shear wall BIM without reinforcing bars, building a one-to-one correspondence relationship between ashear wall and theshear wall reinforcing bar parameter table in the BIM model through names, obtaining geometric coordinates of the shear wall and data of the shear wall reinforcing bar parameter table in the BIM model, and correlating the geometric coordinates and the data of the reinforcing bar table with a shear wall modeling family; completing establishment of a steel bar model in the shear wall, interactively adjusting steel bars in the BIM model, and realizing steel bar avoidance design, wherein the step of generating the machining graph comprises BIM model recognition, data two-dimensional code generation and batch generation of the machining graph associated with themachining graph family parameters.

Owner:SHENYANG POLYTECHNIC UNIV +1

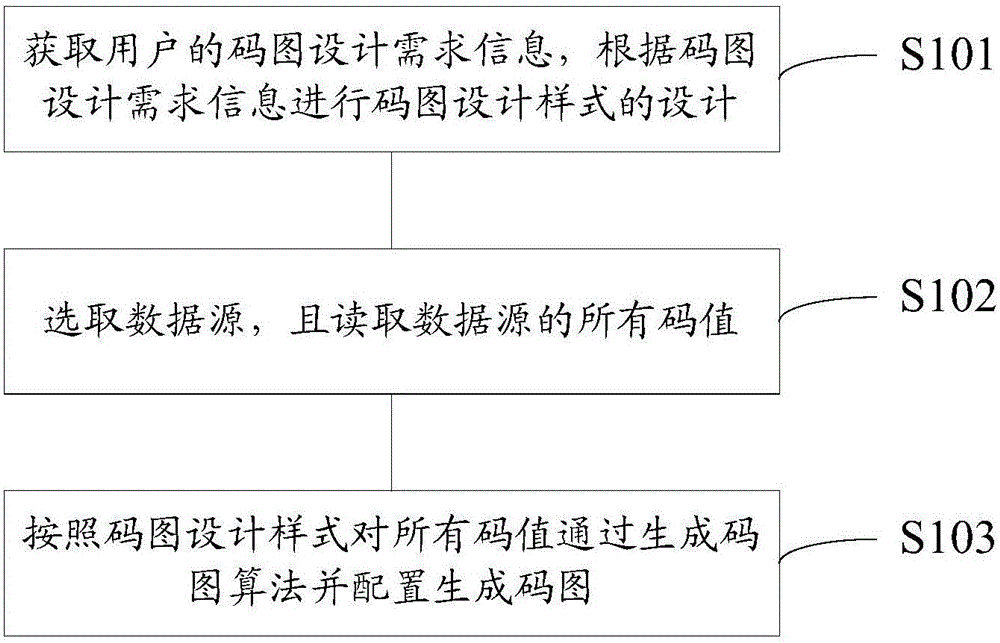

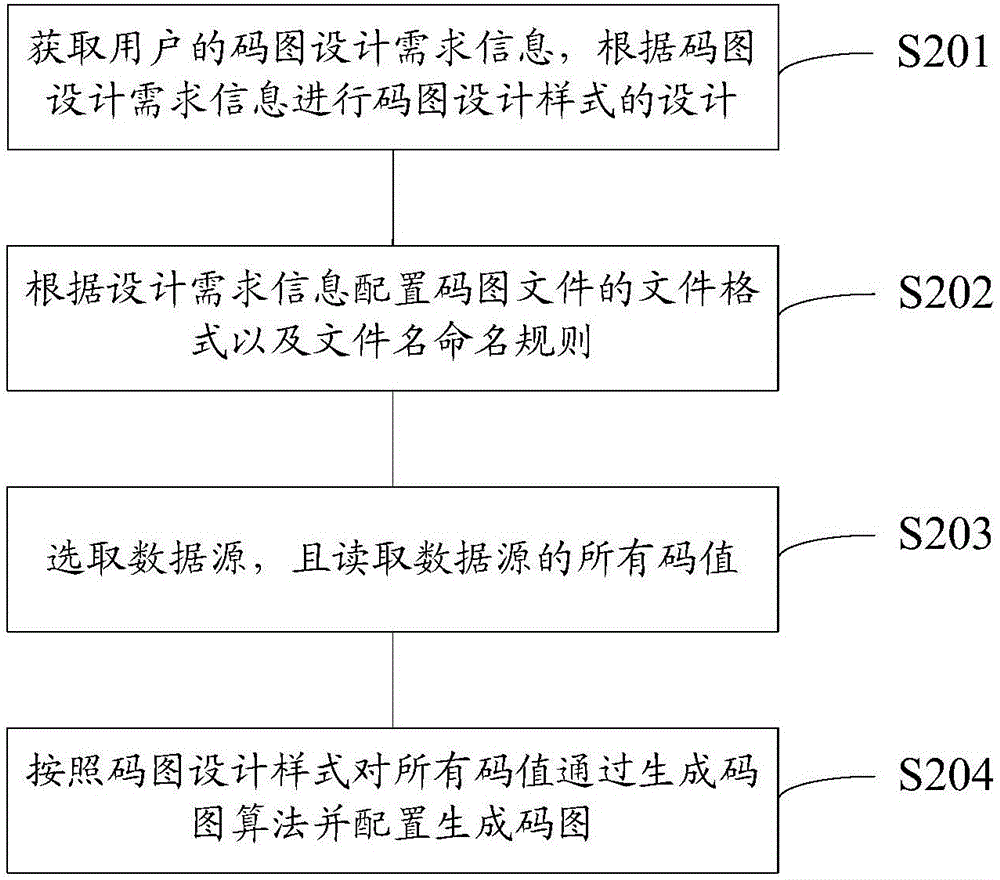

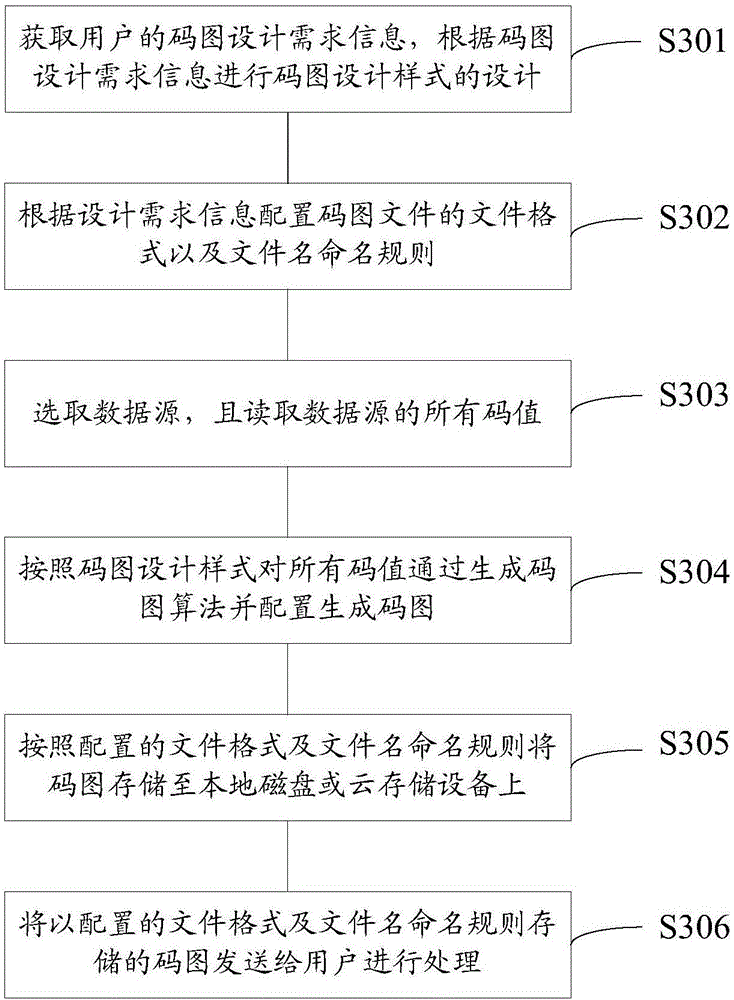

Code graph editing and generating method and system

The invention discloses a code graph editing and generating method and system. The method specifically comprises the following steps that: obtaining the code graph design requirement information of a user, and designing a code graph design style according to the code graph design requirement; selecting a data source, and reading all code values of the data source; and according to the code graph design style, generating code graph algorithms and configuring and generating the code graph for all code values according to the code graph design style. The source and the amount of the code values are strictly restricted and can not be tampered in a generation process, and the generated code graph is guaranteed to be legal and unique to realize the accuracy of one object with one code; and in addition, according to the design requirement information, the file format and the file name naming rule of a code graph file are configured, and different code graphs can be generated according to different coding positions, different coding types, different code graph formats and different naming rules for a printing press to carry out jet printing.

Owner:BEIJING VISION BRILLIANCE TECH CO LTD

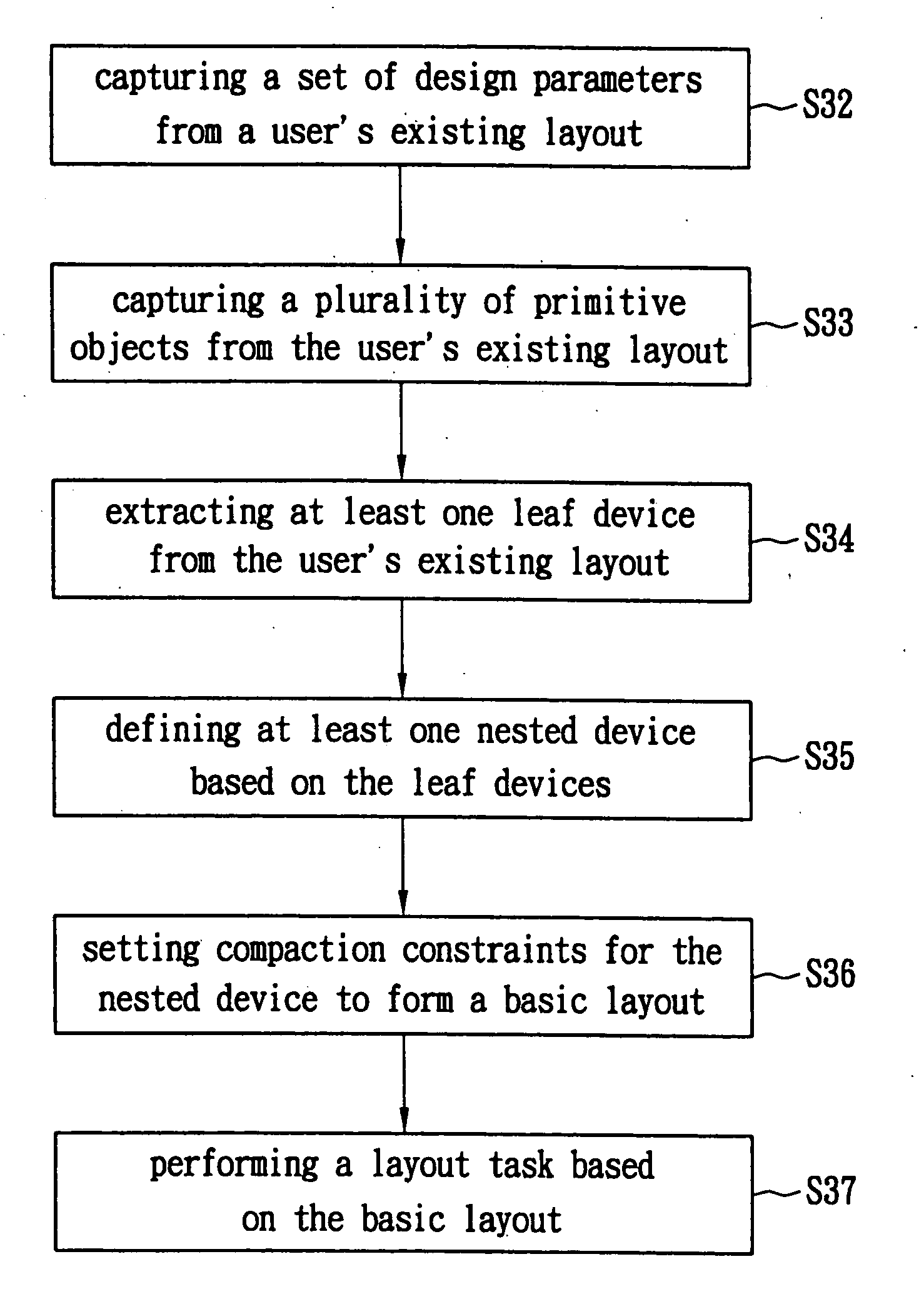

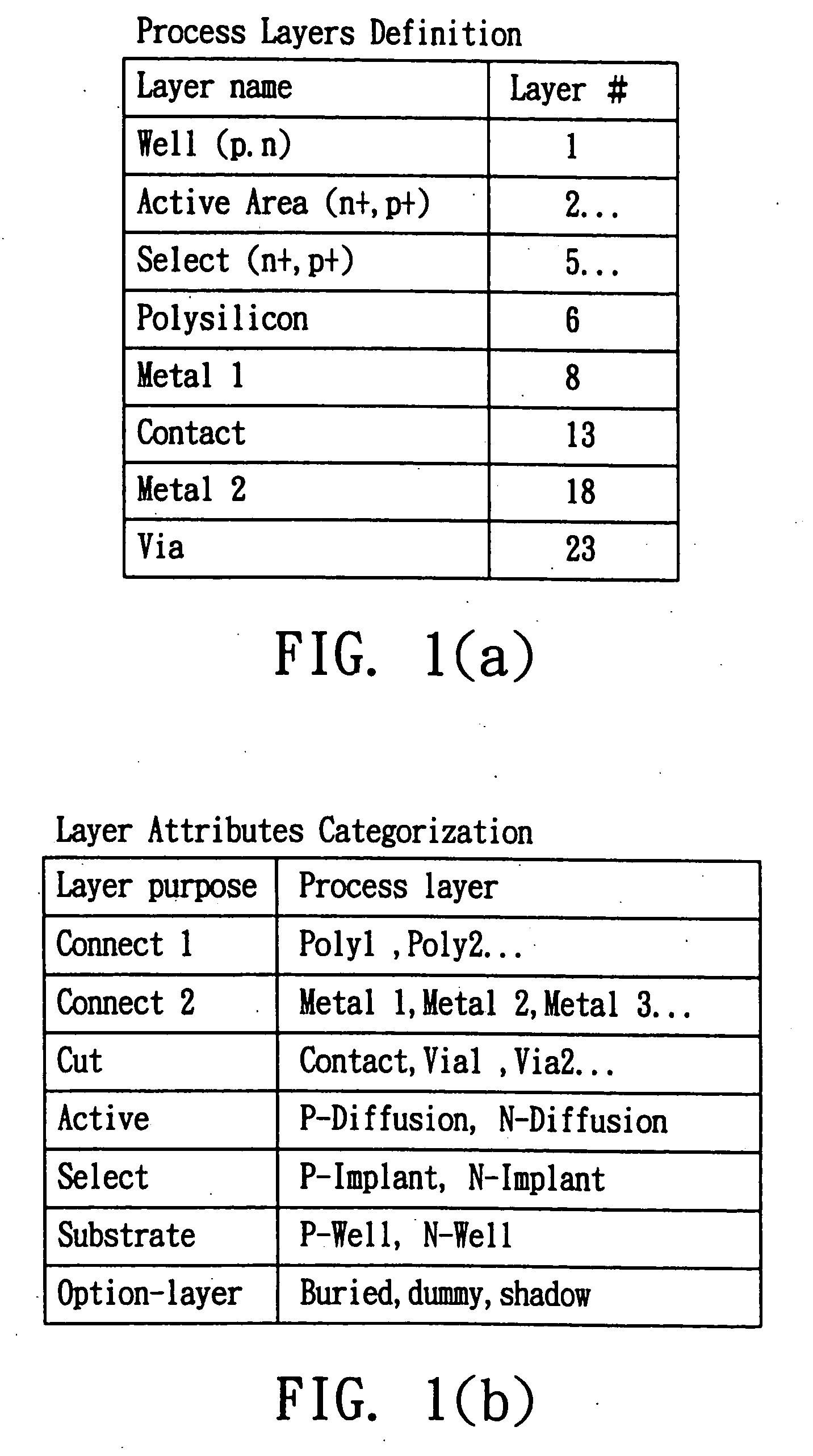

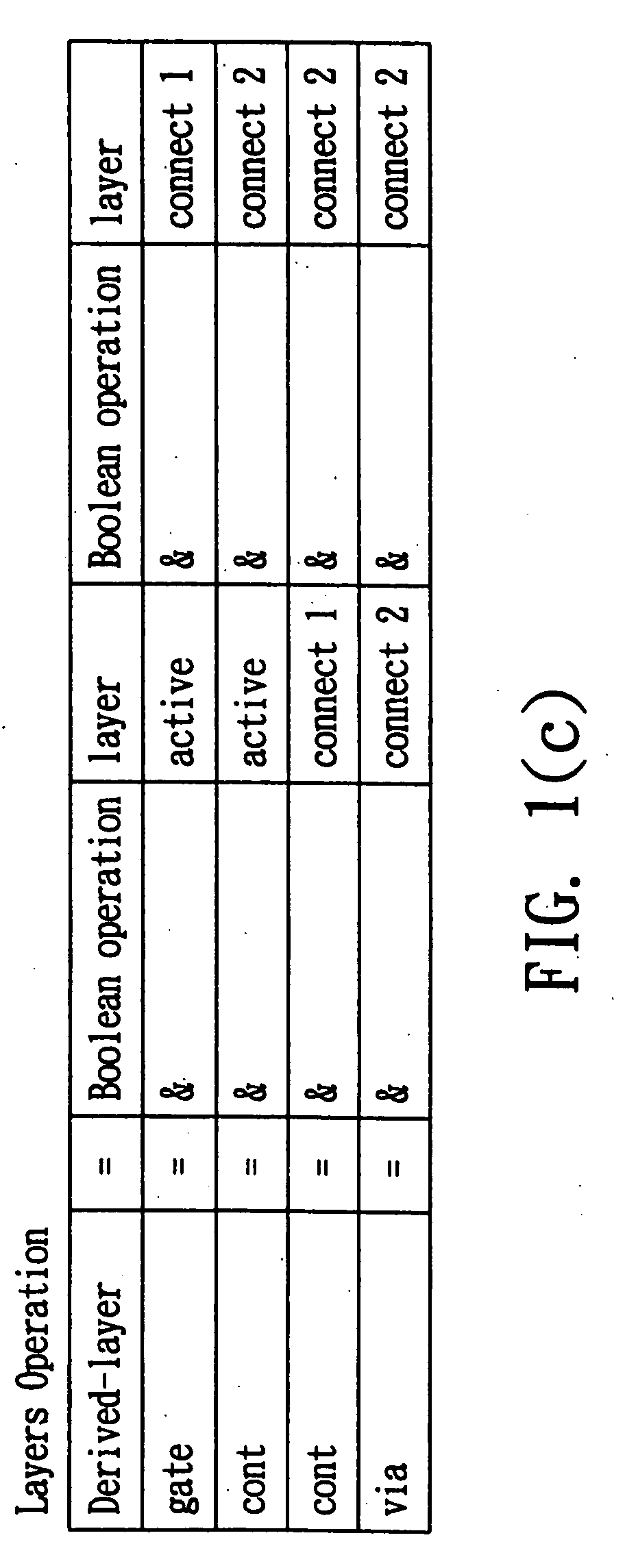

Object-oriented layout data model and integrated circuit layout method using the same

InactiveUS20080010624A1Minimal costFull coverageComputer programmed simultaneously with data introductionCAD circuit designComputer architectureIntegrated circuit layout

An integrated circuit layout method directly extracts plural primitive objects from a user's existing layout to expedite a new layout for reuse and migration and to gain the benefits of full coverage and minimal cost of layout design. The integrated circuit layout method comprises the steps of capturing a set of design parameters from a user's existing layout; capturing a plurality of primitive objects from the user's existing layout; extracting at least one leaf device from the user's existing layout; defining at least one nested device based on the leaf device; setting compaction constraints for the nested device to form a basic layout; and performing a layout task based on the basic layout. In addition, an object-oriented layout data model, used in the aforesaid integrated circuit layout method, comprises a first set of fields storing layer usages of plural layers captured from a user's existing layout to define a primitive object, a second set of field storing a set of design parameters regarding the layers, and a third set of fields defining plural data types of the first and the second sets of fields.

Owner:ANAGLOBE TECH

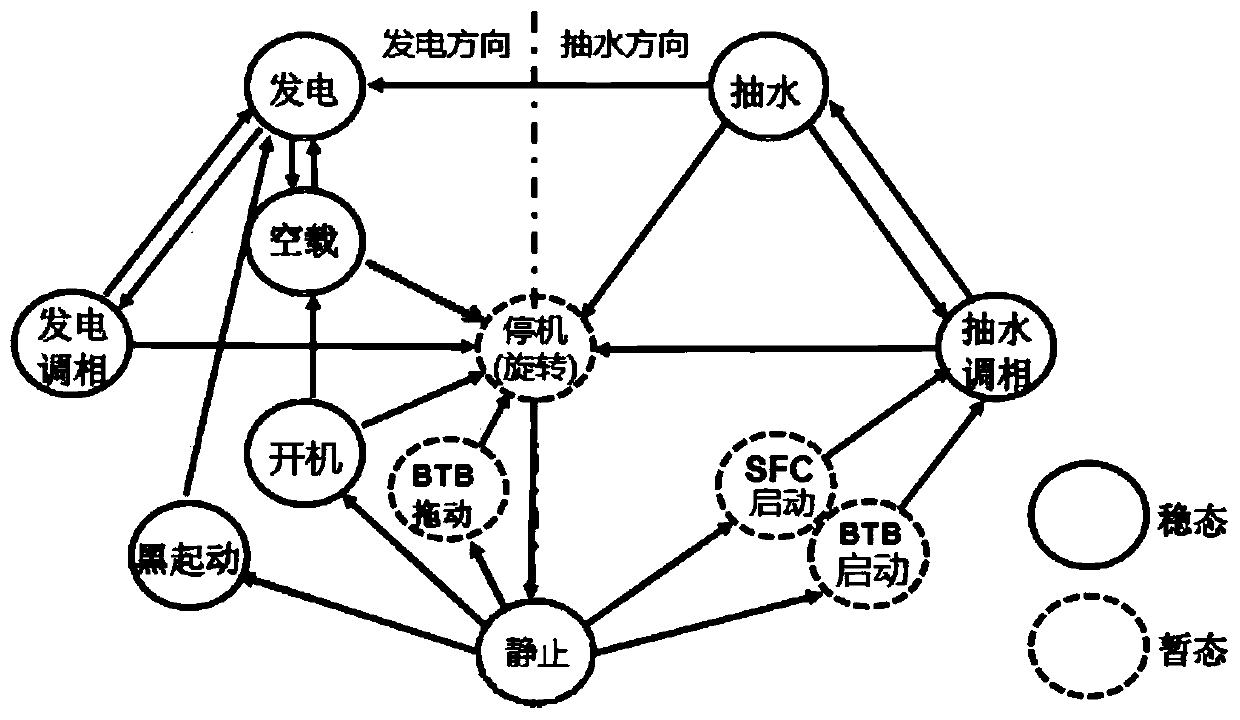

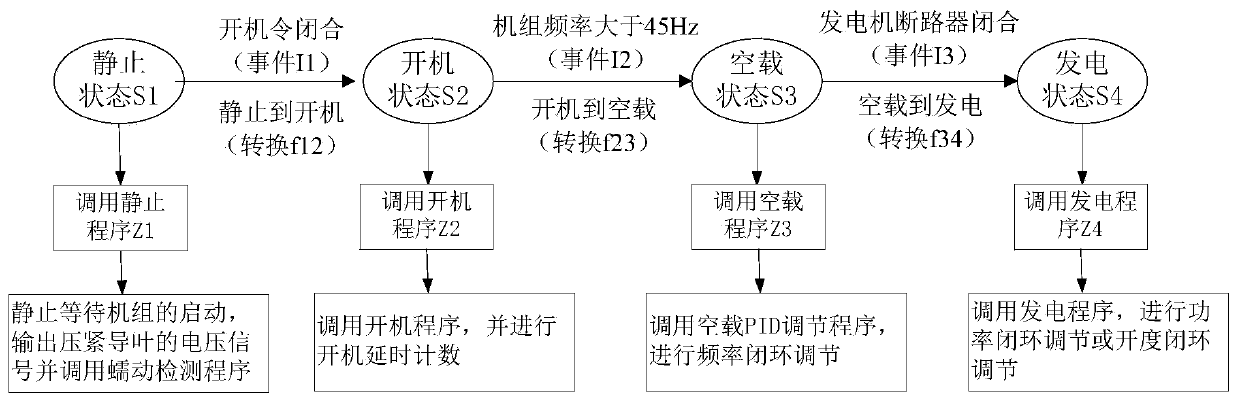

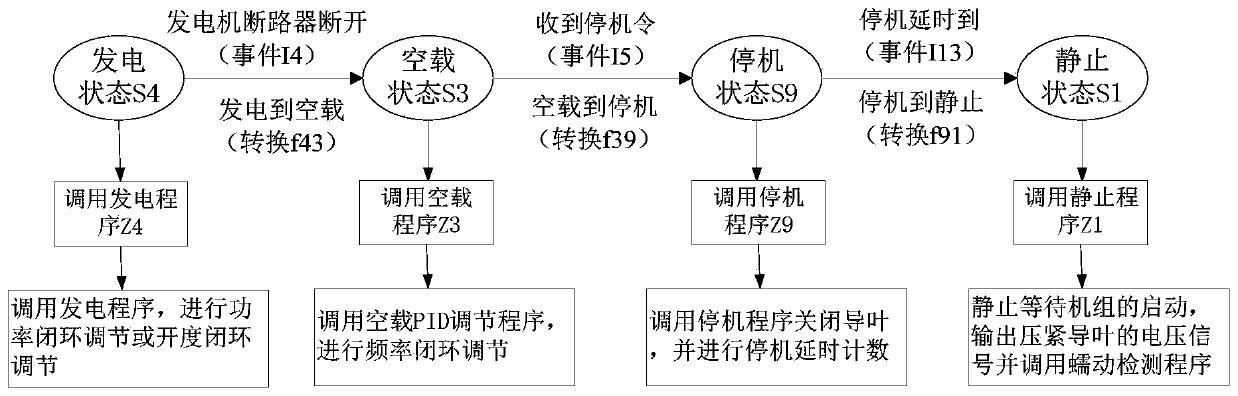

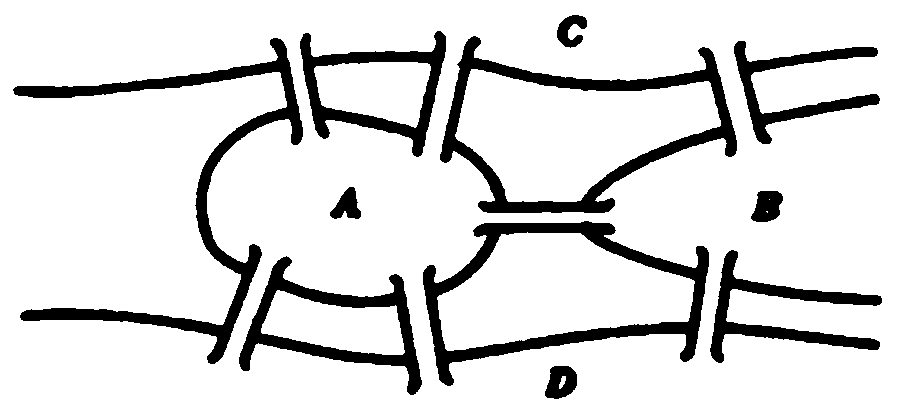

Working condition conversion method of speed regulator of pumped storage unit

InactiveCN110513241AOvercome limitationsThe complex conversion relationship is clear and clearHydro energy generationMachines/enginesGraph designTheoretical computer science

The invention discloses a working condition conversion method of a speed regulator of a pumped storage unit. The method comprises the following steps: (1) a state set, an event set, a state conversionfunction and an action set of a finite state machine are obtained by combing through various working conditions, external input events, conversion conditions among the various working conditions andaction programs executed by the various working conditions of the pumped storage unit on the basis of a finite state machine principle, wherein the state set, the event set, the state conversion function and the action set of the finite state machine are used for describing working condition conversion of the pumped storage unit; and (2) based on the state set, the event set, the conversion function and the action set of the finite state machine, the multiple working conditions, complex conversion relations and execution programs of the pumped storage unit are programmed. The method has the advantages that the limitation of a conventional trapezoid graph and a graph design method is overcome, the occurrence of wrong working condition conversion is effectively prevented, and the overall reliability of equipment is improved.

Owner:NANJING NARI WATER RESOURCES & HYDROPOWER TECH CO LTD +4

Dynamic electronic mask plate system used for preparing monolithic integration capacitive touch screen through collage method

ActiveCN103631095ARealize mass productionIncrease productivityPhotomechanical exposure apparatusMicrolithography exposure apparatusData processing systemGraphics

The invention discloses a dynamic electronic mask plate system used for preparing a monolithic integration capacitive touch screen through a collage method. The dynamic electronic mask plate system comprises a substrate bearing system, a visual identification system, a filling graph design system, an image data processing system, a dynamic digital mask graph adjustment system and an electronic mask plate system. An electronic mask is used to replace a fixed metal pattern photoresistance mask plate in the prior art, the position of a filling graph is adjusted according to the deviation position and the angle of inclination of a small piece of glass in the production of preparing the monolithic integration capacitive touch screen through the collage method, and the small piece of glass having position, height and angle deviations is exposed, so that the large-scale volume production of OGS touch screens is achieved, the production efficiency is improved, and the dynamic electronic mask plate system is widely applied to the manufacturing of a multilayer composite membrane layer in a touch screen, an electronic product, a photovoltaic product or a PCB (printed circuit board) or implementing of perforated locating and sleeving between layers.

Owner:ZHONGSHAN AISCENT TECH

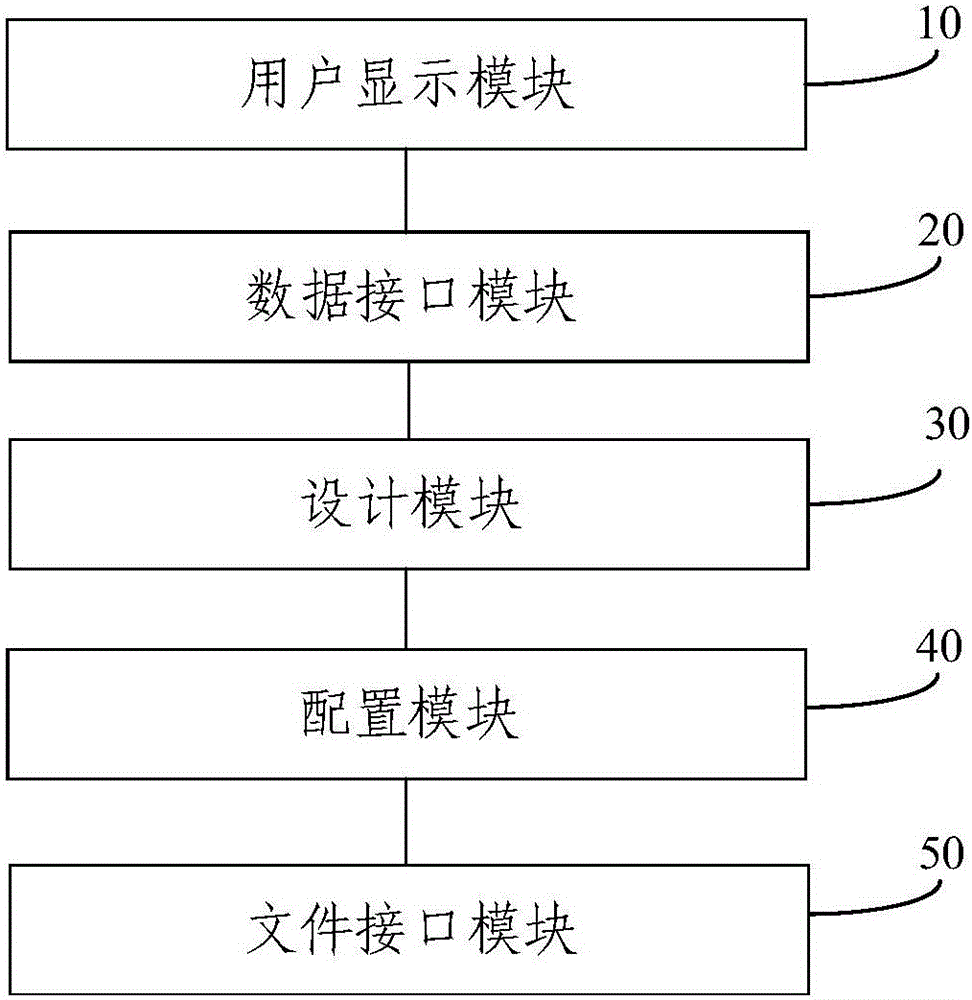

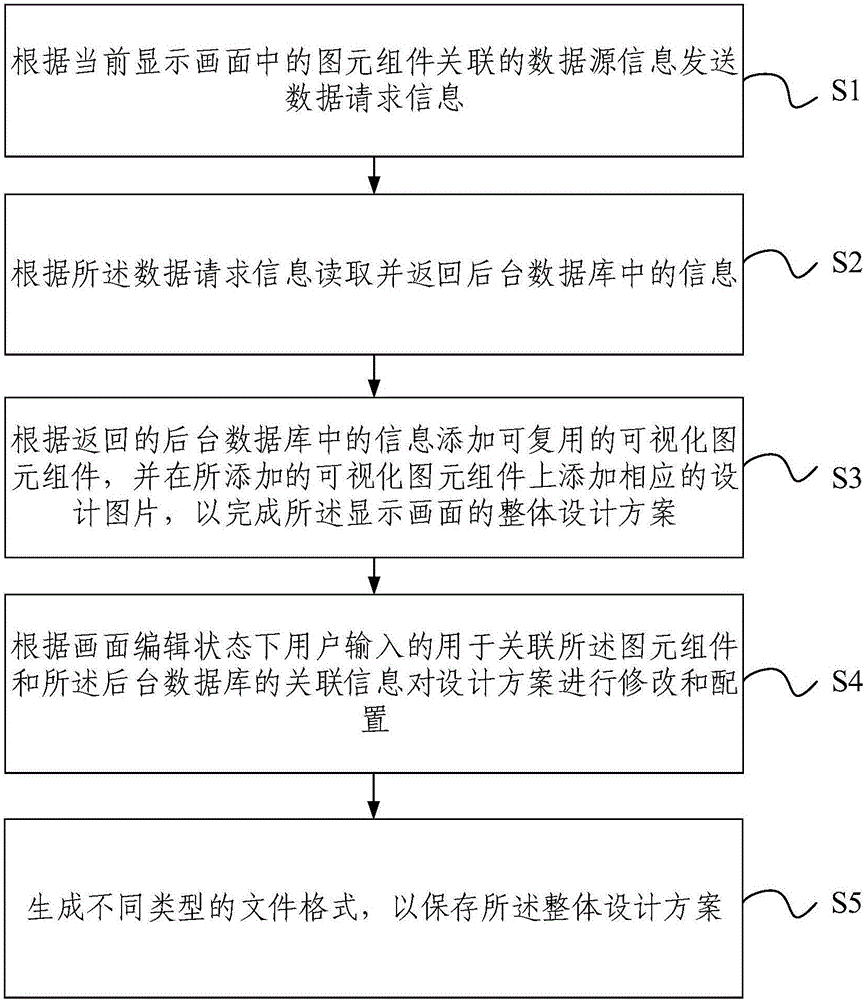

Power grid comprehensive information monitoring graph generation system and method

InactiveCN105976322AIncrease profitImprove reusabilityData processing applicationsGeometric image transformationGraphicsGraph generation

The invention relates to a power grid comprehensive information monitoring graph generation system and method, and the system comprises a user display module, a data interface module, a design module, a configuration module, and a file interface module. According to the invention, the system and method build a mapping relation library based on a large-screen overall design scheme and a graphic file, which are generated in an integrated manner, and a visual graph element assembly. The system and method can achieve the packaging and flexible configuration of the visual assembly, can iron out the defects that a large-screen graph design scheme of a conventional power grid monitoring system is lower in reusability and is difficult for later configuration and modification, can improve the utilization rate and the reusability of the assembly, and can improve the implementation efficiency of a project.

Owner:DALIAN POWER SUPPLY COMPANY STATE GRID LIAONING ELECTRIC POWER +3

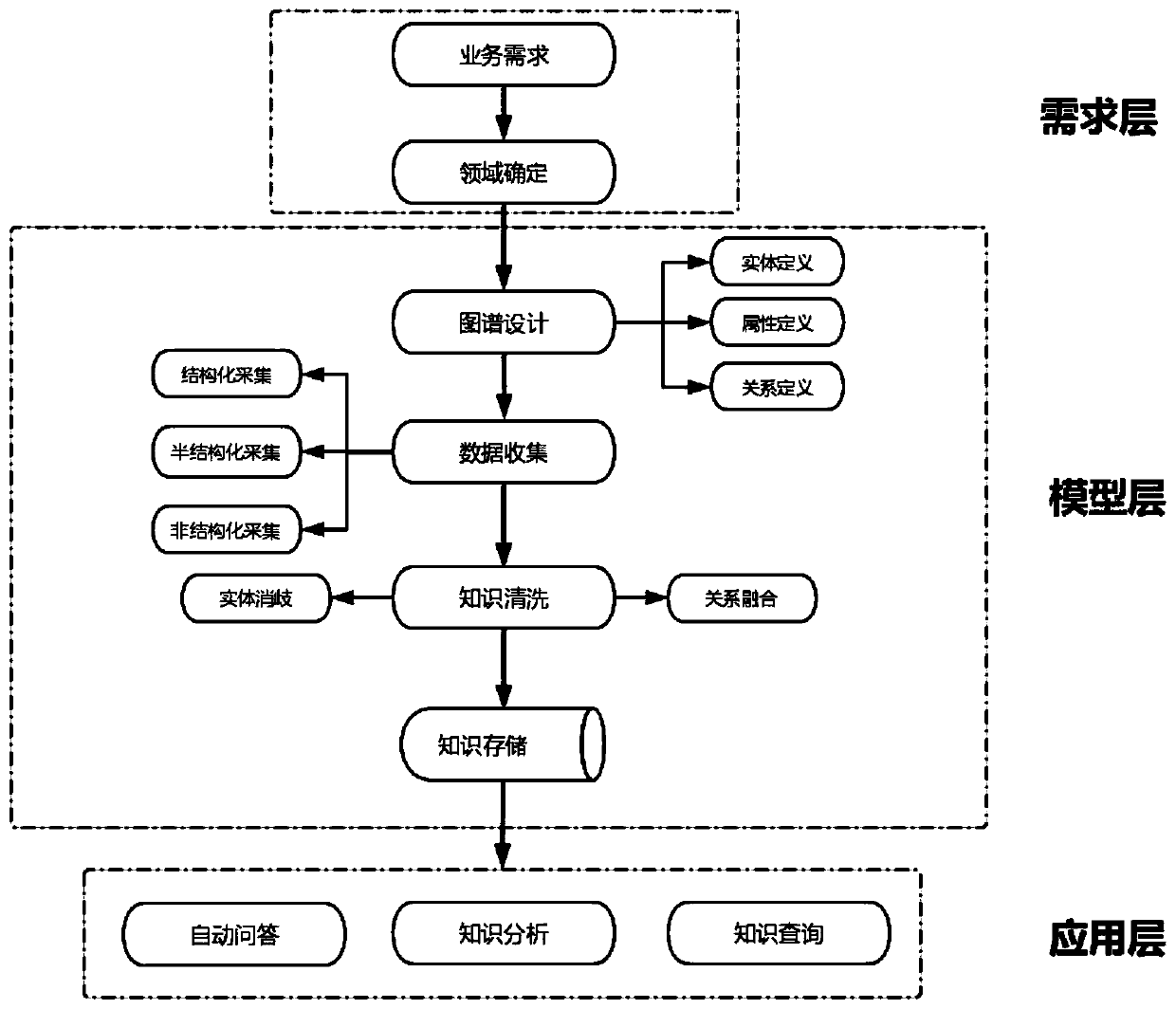

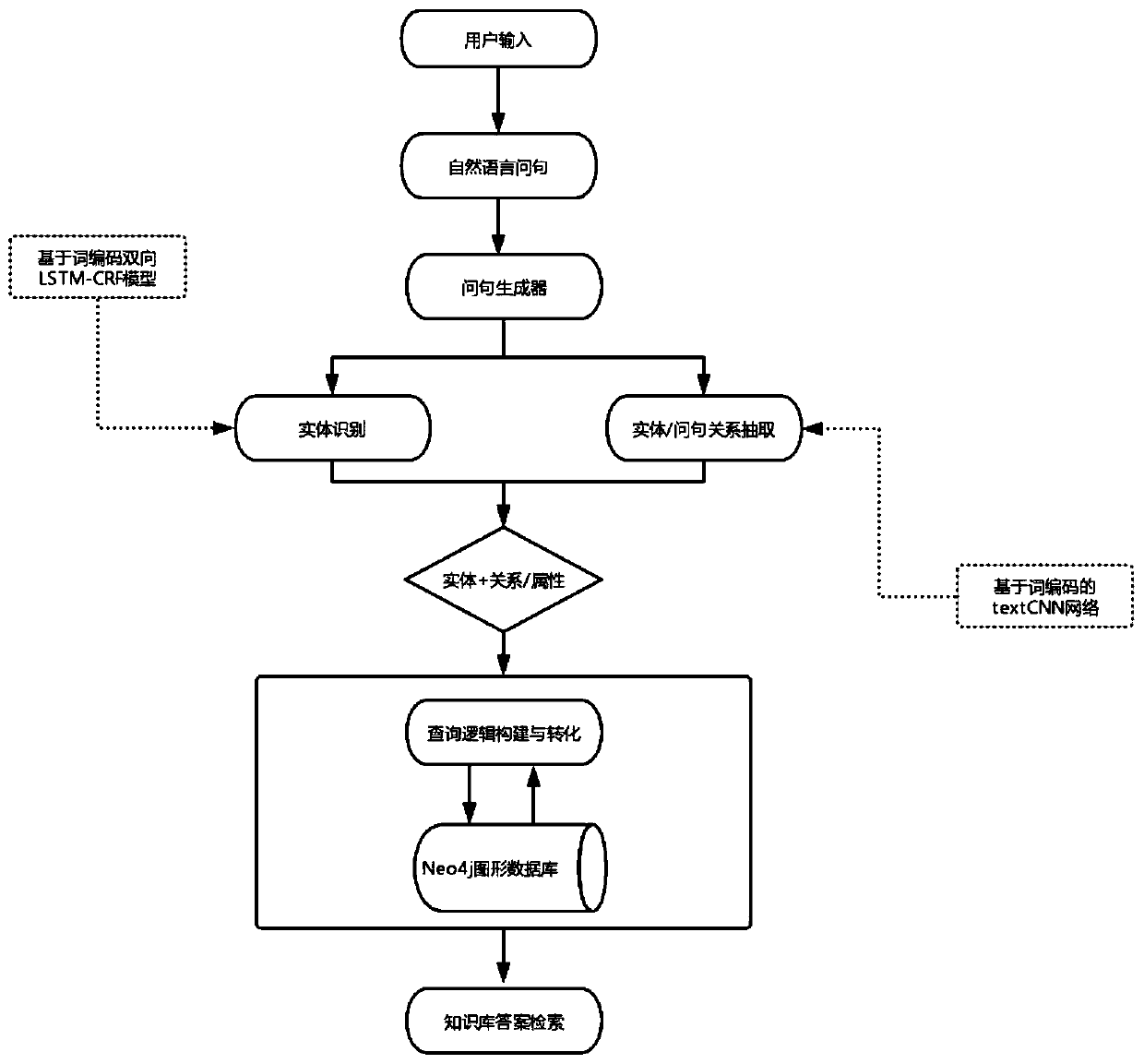

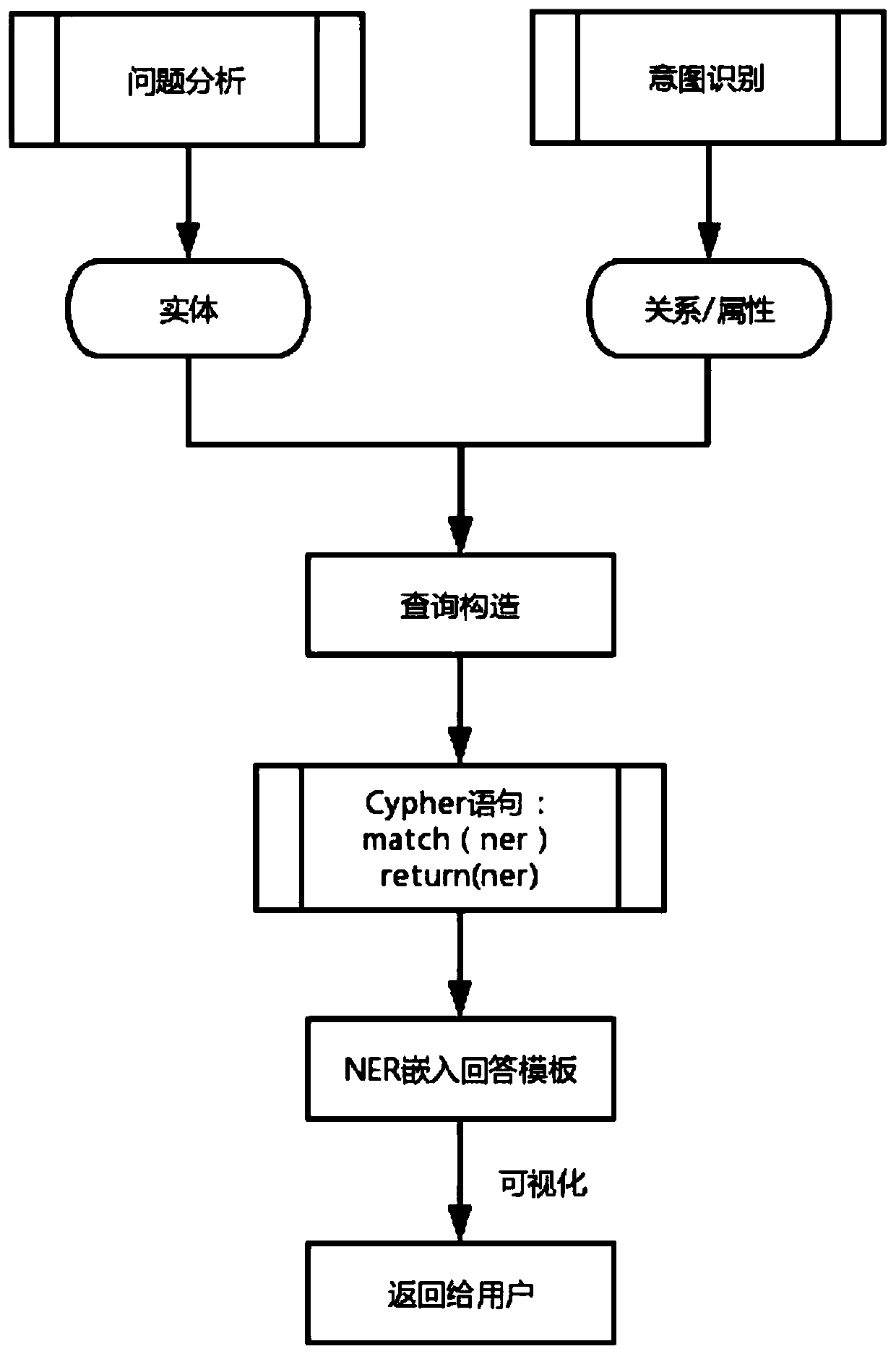

Minority field intelligent question-answering method based on knowledge graph

PendingCN111324691APromote disseminationImprove retrieval efficiencyNatural language data processingNeural architecturesQuestions and answersKnowledge graph

The invention discloses a minority field intelligent question-answering method based on a knowledge graph, and belongs to the field of question-answering methods based on artificial intelligence. According to the technical scheme, the method comprises the following steps: designing an atlas according to correlation between entity categories; obtaining an original corpus constructed by the minoritydomain knowledge graph according to the graph design; processing the original corpus; construction of knowledge graph. The minority domain intelligent question-answering method based on the knowledgegraph has the beneficial effects that by constructing the minority domain knowledge graph, related data can be integrated and normalized, related knowledge of minority can be more reasonably appliedto practical application, and spreading of national culture is facilitated; and the knowledge graph is applied to intelligent questions and answers, so that the retrieval efficiency and the absorptionefficiency of national knowledge can be improved.

Owner:DALIAN NATIONALITIES UNIVERSITY

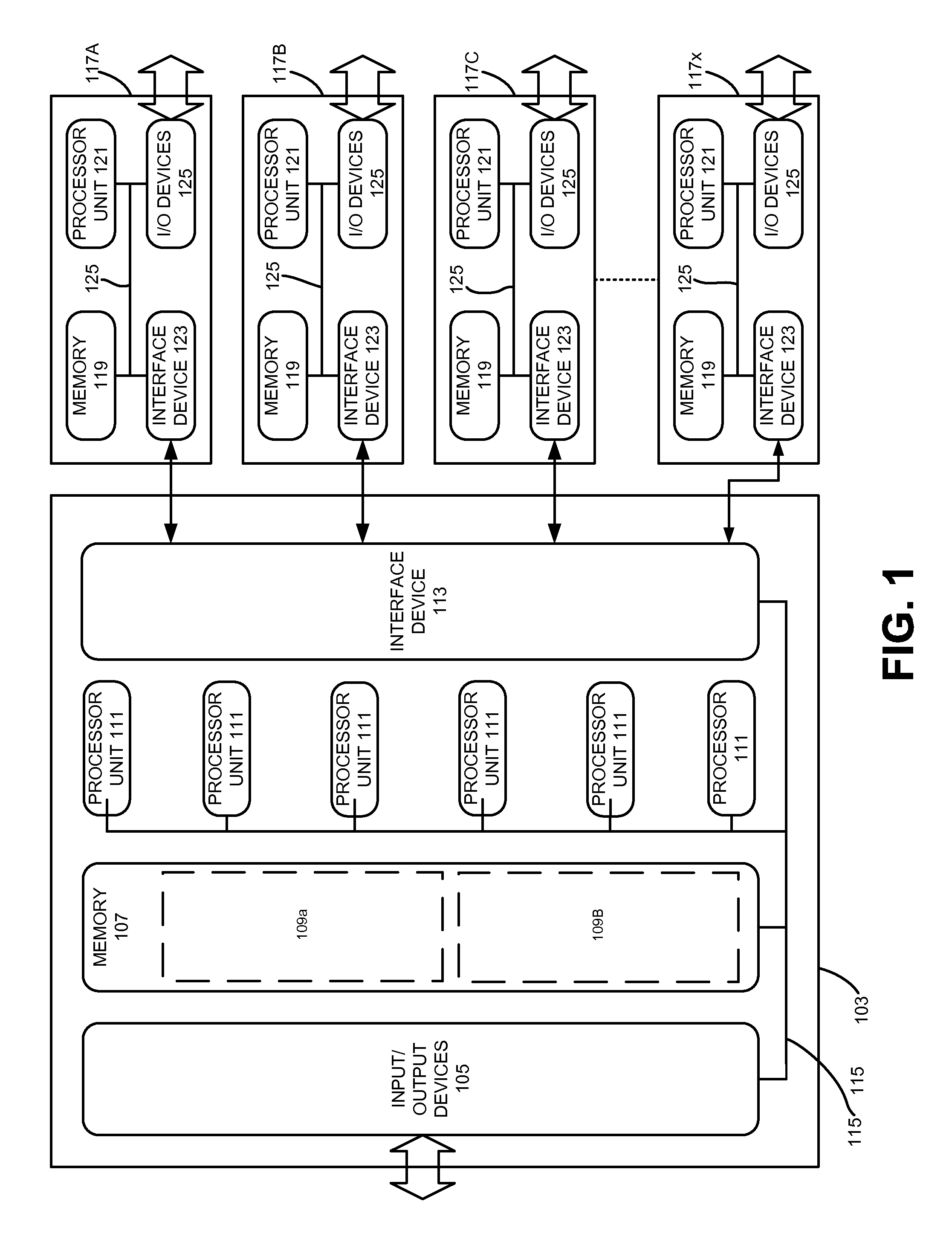

Estimation of Power and Thermal Profiles

ActiveUS20130198704A1CAD circuit designSoftware simulation/interpretation/emulationDevice parametersIntegrated circuit

Aspects of the invention relate to techniques for estimating power and thermal profiles for an integrated circuit design. With various implementations of the invention, a group of devices is identified in a netlist based on information of the group of devices. The netlist may be a schematic netlist or a layout netlist extracted from a layout design. Power consumption information for the group of devices is determined based on device parameters for the group of devices and a lookup table. The determined power consumption information is then associated with layout location information. A thermal profile may then be estimated based on the power consumption information.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

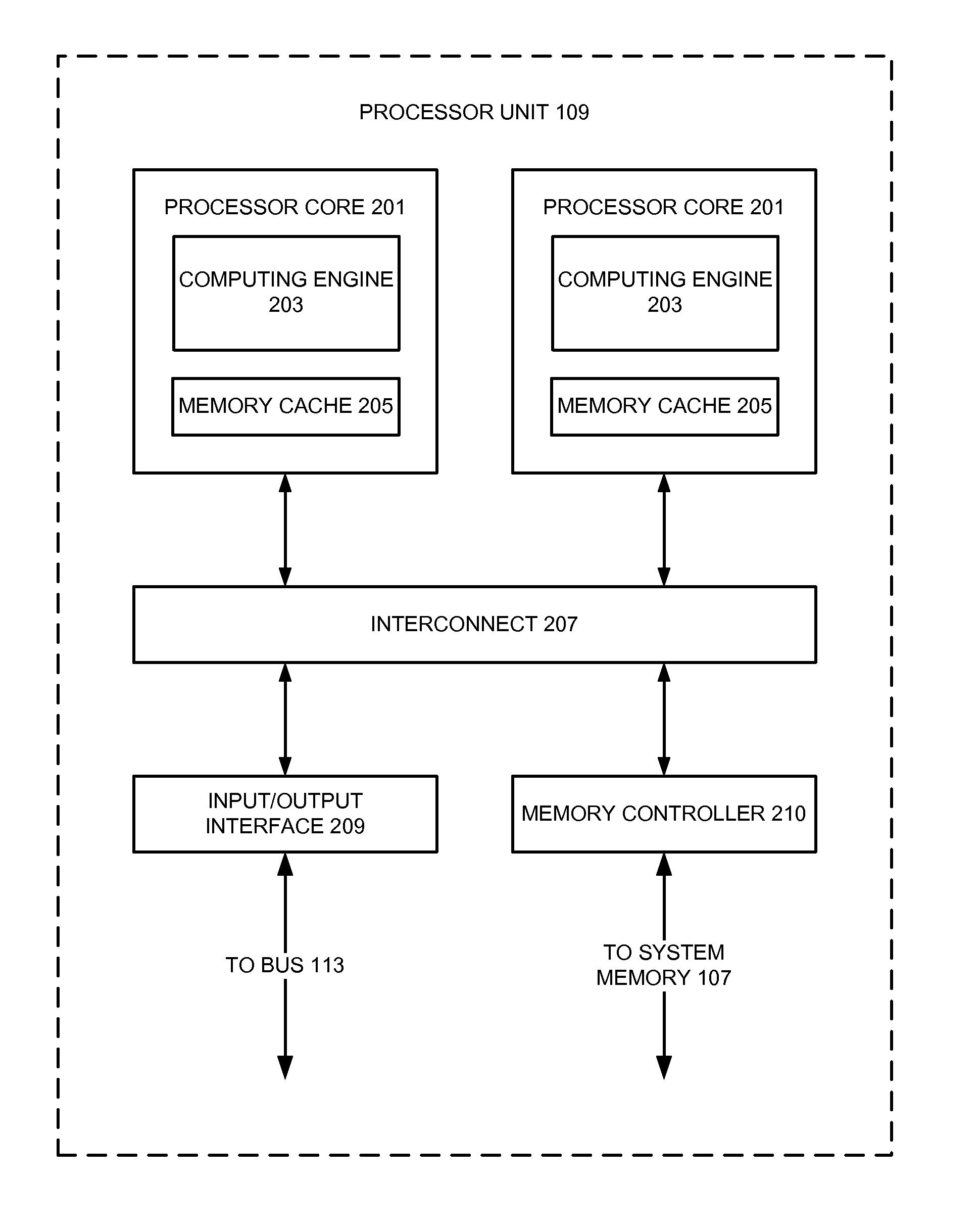

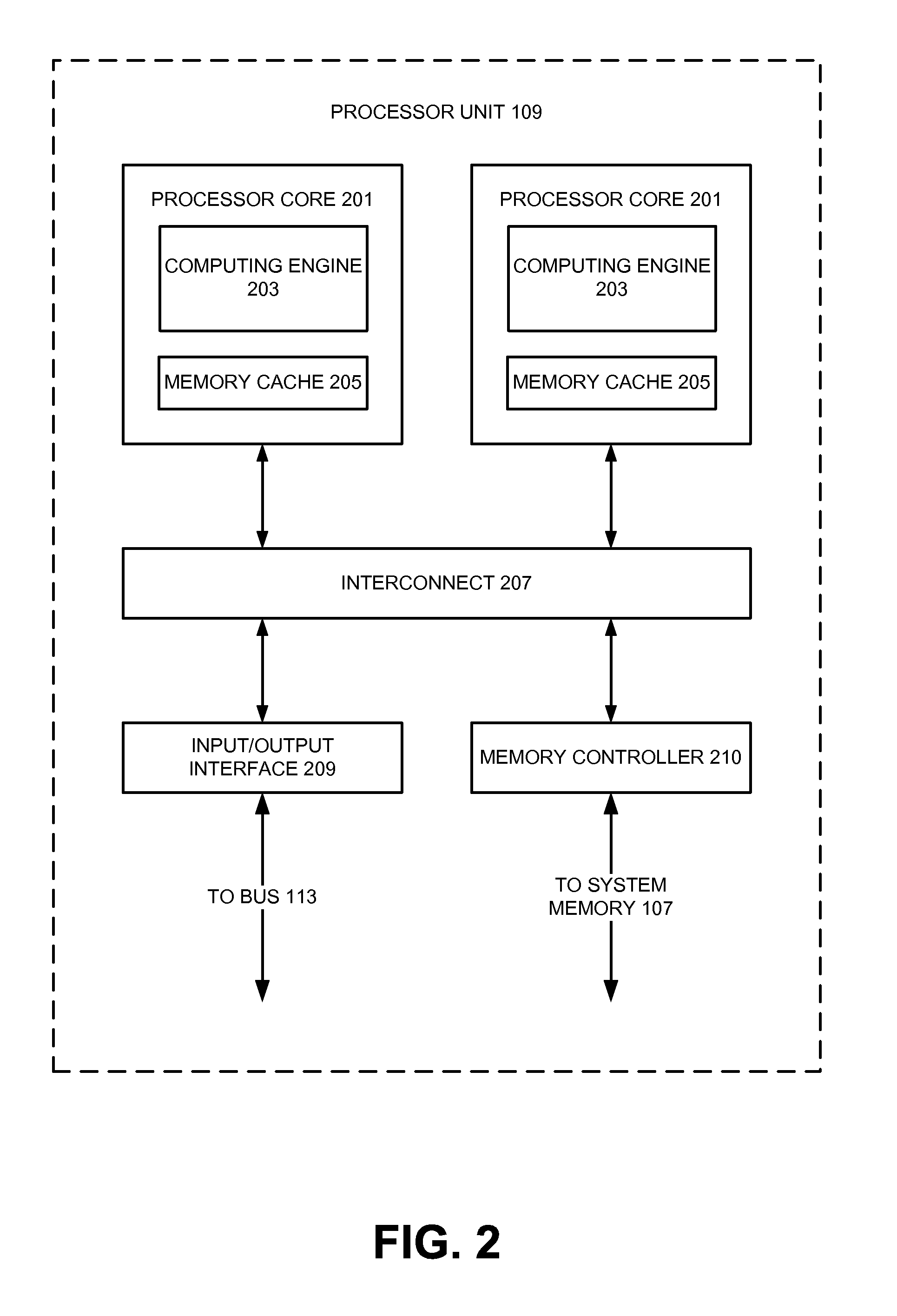

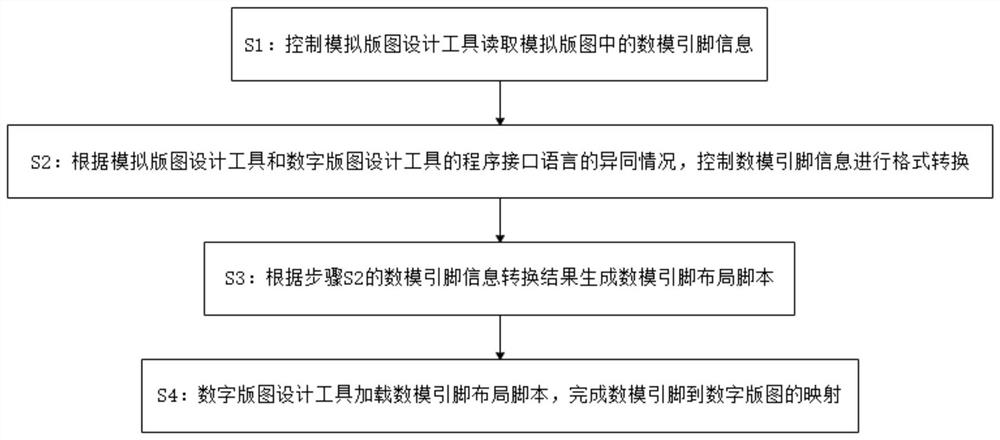

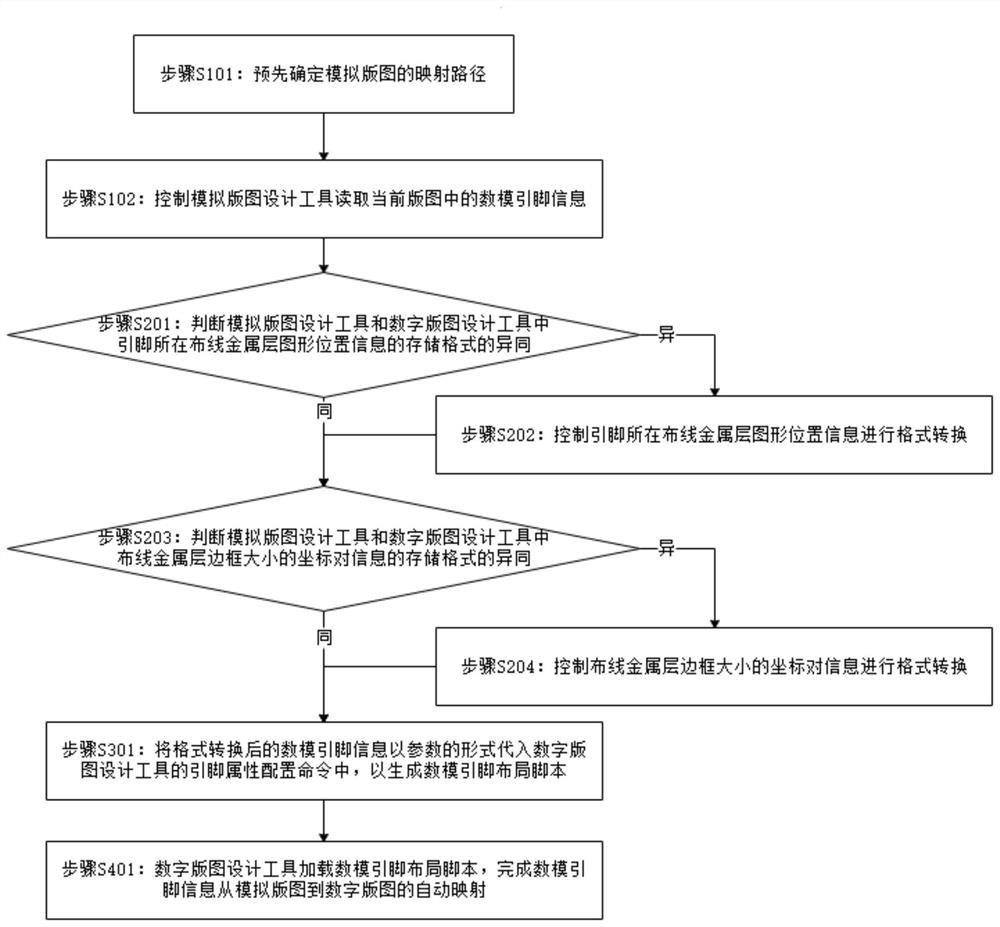

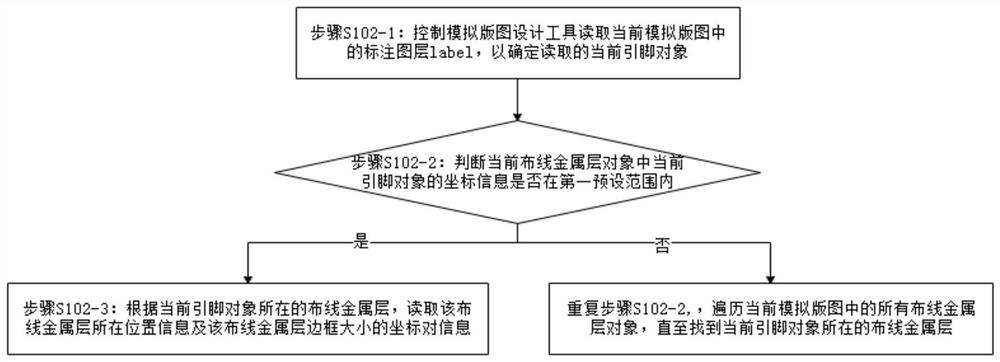

Method for mapping digital-analog pin of analog layout to digital layout

PendingCN112507649AReduce the number of iterationsShorten the production cycleComputer aided designSpecial data processing applicationsComputer hardwareComputer architecture

The invention discloses a method for mapping a digital-analog pin of an analog layout to a digital layout. The method comprises the following steps of: 1, controlling an analog layout design tool to read digital-analog pin information of the analog layout; 2, controlling the digital-analog pin information read in the step 1 to perform format conversion according to program interface language similarities and differences corresponding to the analog layout design tool and the digital layout design tool; 3, controlling the digital-analog pin information to generate a digital-analog pin layout script according to the format conversion result in the step 2; and step 4, controlling a digital layout design tool to load the digital-analog pin layout script according to the digital-analog pin layout script generated in the step 3, and completing mapping of the digital-analog pin to the digital layout. According to the method, automatic mapping of the digital-analog pin information in the designof the analog layout package digital layout is realized, so that the time and energy consumed by a layout designer in the layout stage are reduced, and the processing period of information interaction of the digital template graph is greatly shortened.

Owner:AMICRO SEMICON CORP

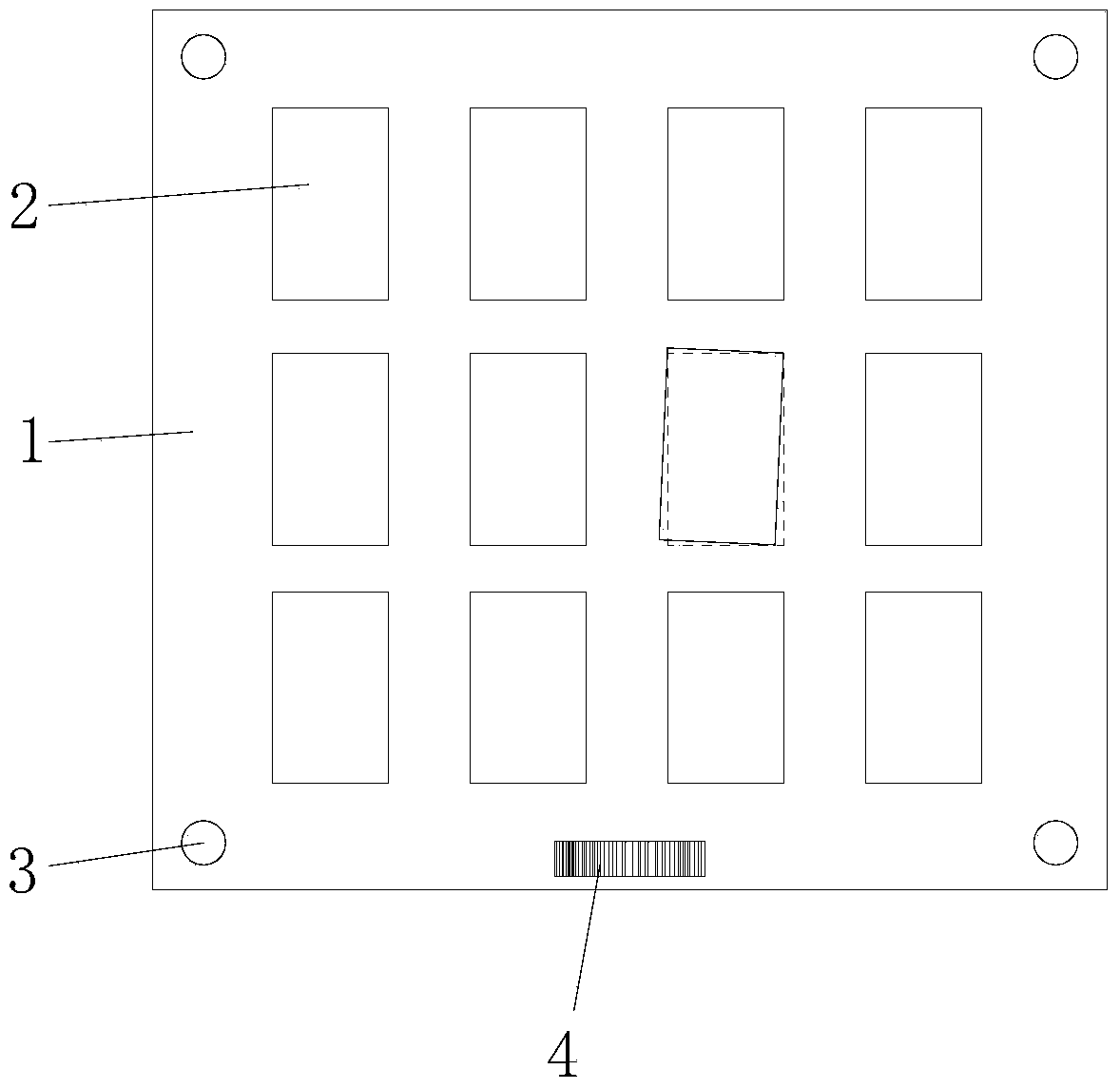

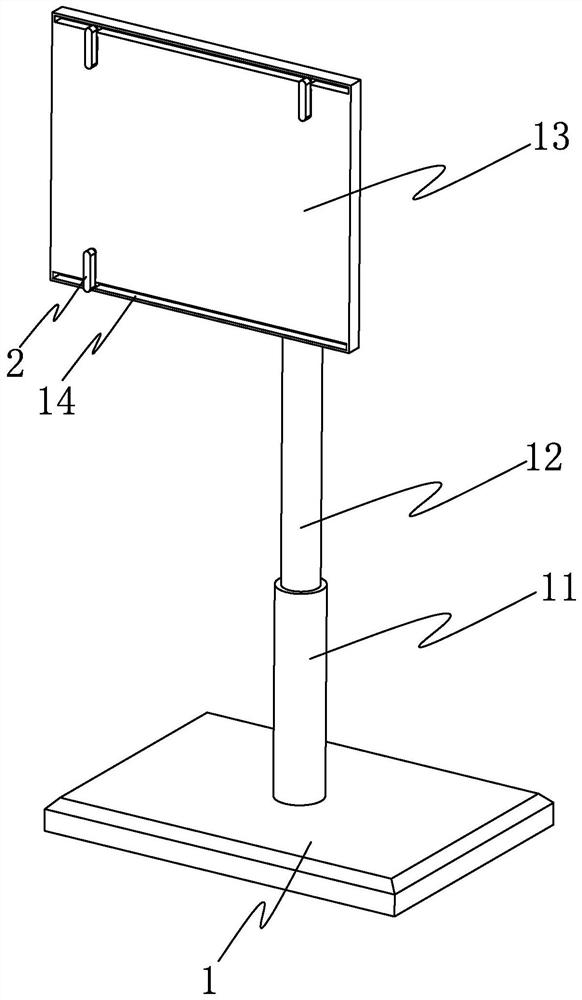

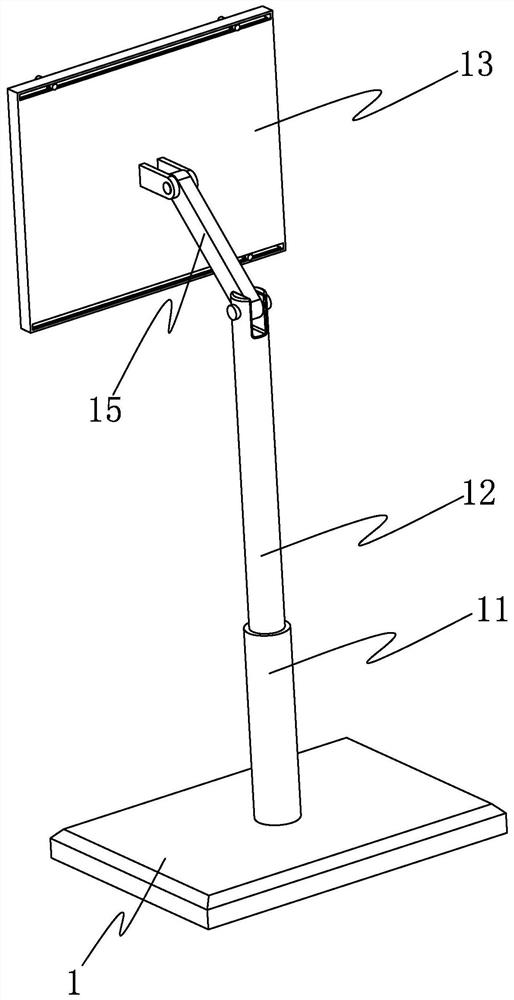

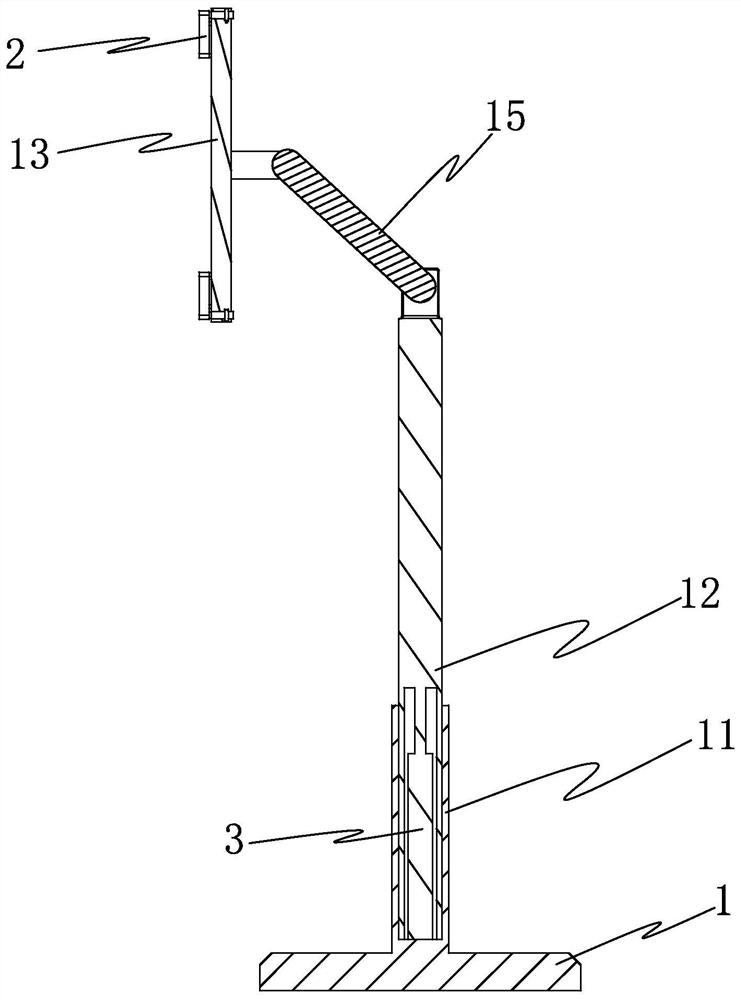

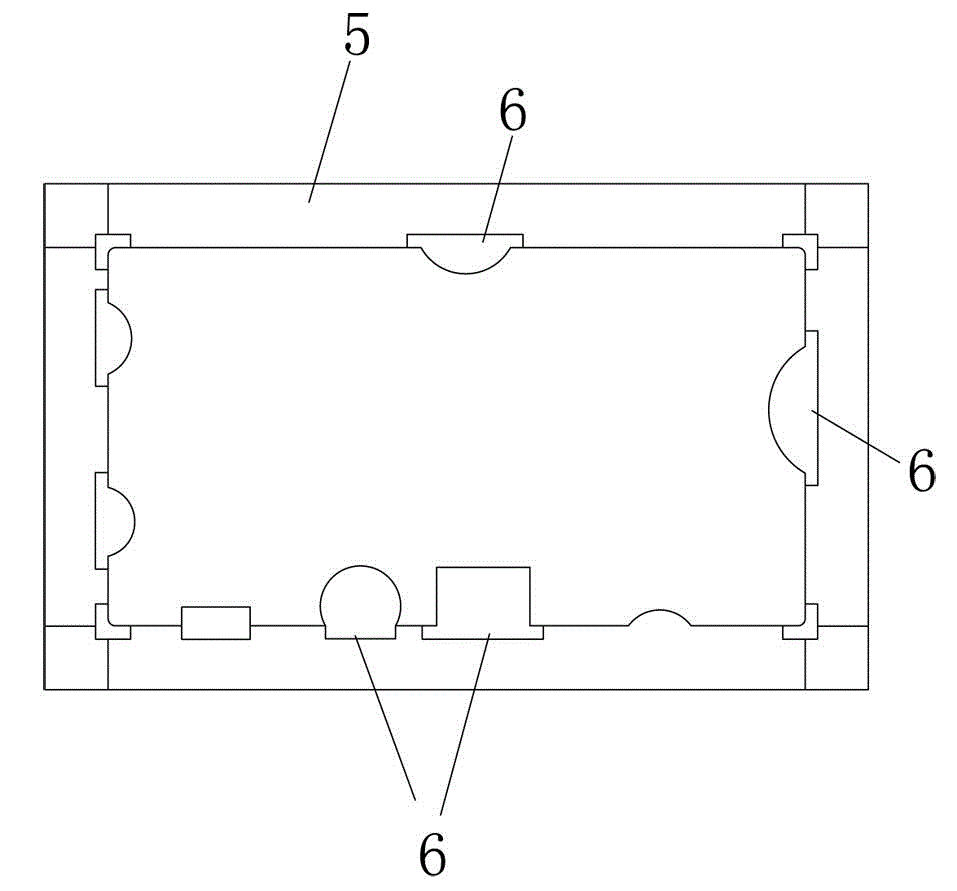

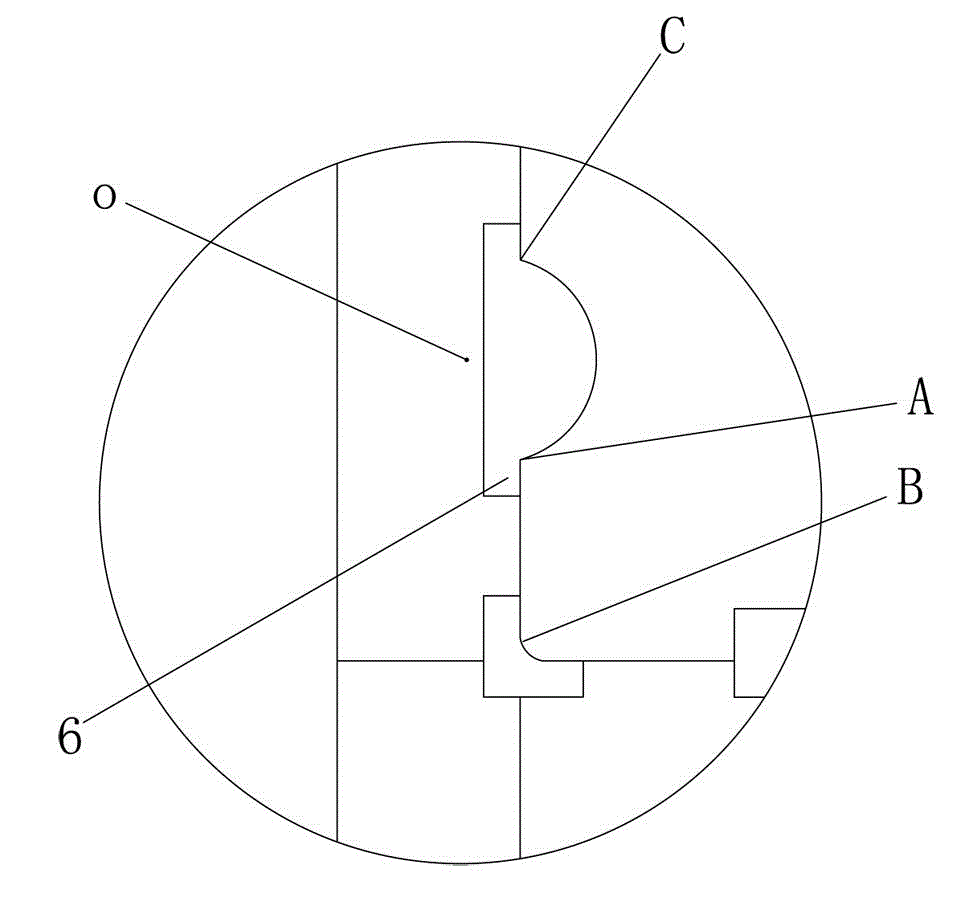

Graph design drawing device

ActiveCN112205755AEasy to fixImprove stabilityDrawing boardsDrawing desksStructural engineeringIndustrial engineering

The invention discloses a graphic design drawing device which comprises a base, a fixing rod is arranged on the base, a telescopic rod is movably inserted into the fixing rod, a moving assembly for driving the telescopic rod to move up and down is arranged in the fixing rod, a connecting rod is hinged to the upper portion of the telescopic rod, and a drawing board is hinged to the connecting rod.Guide grooves are formed in the upper portion and the lower portion of the drawing board respectively, at least two paper pressing devices are arranged in the guide grooves, the paper pressing devicescan transversely move relative to the guide grooves and rotate to conduct angle adjustment, the paper pressing devices can be adjusted according to use requirements, and the use requirements are met.

Owner:ZHENGZHOU RAILWAY VOCATIONAL & TECH COLLEGE

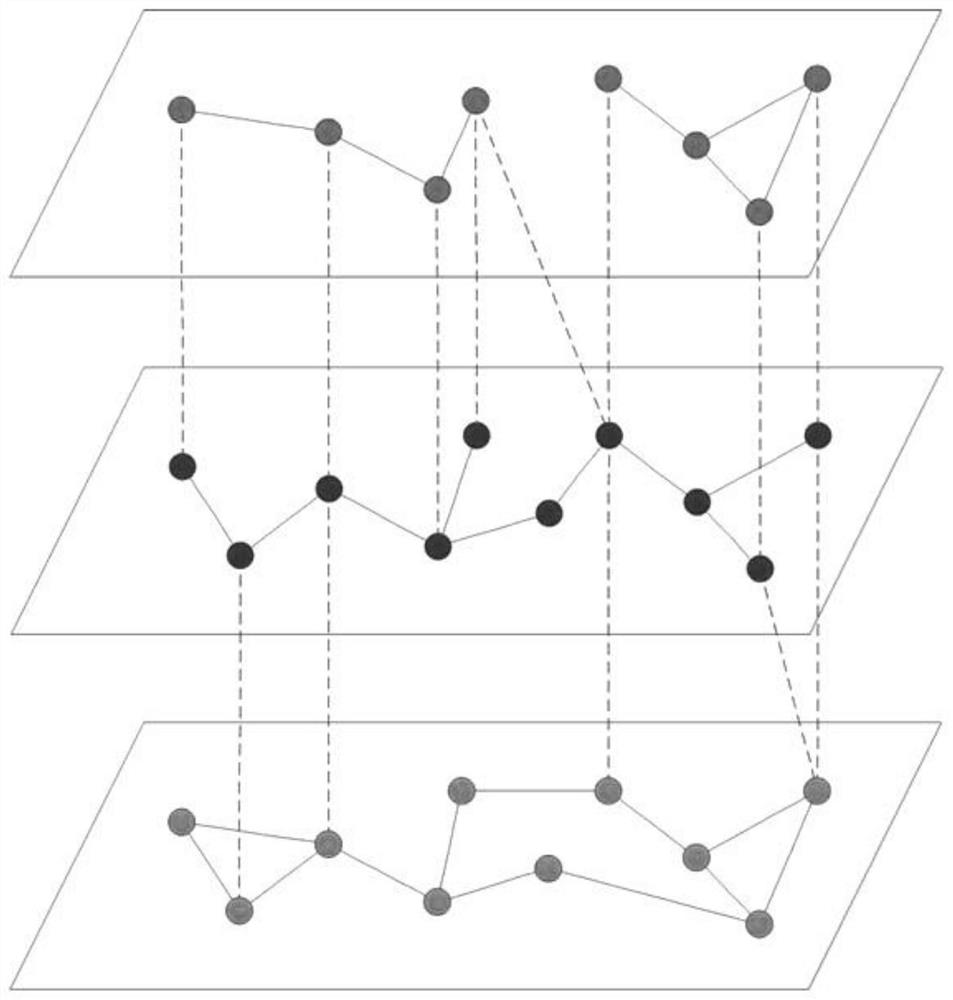

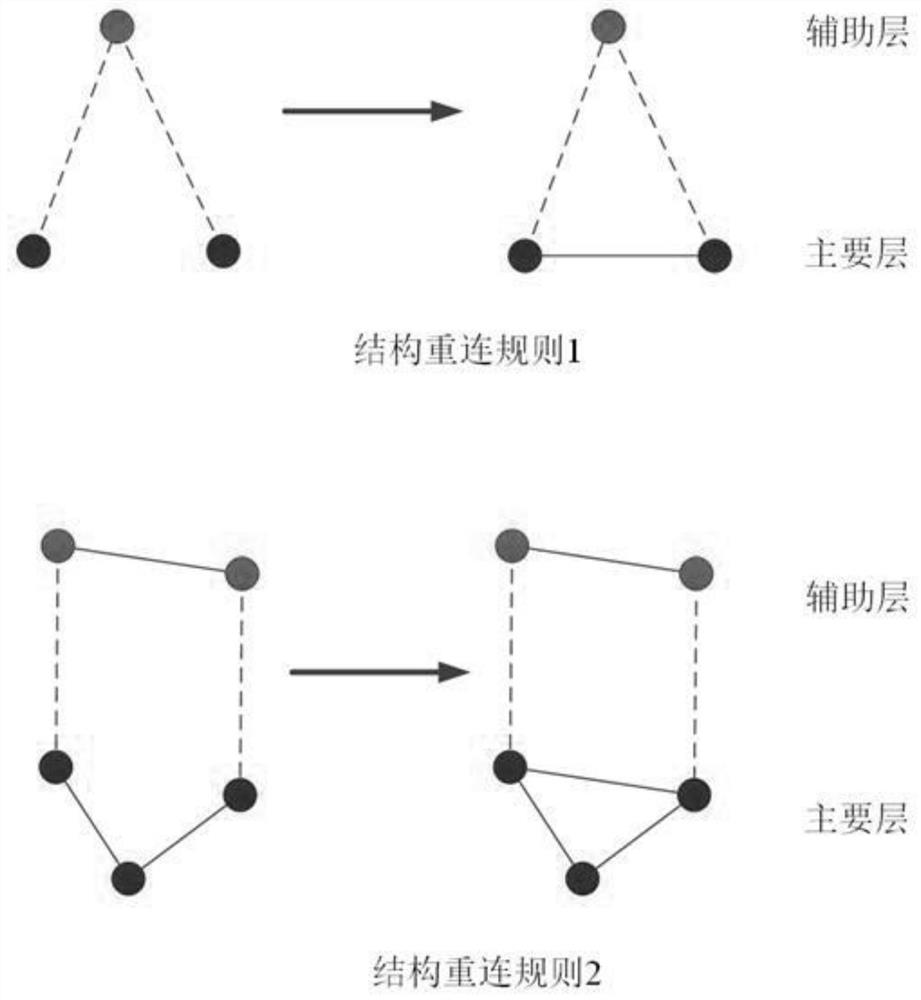

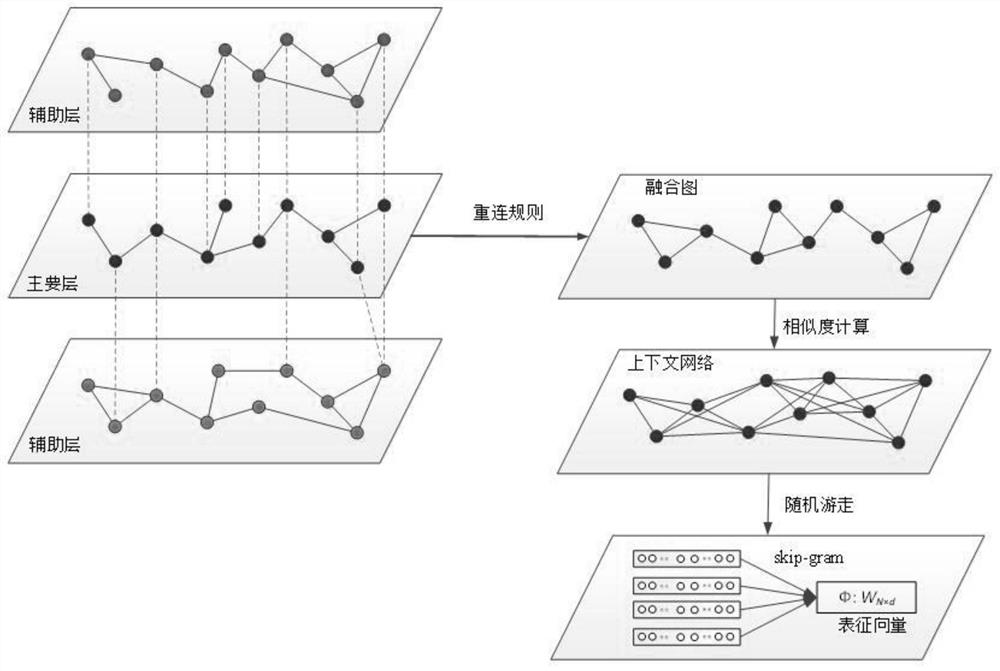

Multilayer heterogeneous network space node characterization method

ActiveCN112311608AImprove clustering effectExtend the relationship between nodesCharacter and pattern recognitionData switching networksAlgorithmTheoretical computer science

The invention provides a multilayer heterogeneous network space node characterization method, which comprises the following steps of S1, reconstructing a network according to a structure reconnectionrule, and generating a fusion graph based on a main layer and an auxiliary layer; S2, designing an algorithm of an adjacent distance, a structure distance and an attribute distance between node pairsfor the fusion graph; S3, in combination with the algorithm, obtaining the similarity between any two nodes in the fusion graph; S4, after similarity calculation of all node pairs in the fusion graphis completed, starting to construct a context network graph, and further generating an undirected unweighted graph; and S5, after carrying out random walk on the sampling path based on the context network, training a node representation vector through a skipgram model. Due to the facts that the multi-layer heterogeneous network is reconstructed, and the considered similarity is comprehensive, compared with other characterization algorithms, the method has a better effect.

Owner:中国人民解放军66136部队

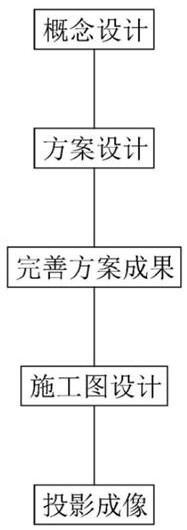

Building design method based on BIM technology

PendingCN113987659AImprove consistencyQuality improvementGeometric CADDesign optimisation/simulationDesign planAnalysis data

The invention provides a building design method based on a BIM technology. The method comprises the following steps of conducting concept design: according to urban overall planning requirements and user requirements, building a preliminary model through site and environment simulation analysis, conducting scheme design: building a wind speed analysis model and a lighting analysis model on the preliminary model for simulation analysis, conducting scheme comparison and selection through analysis data and comprehensive factors, and estimating structure type selection, perfecting a scheme result: perfecting a scheme model, establishing a building center file database, covering the preliminary model with equipment rooms and pipeline lines, and forming an overall model, construction drawing design: importing the overall model design scheme into 3D max, carrying out collision detection and three-dimensional pipeline synthesis, adjusting and optimizing collided pipelines, and exporting an optimized two-dimensional construction drawing, and conducting projection imaging: using a BIM model rendering technology to present the optimization model design scheme, outputting various digital effect pictures of the design scheme, and stereoscopically presenting the digital effect pictures by using 3D projection.

Owner:山东新汉唐数据科技有限公司

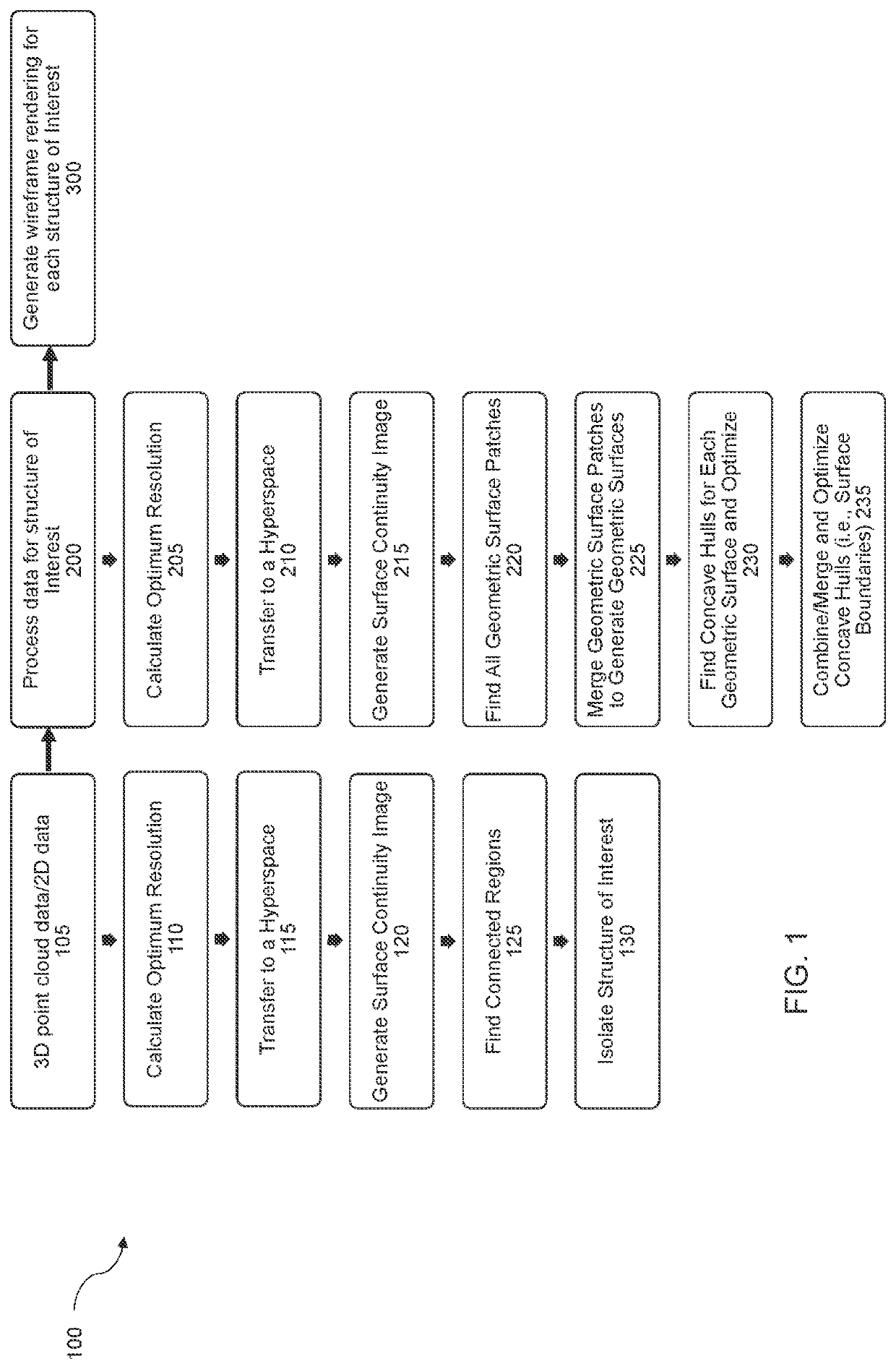

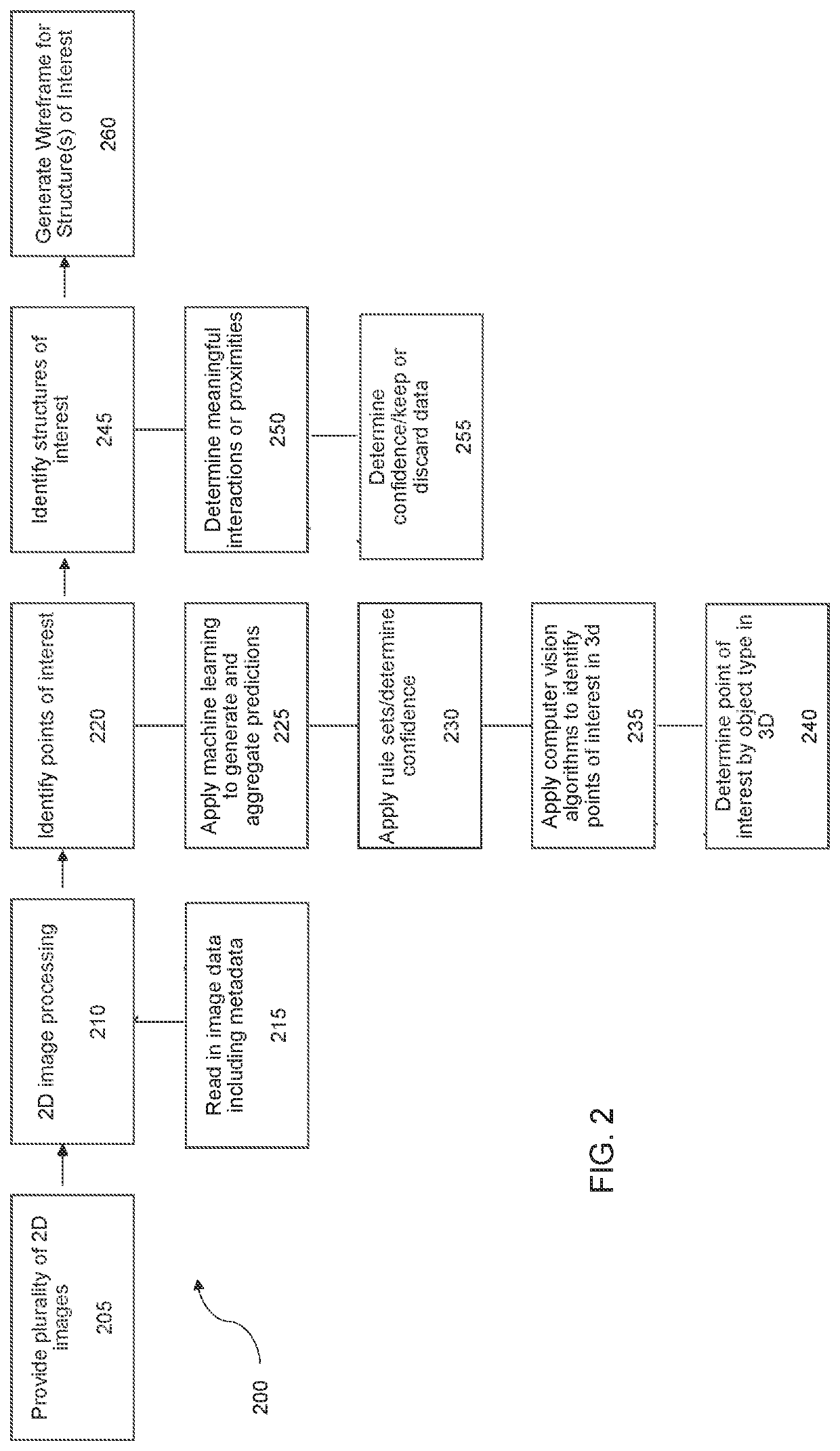

Systems and methods for processing 2d/3d data for structures of interest in a scene and wireframes generated therefrom

The inventions herein relate generally to improvements in the generation of wireframe renderings derived from 2D and / or 3D data that includes at least one structure of interest in a scene. Such wireframe renderings and similar formats can be used in, among other things, 2D / 3D CAD drawings, designs, drafts, models, building information models, augmented reality or virtual reality, and the like. Measurements, dimensions, geometric information, and semantic information generated according to the inventive methods can be accurate in relation to the actual structures. The wireframe renderings can be generated from a combination of a plurality of 2D images and point clouds, processing of point clouds to generate virtual / synthetic views to be used with the point clouds, or from 2D image data that has been processed in a machine learning process to generate 3D data. In some aspects, the wireframe renderings are accurate in relation to the actual structure of interest, automatically generated, or both.

Owner:POINTIVO

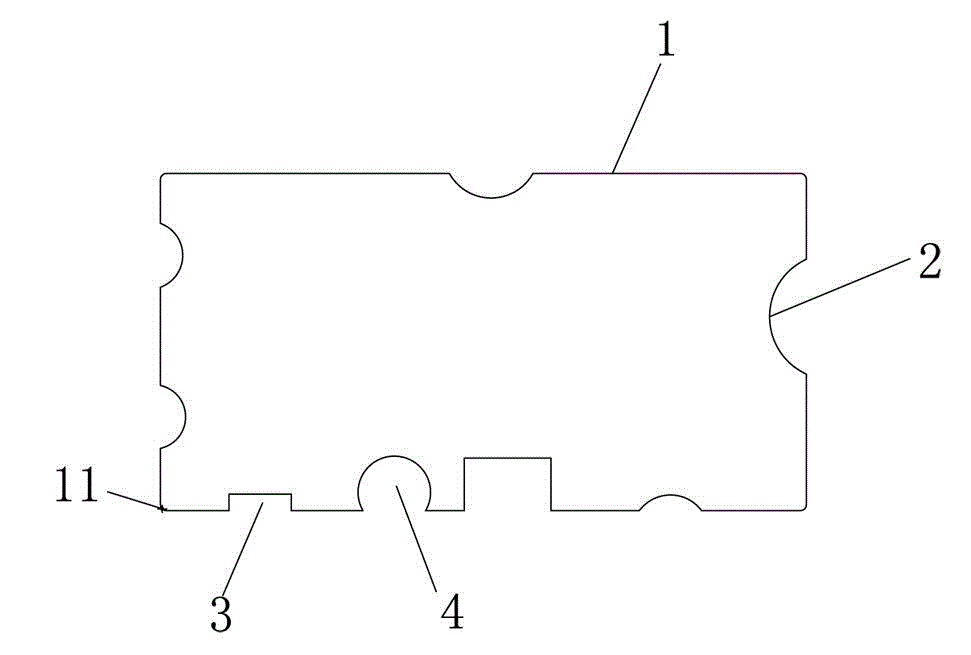

Circuit board profile process edge milling judgment method

ActiveCN104537176AImprove design efficiencyImprove accuracySpecial data processing applicationsRectangular coordinatesComputer science

The invention relates to the field of circuit board manufacturing, and provides a circuit board profile process edge milling judgment method. Before a profile graph is designed, a zero point is set, and a rectangular coordinate system is built so as to guarantee that all profile frame lines are horizontal or vertical; the profile graph designed by a client is stored in the form of a multi-level hash table, and a circle center coordinate is stored if the profile is in an arc shape; traversal is conducted on the hash table in a circulation mode, and results for judging whether partial process edge milling need to be conducted on the two ends of all the profile frame lines or not and for judging whether milling needs to be conducted towards side edges at the same time or not in the milling process are obtained; line segments are connected together according to the judging results of the two ends of all the profile frame lines to form a designed profile closed graph required by production. The circuit board profile process edge milling judgment method has the advantages of being fast, automatic, accurate and the like.

Owner:HUIZHOU KING BROTHER CIRCUIT TECH +2

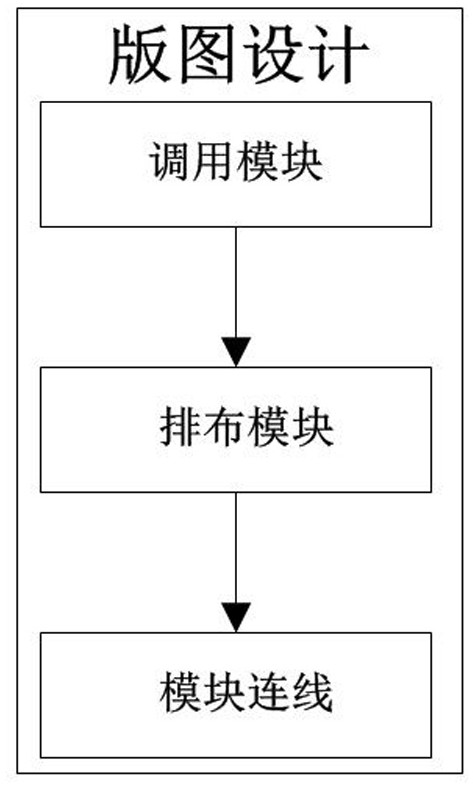

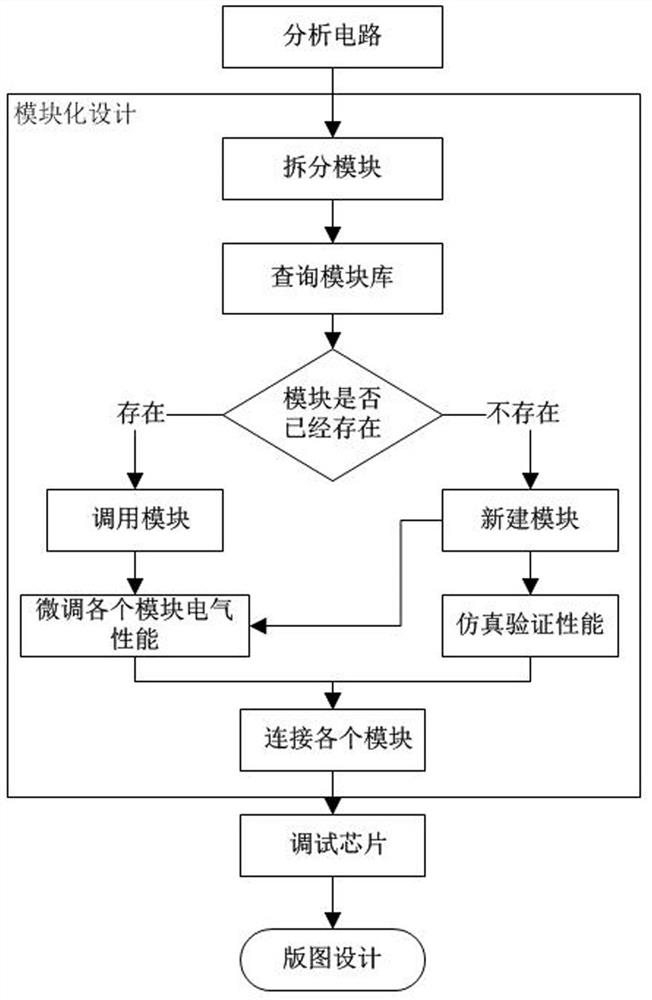

Auxiliary chip design method for reducing simulation time

ActiveCN112507657ADesign fasterSignificantly progressiveCAD circuit designSpecial data processing applicationsReference modelingSoftware engineering

The invention discloses an auxiliary chip design method for reducing simulation time. The method comprises the following steps: firstly, establishing a standard element library; establishing a reference model of the analog integrated circuit according to function classification, wherein the reference model comprises element library information of automatic calling and combined connection, a parameter filling space and a part of blank modules needing to be manually designed; selecting a reference model in a development tool according to required functions, filling in parameters, generating a schematic diagram top layer circuit, each module sub-circuit and a form required by module verification, and importing the schematic diagram top layer circuit, each module sub-circuit and the form intoa schematic diagram editor to complete schematic diagram design; and finally, importing a layout design tool, calling the corresponding layout and drawing layout in the standard element library, and verifying, integrating and completely drawing. By applying the method provided by the invention, the consumed time caused by layout rearrangement due to schematic diagram adjustment can be reduced, meanwhile, the simulation time required by most module function verification is also reduced, and the chip design speed is greatly increased.

Owner:SUZHOU BATELAB MICROELECTRONICS

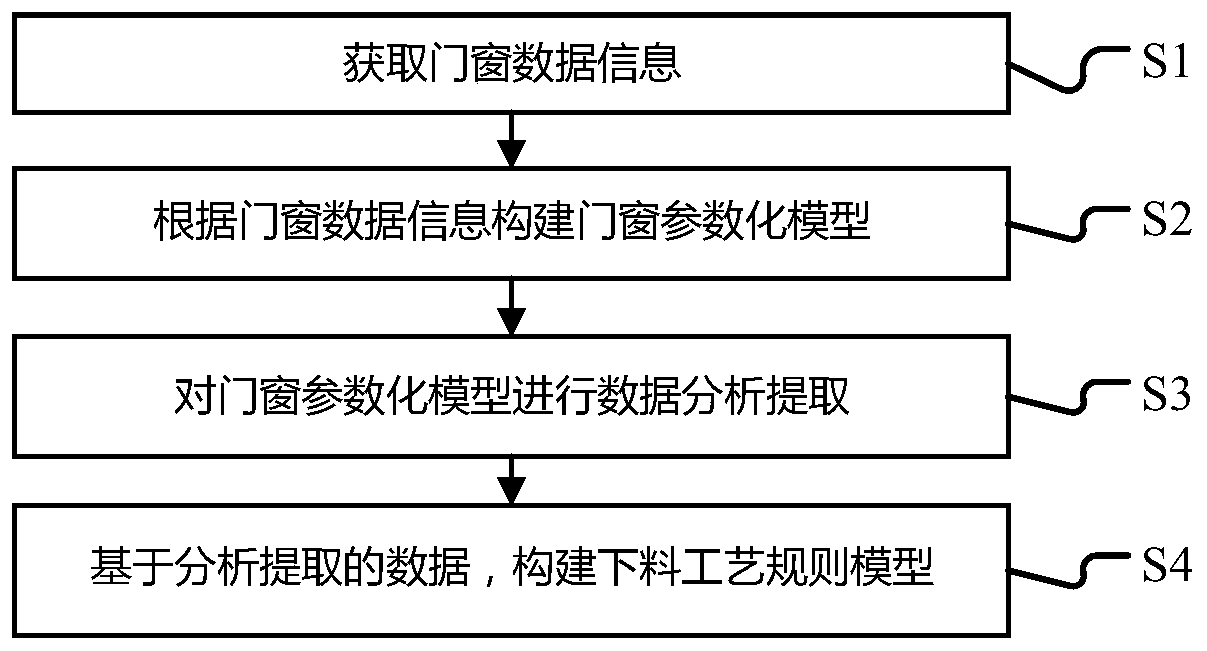

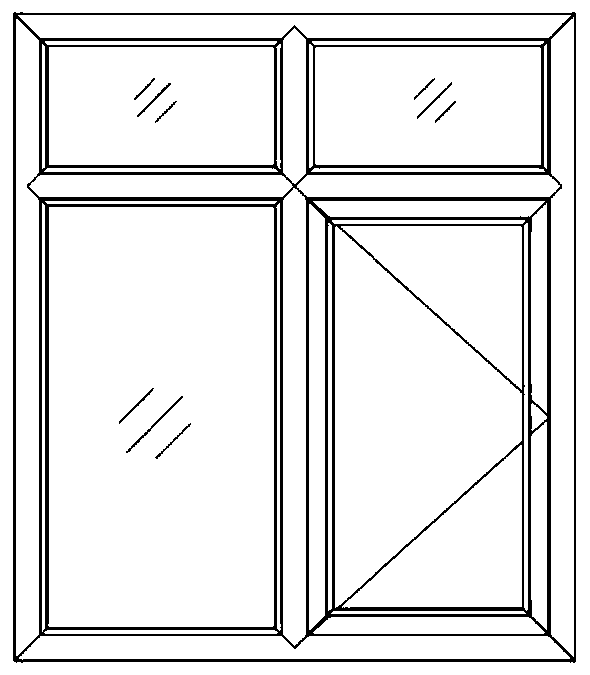

Door and window design and process planning integration method and system, server and readable storage medium

ActiveCN110334447AShorten the design cycleEnhanced data management toolsDesign optimisation/simulationSpecial data processing applicationsGraphicsInteractive design

The invention provides a door and window design and process planning integration method and system, a server and a readable storage medium. The method comprises: acquiring door and window data information; constructing a door and window parameterization model according to the door and window data information; performing data analysis and extraction on the door and window parameterized model; and constructing a blanking process rule model based on the analyzed and extracted data. The door and window design and the data management system are integrated, and the problems of information repetitionand poor data consistency of users are avoided. The door and window graph design efficiency is improved, the requirement for interactive design of door and window graphs can be met, and the design requirement for various door and window graphs can be met; the integration level of a door and window system is improved, planning of a door and window discharging process rule during interactive designis met, and the discharging process rule can be directly driven by the design size to generate a discharging result; the integration and sharing of data are improved, effective product data can be provided for ERP and the like, and the data island phenomenon of a process planning system is avoided.

Owner:UNIV OF JINAN

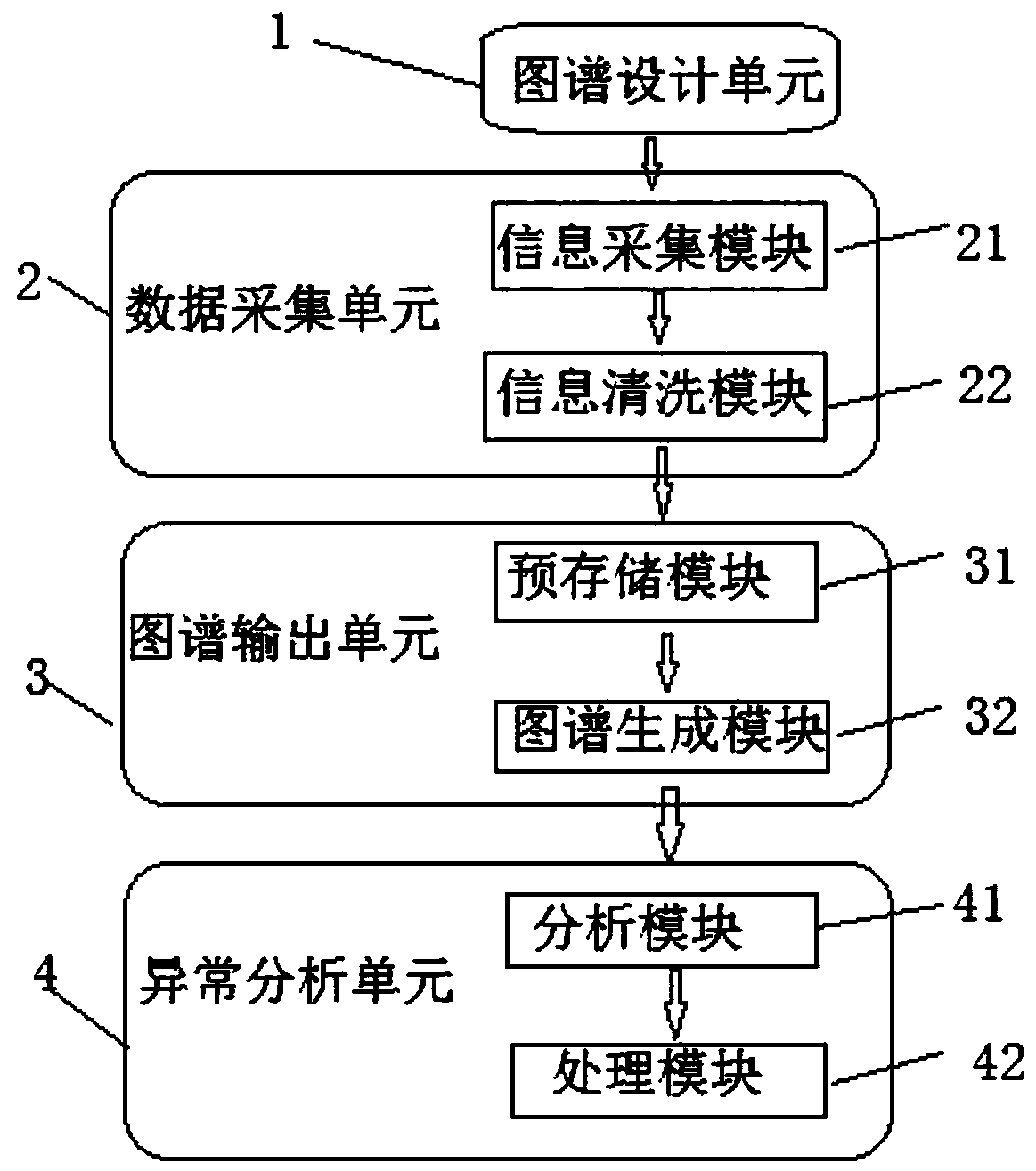

Financial knowledge graph visual query and multi-dimensional analysis system

PendingCN110837538AAvoid asset lossReduce bad debt rateFinanceVisual data miningEngineeringKnowledge graph

The invention provides a financial knowledge graph visual query and multi-dimensional analysis system. The financial knowledge graph visual query and multi-dimensional analysis system comprises a graph design unit used for designing the structure of a graph database according to the query requirement of financial data; a data acquisition unit used for acquiring a plurality of unstructured sample source data, cleaning the sample source data, and storing the cleaned sample source data into the atlas database as sample data; an atlas output unit used for importing the sample data into the atlas database to output a knowledge atlas; and an exception analysis unit used for extracting exception data from the knowledge graph and carrying out multi-dimensional analysis according to exception attributes. The method has the beneficial effects that the method is used for auditing the loan application client in financial loan business, and fraud behaviors can be avoided to a great extent, so thatthe bad debt rate of a financial platform can be reduced, and asset loss of the financial platform is avoided.

Owner:北京中科捷信信息技术有限公司

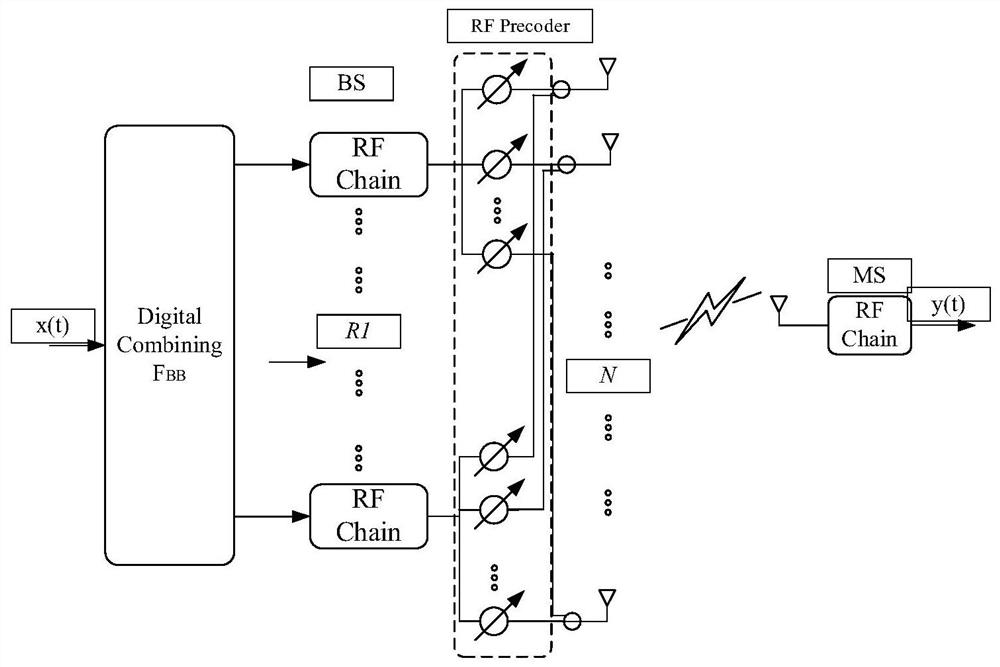

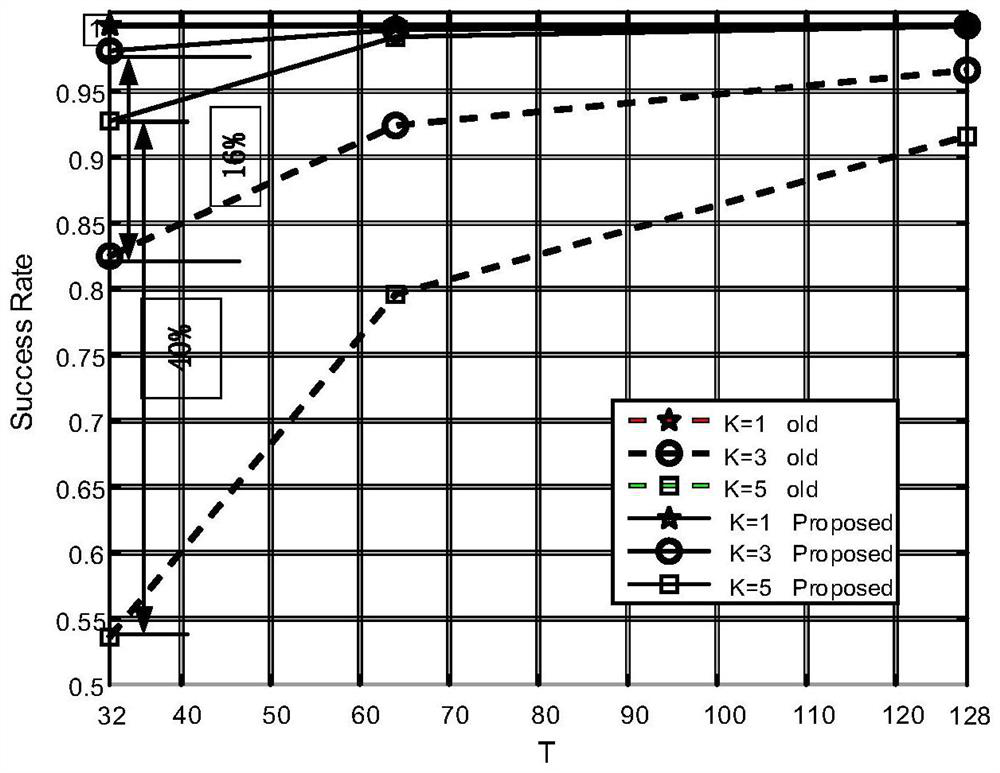

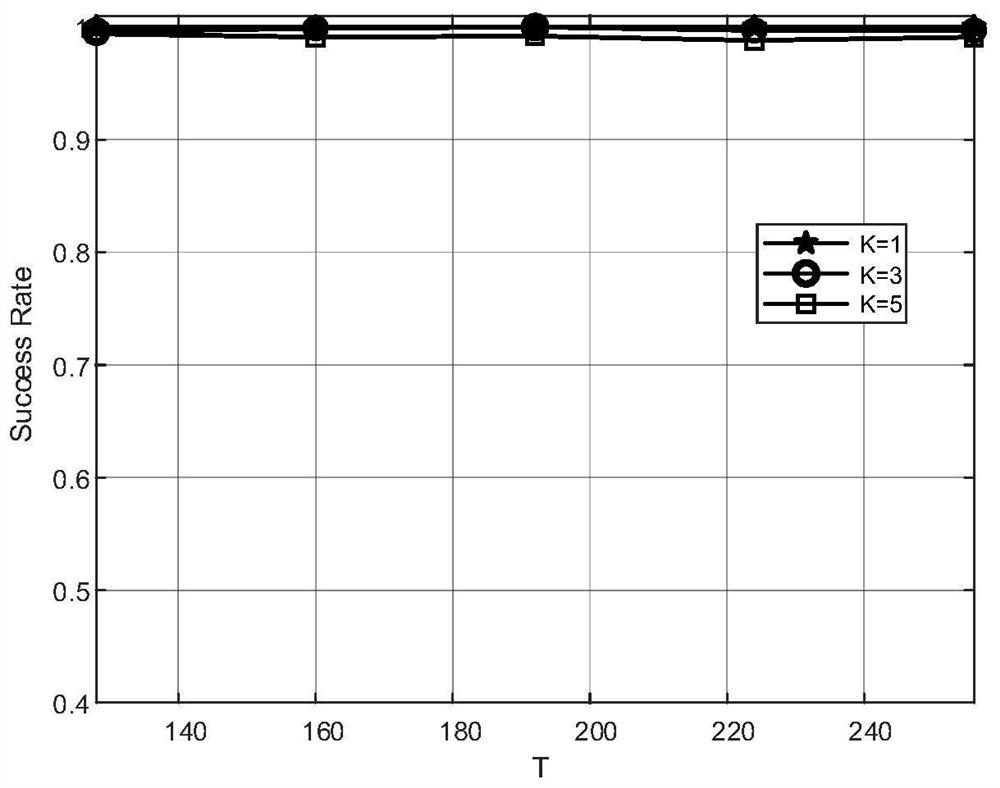

Millimeter wave beam alignment method based on sparse coding

ActiveCN112543044AFacilitate FPGA implementationEasy to implementSpatial transmit diversityLink dataMillimetre wave

The invention belongs to the technical field of millimeter wave communication, and particularly relates to a millimeter wave beam alignment method based on sparse coding. 1, a transmitting precoding matrix of a transmitting end and a receiving precoding matrix of a receiving end are reasonably designed, a plurality of wave beams are formed at the transmitting end and the receiving end at the sametime, and then independent link data are selected. In this way, a beam alignment problem is converted into a sparse coding and decoding problem. 2, the measurement matrix is divided into two parts, the two parts are respectively designed, namely a sparse graph design and an identification matrix design, and the minimum graph row number is defined through a theoretical lower limit table obtained byderivation; experimental results show that the proposed algorithm is simpler and easier to implement than a traditional method based on compressed sensing, and it can also be proved that the proposedmethod is superior to a traditional beam alignment method based on sparse coding and has robustness for different antenna numbers.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

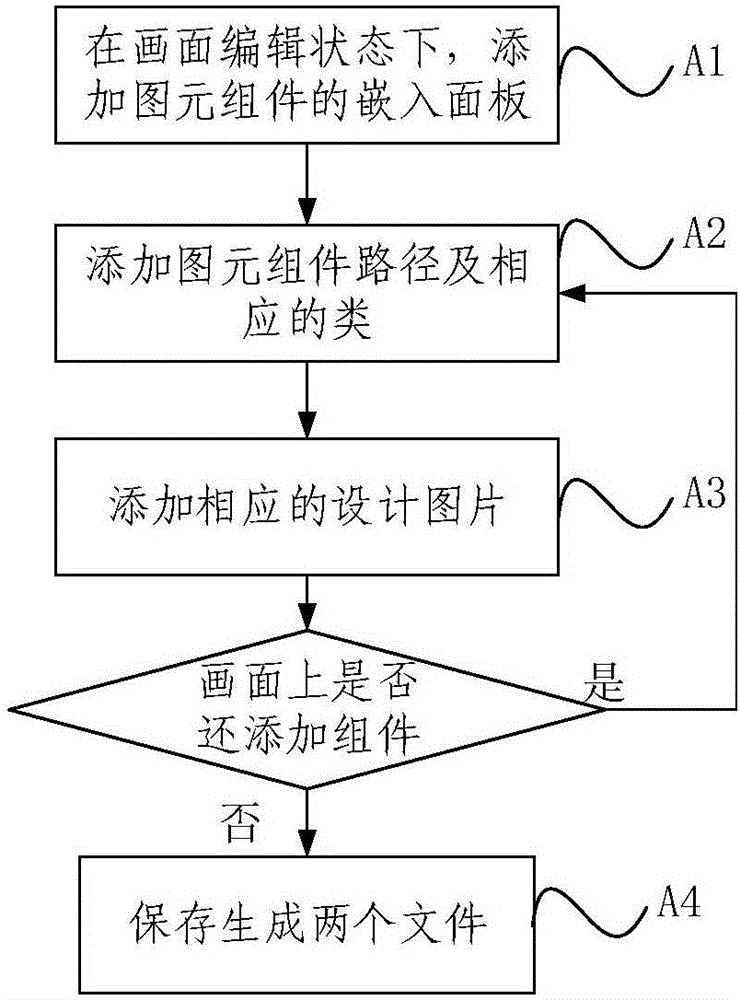

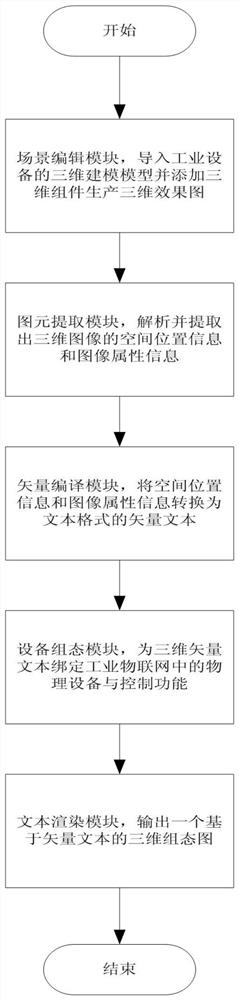

Three-dimensional configuration diagram design system and method

InactiveCN112288860ARealize automatic controlAdd dimensionVectoral format still image dataSpecial data processing applicationsSoftware engineeringIndustrial Internet

The invention relates to the technical field of three-dimensional display, in particular to a three-dimensional configuration diagram design, which comprises a scene editing module, a primitive extraction module, a vector compiling module, an equipment configuration module and a text rendering module, and space position information and image attribute information extracted from a three-dimensionaleffect diagram established by a user are subjected to vector compiling; a three-dimensional vector text is generated through conversion, physical equipment and a control function in the industrial Internet of Things are bound to form a three-dimensional configuration graph, the purpose that a user automatically controls industrial Internet of Things equipment according to any configuration of a control object and a control purpose of the user is achieved, and the method is applied to design of the three-dimensional configuration graph of the industrial Internet of Things equipment.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

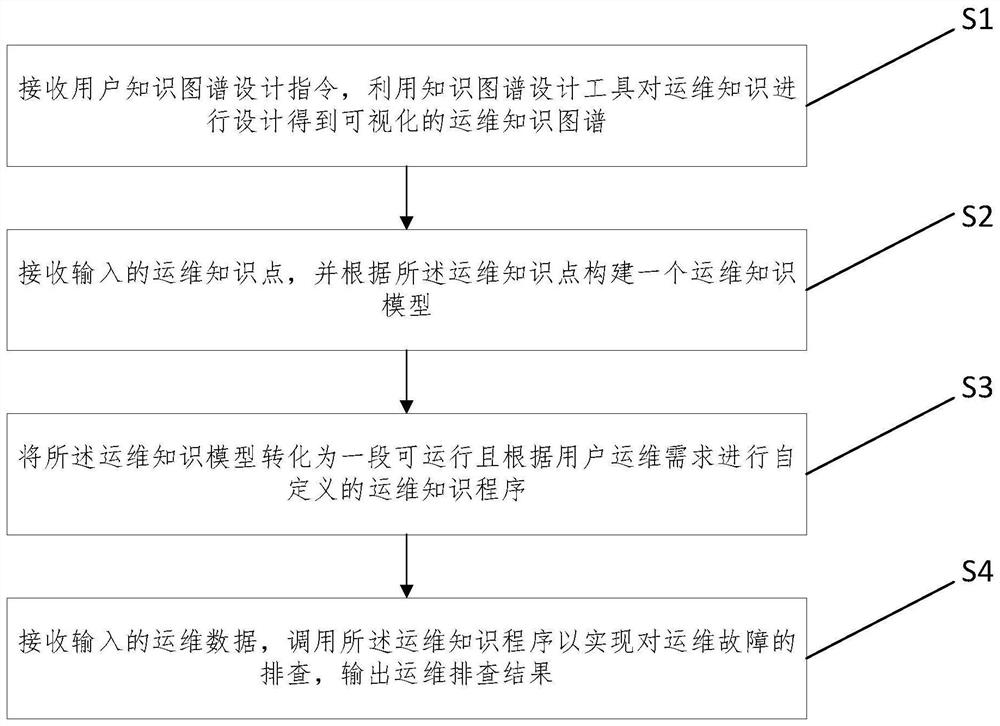

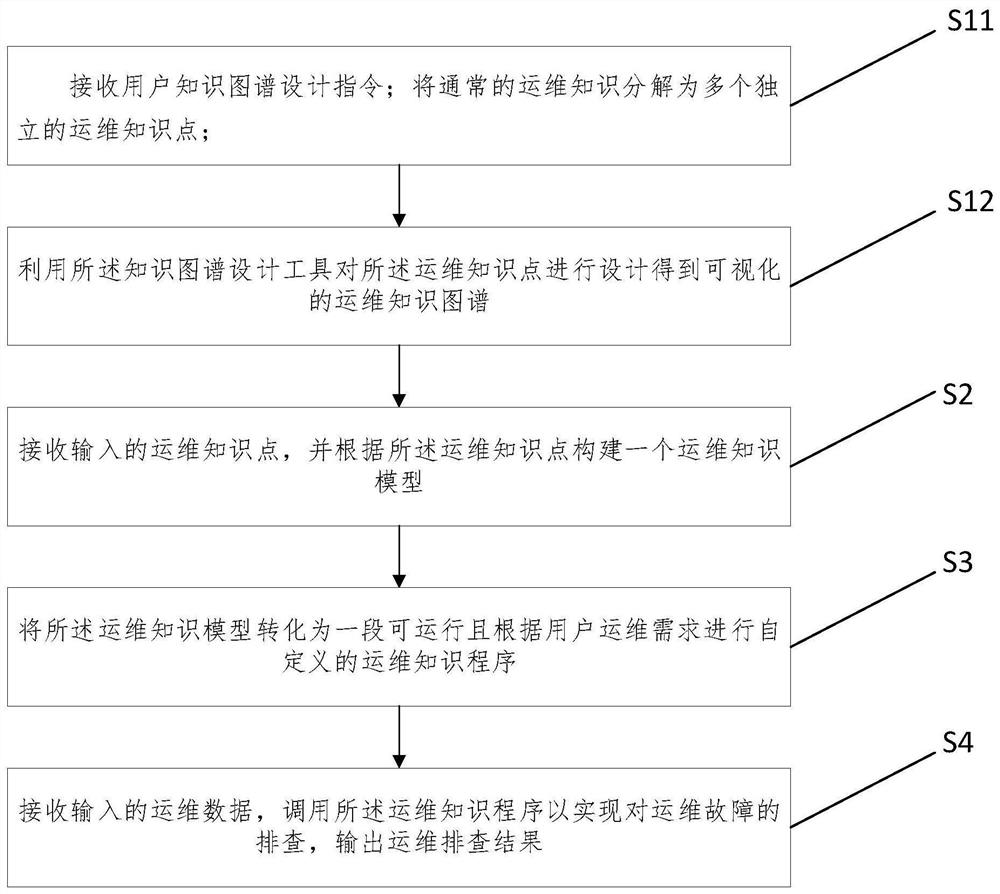

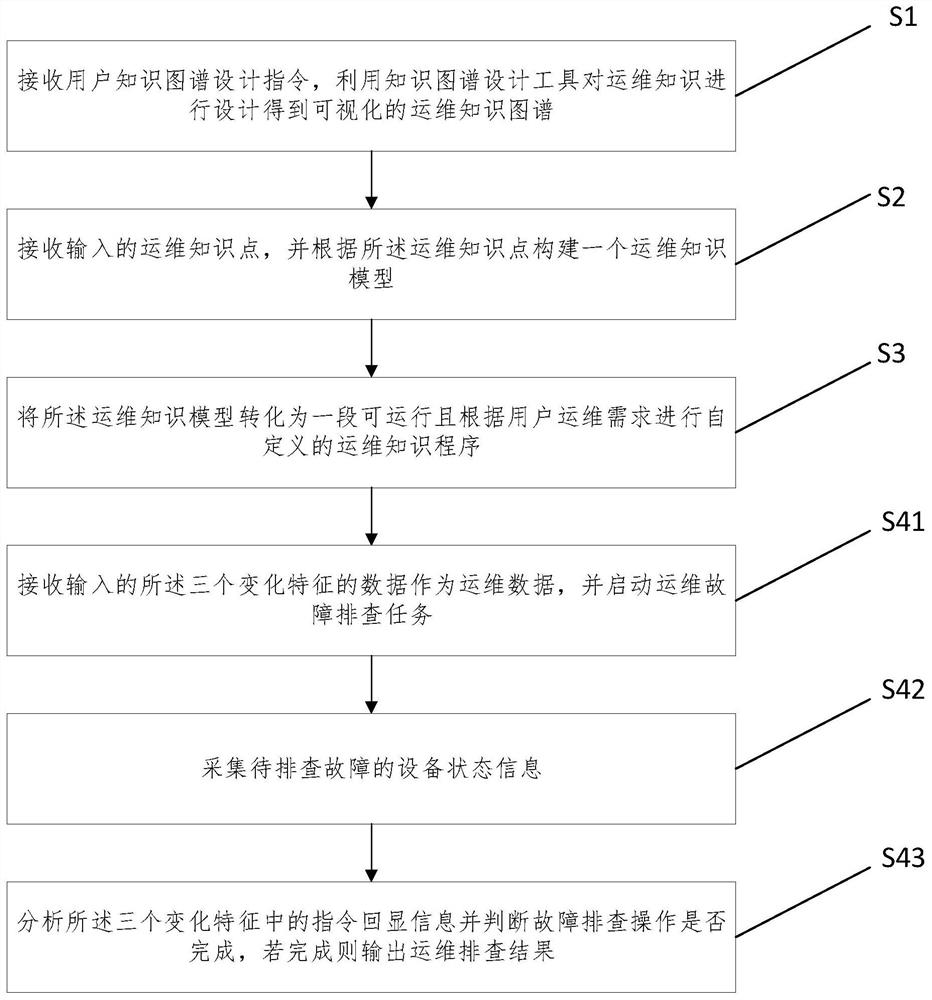

Operation and maintenance troubleshooting implementation method and device, medium and equipment

PendingCN112348213ARealize visualizationAchieve solidificationSpecial data processing applicationsSemantic tool creationDaily operationKnowledge graph

The invention relates to the technical field of operation and maintenance monitoring, and provides an operation and maintenance troubleshooting implementation method and device, a medium and equipment, and the method comprises the steps: receiving a user knowledge graph design instruction, and carrying out the design of operation and maintenance knowledge through a knowledge graph design tool, andobtaining a visual operation and maintenance knowledge graph; receiving input operation and maintenance knowledge points, and constructing an operation and maintenance knowledge model according to the operation and maintenance knowledge points; converting the operation and maintenance knowledge model into an operation and maintenance knowledge program which can run and is self-defined according to operation and maintenance requirements of a user; and receiving input operation and maintenance data, calling the operation and maintenance knowledge program to realize troubleshooting of operationand maintenance faults, and outputting an operation and maintenance troubleshooting result. According to the operation and maintenance troubleshooting implementation method provided by the invention,a user can easily and quickly realize visualization and solidification of operation and maintenance knowledge, the operation and maintenance knowledge is automated, the operation and maintenance practical experience of the user is extracted and abstracted and then endowed to daily operation and maintenance work again, and the operation and maintenance efficiency is improved.

Owner:NEW H3C BIG DATA TECH CO LTD