Trigger signal synchronization system and method based on delay chain, and semiconductor test equipment

A technology of trigger signal and synchronization system, applied in computer-aided design, special data processing applications, instruments, etc., to optimize the synchronization test of trigger signal, avoid unusable, and solve the effect of complicated backplane wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

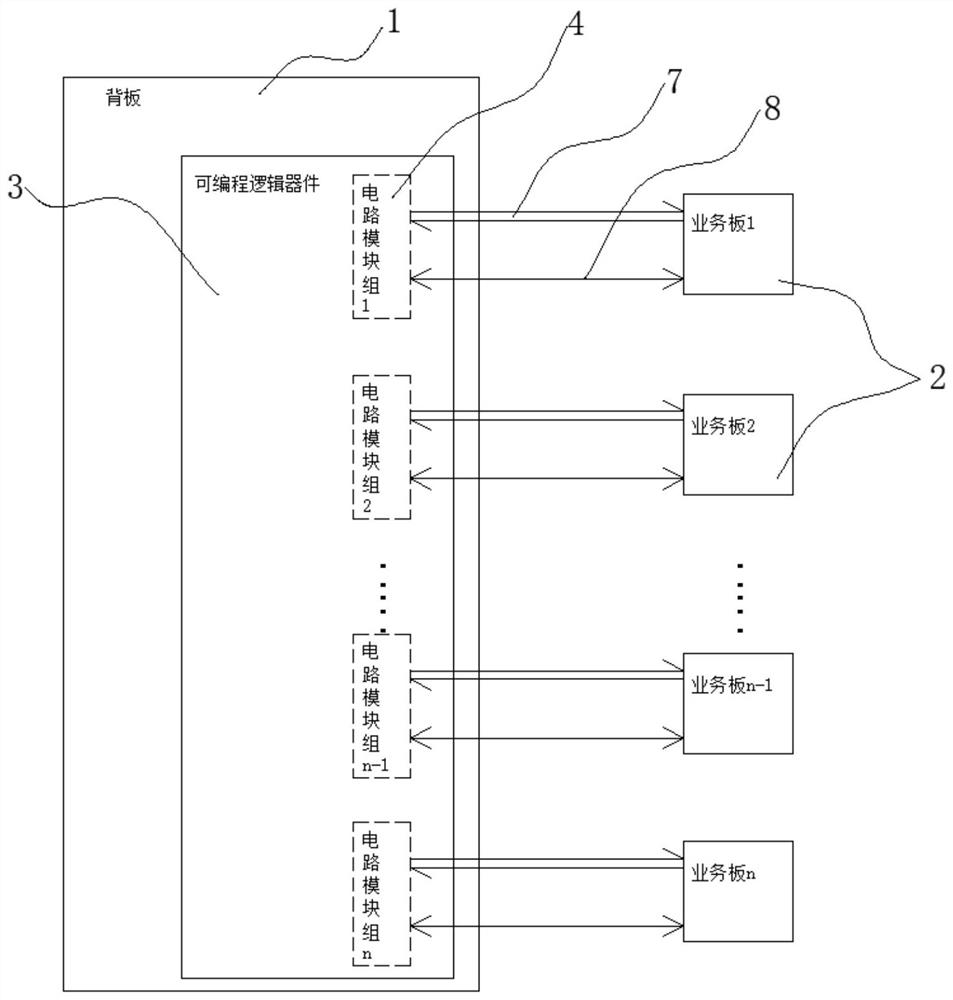

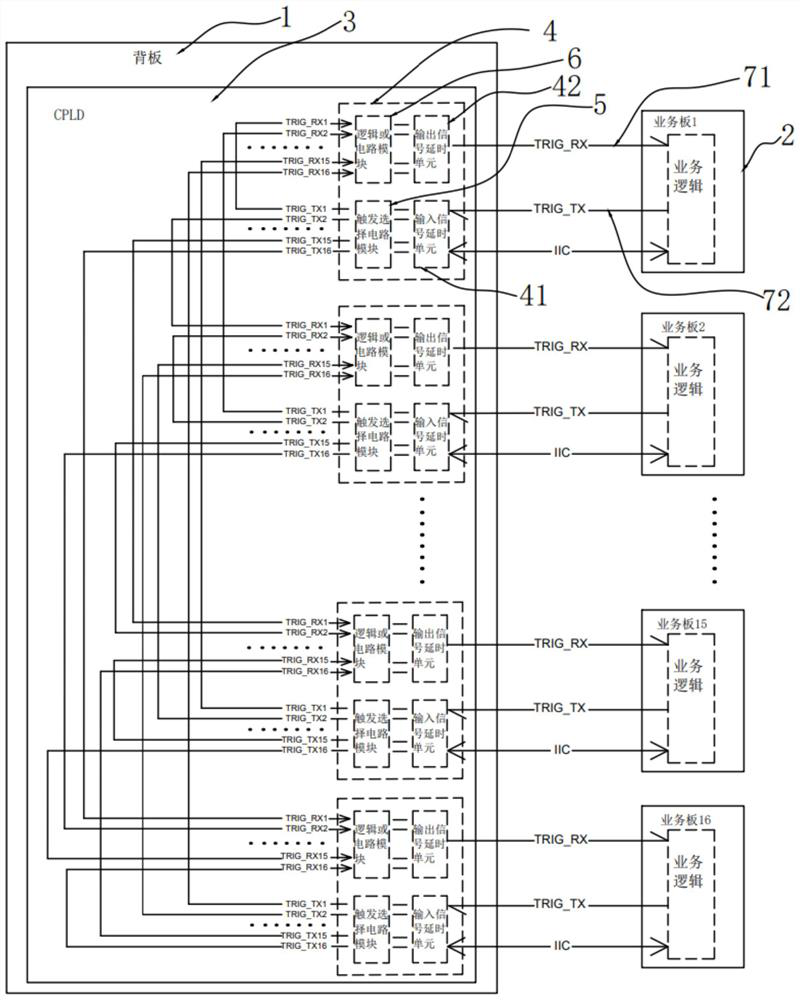

[0074] As attached to the manual figure 1 As shown, the trigger signal synchronization system based on the delay chain in a kind of ATE semiconductor test equipment provided by the present embodiment includes:

[0075] Backplane 1 and several service boards 2; service boards 2 are used to realize preset functions.

[0076] The backplane 1 is provided with a programmable logic device 3, and the programmable logic device 3 communicates with the service board 2 for receiving, processing and distributing the trigger signal with the service board 2, and the service board 2 transmits the trigger signal to the programmable The logic device 3, the programmable logic device 3 receives, processes and distributes the trigger signal transmitted by the service board 2.

[0077] In the programmable logic device 3 , the direction and transmission of signals can be realized through programming. Specifically, EDA tools can be used to perform equal-length layout and wiring to obtain the netli...

Embodiment 2

[0113] This embodiment also provides a trigger signal synchronization method for multi-service boards in ATE test equipment, which is used to synchronously select trigger signals between fan-out service boards 2, and is applicable to a system including a backplane and several service boards. The programmable logic device 3 communicates with each service board 2 . A programmable logic device is arranged on the backplane, and several circuit module groups are arranged inside the programmable logic device, and each circuit module group corresponds to each service board one by one and communicates with each other. The specific steps are attached in the manual Figure 9 As shown, the scheme is:

[0114] 101. Establish a communication connection between the backplane and each service board through a programmable logic device;

[0115] 102. Adjust the time for multiple circuit module groups to receive the trigger signal through the input signal delay unit 41, so as to realize that ...

Embodiment 3

[0132] This embodiment also provides a kind of semiconductor test equipment, based on the trigger signal synchronization method based on the delay chain in the above-mentioned ATE semiconductor test equipment, such as image 3 shown, including:

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com