Wafer semiconductor product, mask and photoetching machine

A semiconductor and mask technology, applied in the field of chip manufacturing technology, can solve the problems of increasing cost, reducing the number of dies, increasing the width of scribing lanes, etc., and achieving the effects of cost saving, increasing quantity, and reducing width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary and are intended to explain the present invention and should not be construed as limiting the present invention.

[0034] The invention provides a wafer semiconductor product. Compared with traditional wafer semiconductor products, the wafer semiconductor product can increase the number of dies under the same wafer area, thereby improving die production efficiency and reducing costs.

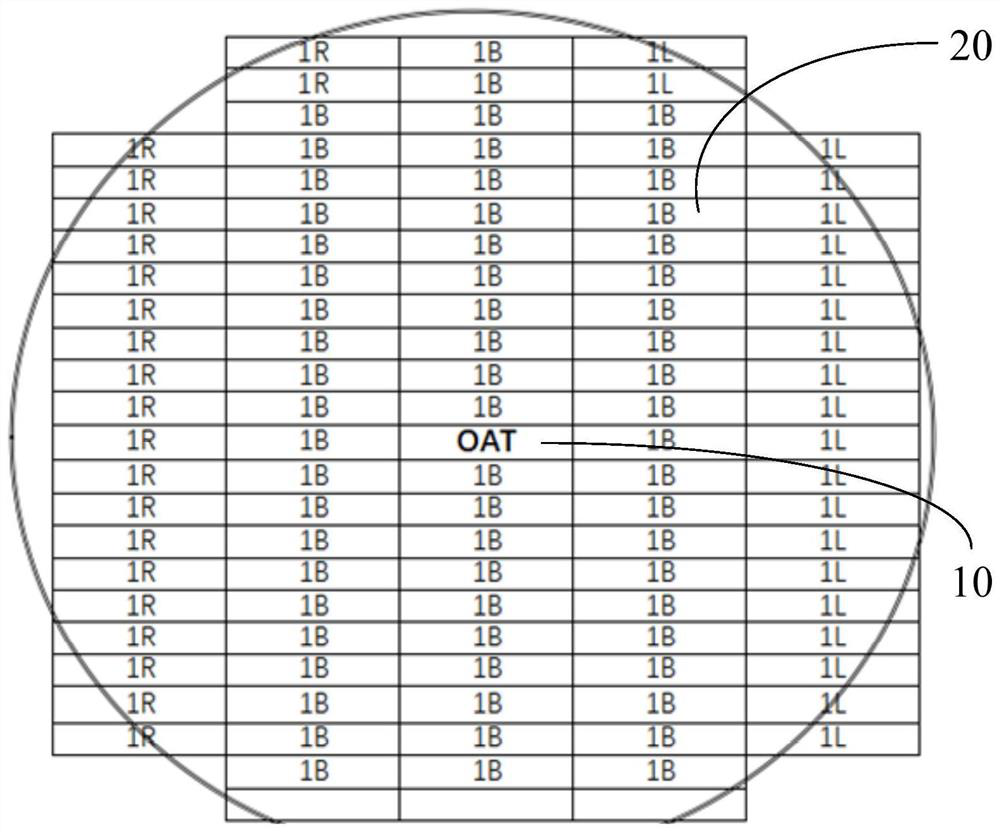

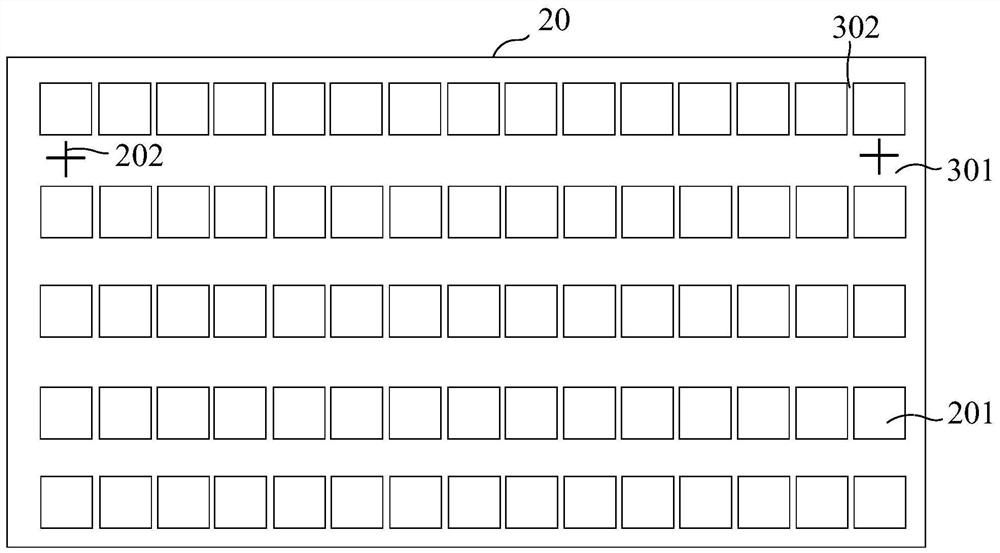

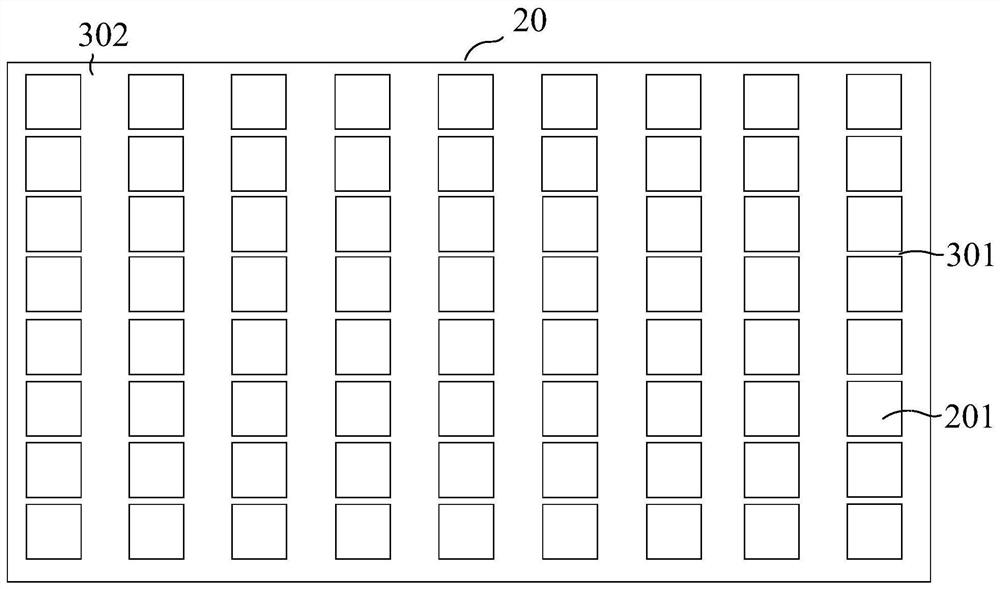

[0035] figure 1 It is a structural schematic diagram of an optical alignment field and a die exposure field of a wafer semiconductor product according to an embodiment of the present invention, and the wafer semiconductor product includes an optical alignment f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More