Silicon on insulator (SOI)-based GaN wafer and preparation method thereof

A wafer and growth method technology, applied in the field of SOI-based GaN wafers and their preparation, can solve the problems of inability to prepare low-defect density, large-size GaN wafers, etc., and achieve the effect of avoiding excessive warping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] 1. Select the SOI substrate material with the following parameters, as shown in Table 1 below:

[0036] Table 1

[0037]

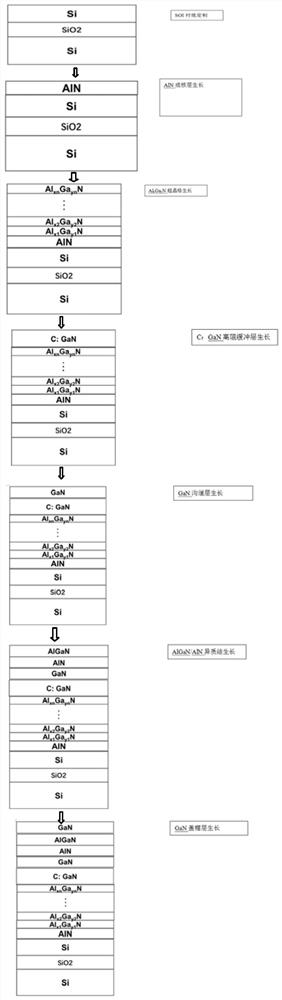

[0038] 2. Deposit sequentially on the SOI surface from bottom to top by MOCVD method, as shown in Table 2 below:

[0039] Table 2

[0040]

[0041] The specific preparation method of the GaN wafer: firstly, in the MOCVD chamber, the surface of the SOI wafer is pretreated with TMAl for 12-15s, the temperature is 1060°C, and the carrier gas is H 2 , the pressure is 100mbar, and then the material preparation method for growing each layer in turn is shown in Table 3 below:

[0042] table 3

[0043]

[0044] The specific measured performance parameters are shown in Table 4:

[0045] Table 4

[0046]

[0047] AlGaN barrier layer thickness 23.55nm (center) and 23.58nm (edge).

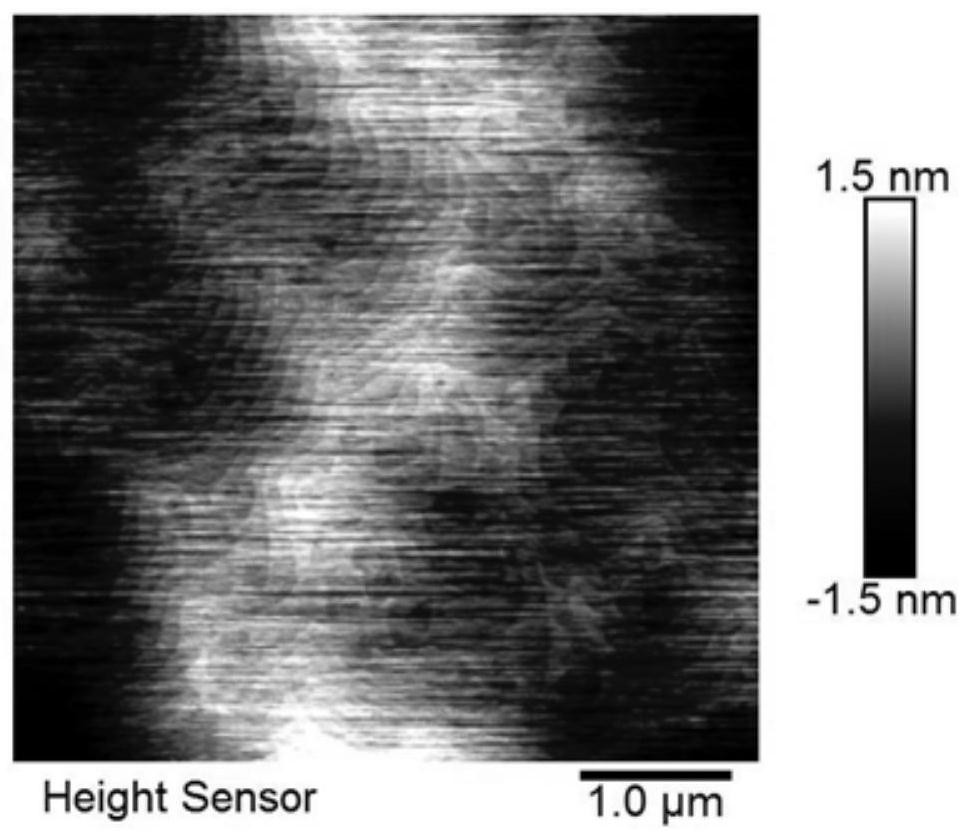

[0048] like figure 1 As shown, the structure shows that the roughness RMS is only 0.6nm;

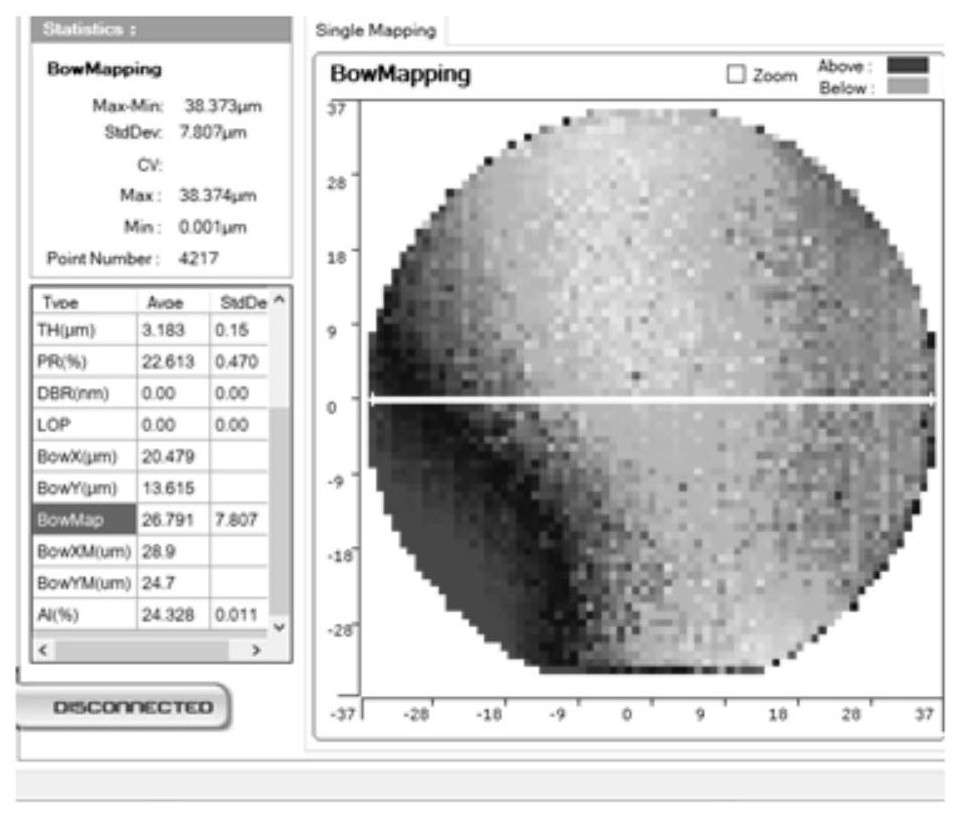

[0049] like figure 2 As shown, the results show that the warpage is...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More