Mask layout correction method and mask layout

A mask and layout technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of poor performance of semiconductor structures, and achieve the effects of improved performance, good shape, and high graphics accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] As mentioned in the background, the performance of existing semiconductor structures is still poor. Now analyze and illustrate in conjunction with specific embodiment.

[0050] It should be noted that the "surface" in this specification is used to describe the relative positional relationship in space, and is not limited to direct contact.

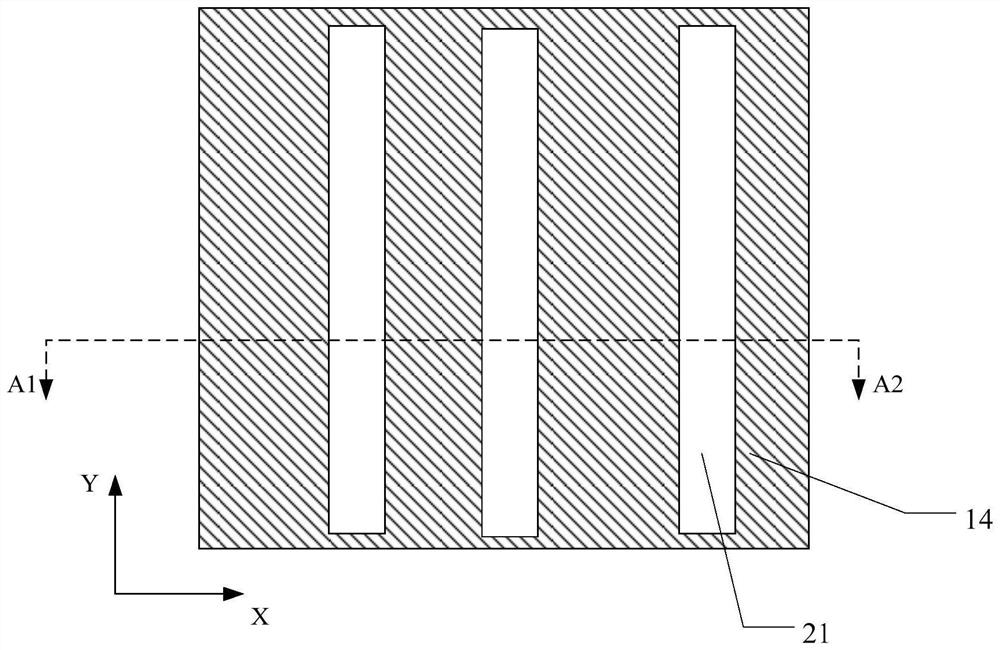

[0051] Figure 1 to Figure 11 It is a structural schematic diagram of each step in the formation process of a semiconductor structure.

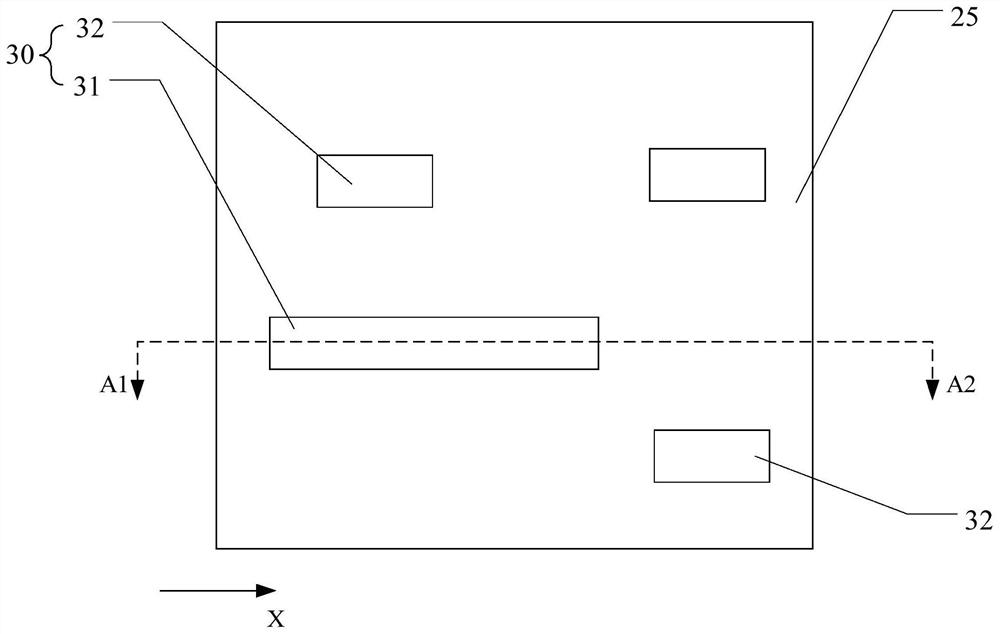

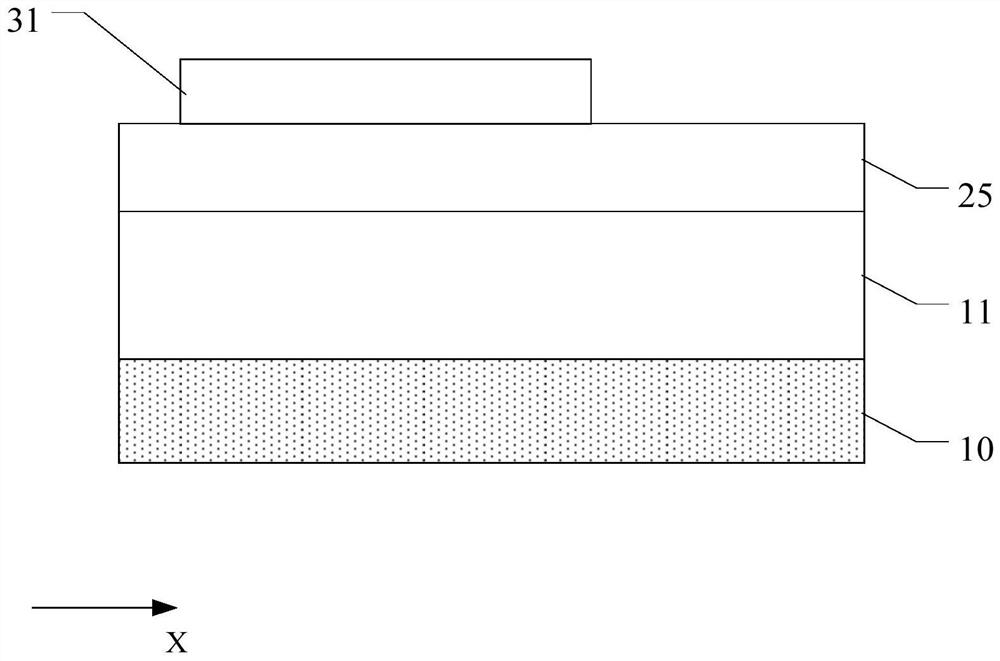

[0052] Please refer to Figure 1 to Figure 2 , figure 1 is a schematic top view of a semiconductor structure, figure 2 It is a schematic diagram of a cross-sectional structure along the A1-A2 direction in FIG. A cutting layer 30 is formed on the surface of the film material layer 25, and the cutting layer 30 includes a plurality of first strip structures 31 and second strip structures 32 extending along the first direction X. In the first direction X, the first The length of the strip struct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More