Multi-interface test system and method

A test system and interface test technology, applied in error detection/correction, detection of faulty computer hardware, instruments, etc., can solve complex problems, avoid interfering data, solve packet loss, and improve test efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

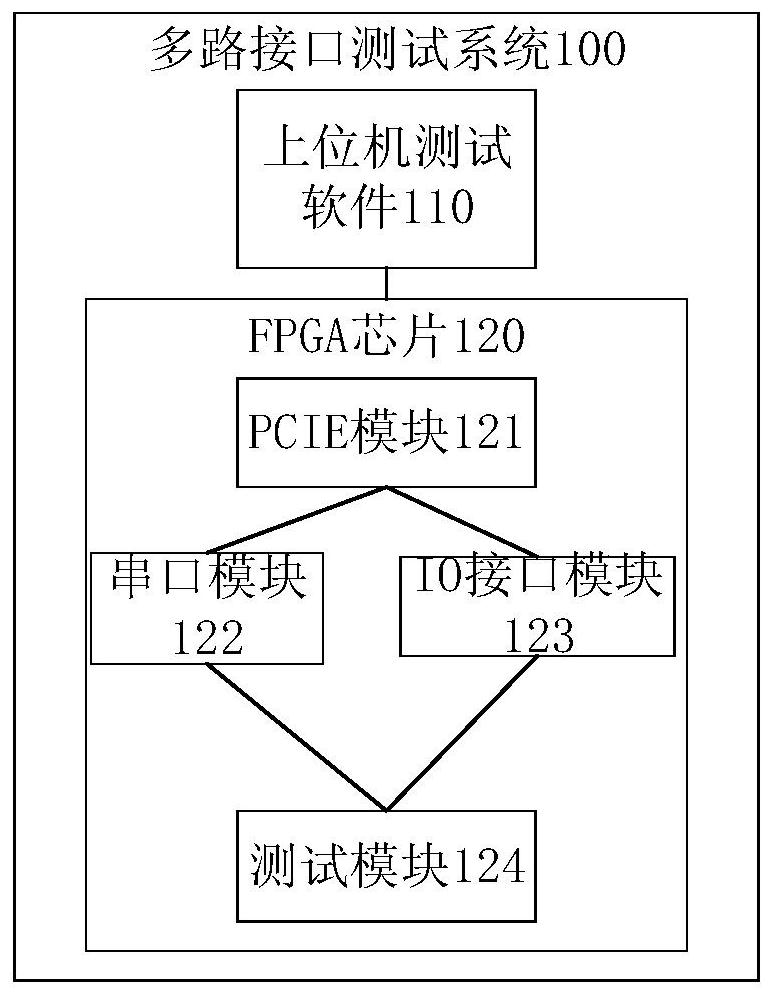

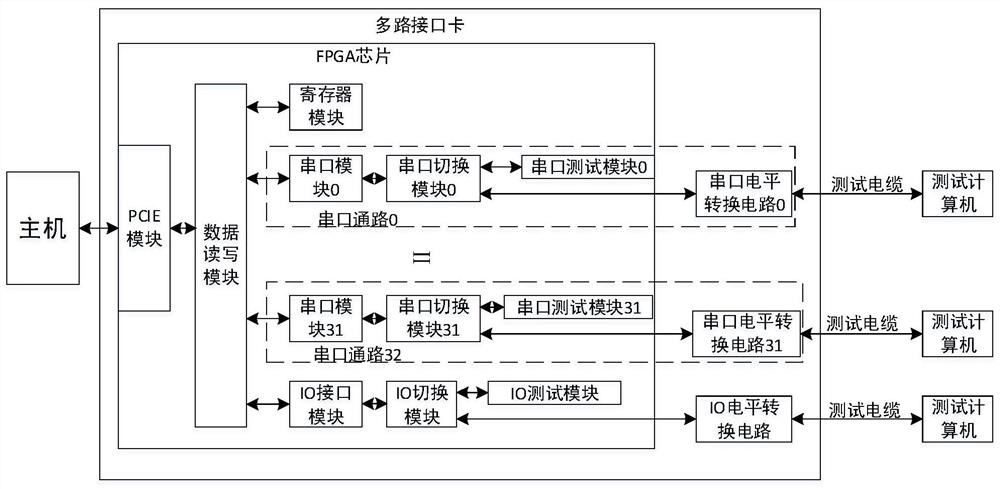

[0035] refer to figure 1 , which shows a schematic structural diagram of a multi-channel interface testing system provided by an embodiment of the present invention, as shown in figure 1 As shown, the multi-channel interface test system 100 can include: a host computer test software 110 and an FPGA chip 120, wherein the FPGA chip 120 can include: a PCIE (peripheral component interconnect express, high-speed serial computer expansion bus standard) module 121, a plurality of Serial port module 122, IO interface module 123 and test module 124, IO interface module 123 can comprise multi-channel IO interface,

[0036] The host computer test software 110 can be connected with the PCIE module 121 in communication, and the PCIE module 121 can be connected with the serial port module 122 and the IO interface module 123 respectively;

[0037] When carrying out the serial port test, the serial port module 122 can be connected with the serial port communication of the computer under test...

Embodiment 2

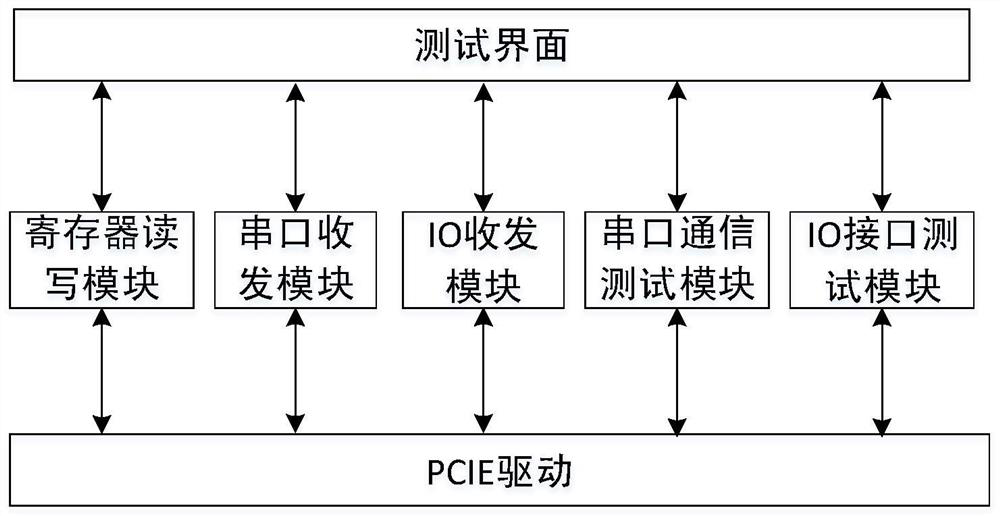

[0089] refer to Figure 4 , shows a flow chart of the steps of a multi-channel interface testing method provided by an embodiment of the present invention, as Figure 4 As shown, the multi-channel interface testing method may specifically include the following steps:

[0090] Step 401: When testing the multi-channel target interface, the host sets the register module to the test mode through the PCIE module, and the serial port switching module connects the corresponding multi-channel serial port module to the serial port test module, and connects the IO interface module to the IO test module.

[0091] The embodiment of the present invention can be applied in the scenario of testing serial ports and / or IO interfaces of multiple computers under test.

[0092] In this embodiment, the target interface may be a serial port and / or an IO interface.

[0093] When testing the multi-channel target interface, the host can set the register module as the test mode through the PCIE modul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More