Preparation method of fin type semiconductor device

A semiconductor and device technology, applied in the field of preparation of fin semiconductor devices, can solve the problems of poor flatness, affecting the working speed of the device, height difference, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

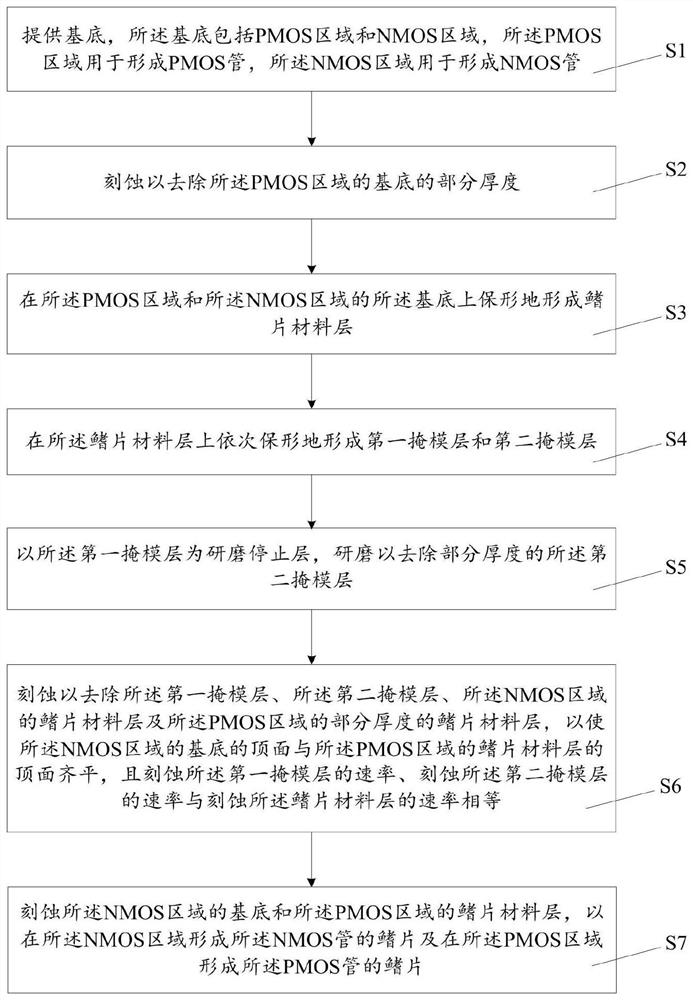

[0027] figure 1 A flow chart of the preparation method of the fin semiconductor device provided in this embodiment. This embodiment provides a method of preparing a fin semiconductor device to reduce the height difference of fins of the NMOS tube and the fins of the PMOS tube. Please refer to figure 1 The preparation method of the fins-type semiconductor device includes:

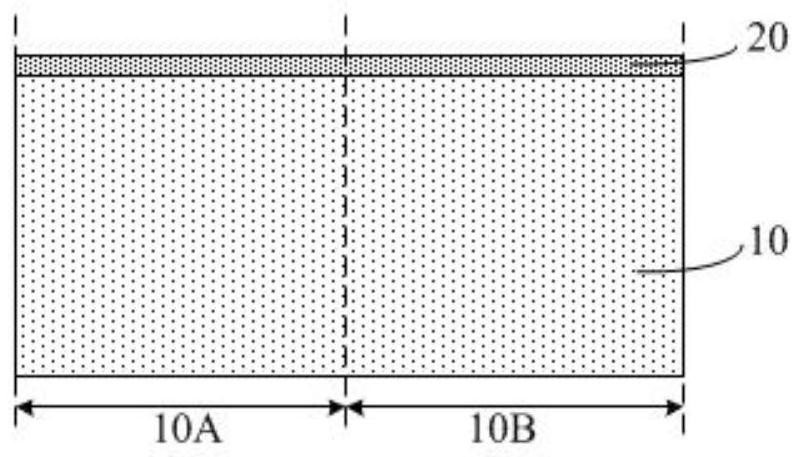

[0028] Step S1: Provides a substrate including a PMOS region and an NMOS region, the PMOS area for forming a PMOS tube, the NMOS region for forming an NMOS tube;

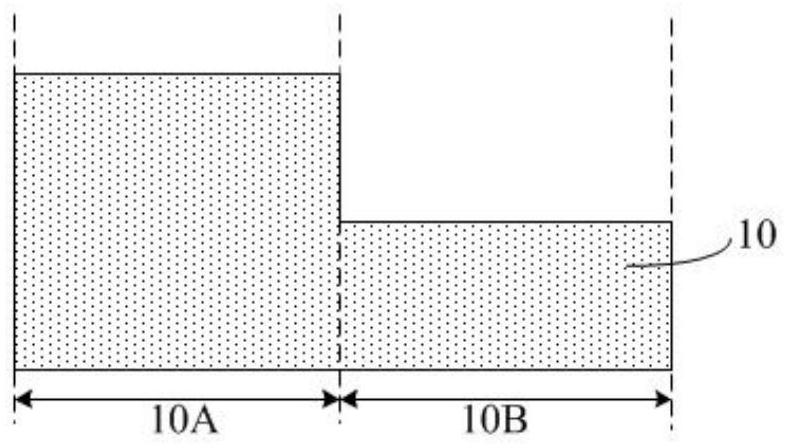

[0029] Step S2: Erochor to remove part of the substrate of the PMOS region;

[0030] Step S3: The fin material layer is protected on the substrate of the PMOS region and the NMOS region;

[0031] Step S4: The first mask layer and the second mask layer are sequentially formed on the fin material layer;

[0032] Step S5: The second mask layer of the partial thickness is removed by the first mask layer as a ground stop layer.

[0033] Step S6: Eroching ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More