Preparation method of fin type semiconductor device

A semiconductor and device technology, applied in the field of preparation of fin-type semiconductor devices, can solve problems such as poor surface flatness of germanium-silicon and silicon, affecting the working speed of devices, and surface damage of silicon and germanium-silicon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

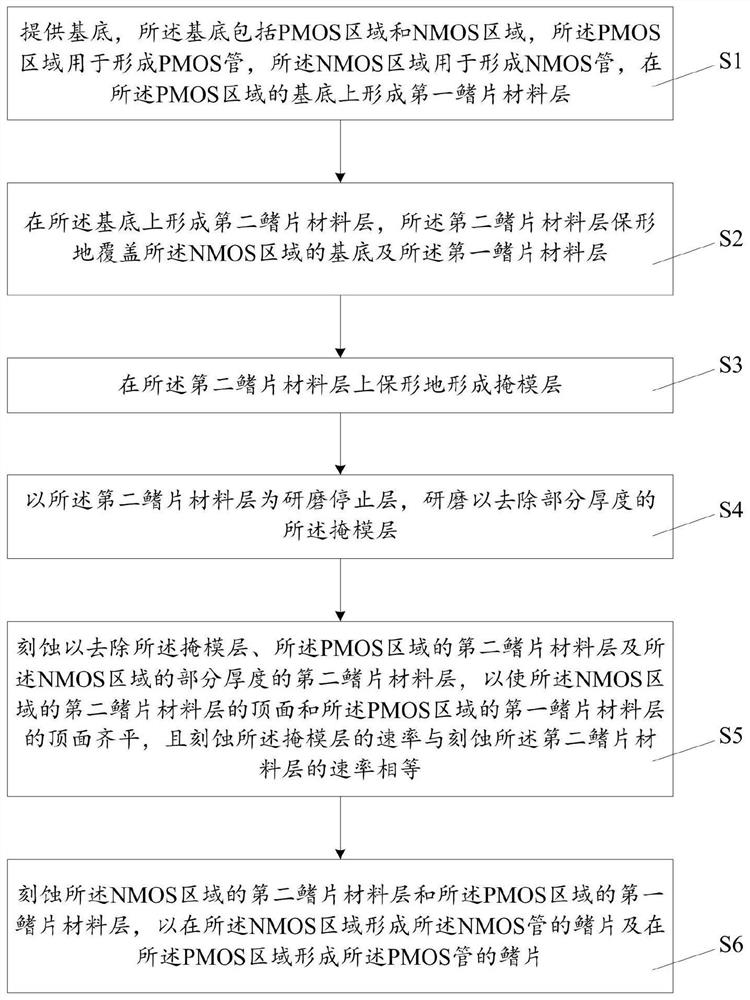

[0028] figure 1 It is a flow chart of the manufacturing method of the fin-type semiconductor device provided in this embodiment. This embodiment provides a method for manufacturing a fin-type semiconductor device, so as to reduce the height difference between the fins of the NMOS transistor and the fins of the PMOS transistor. Please refer to figure 1 , the preparation method of the fin semiconductor device includes:

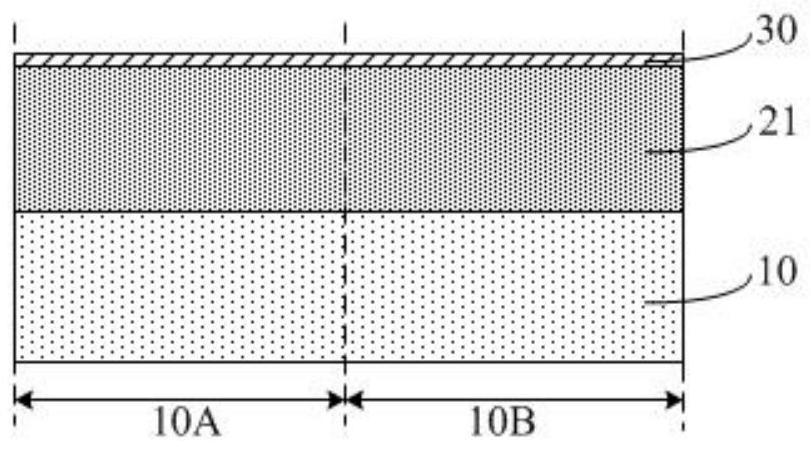

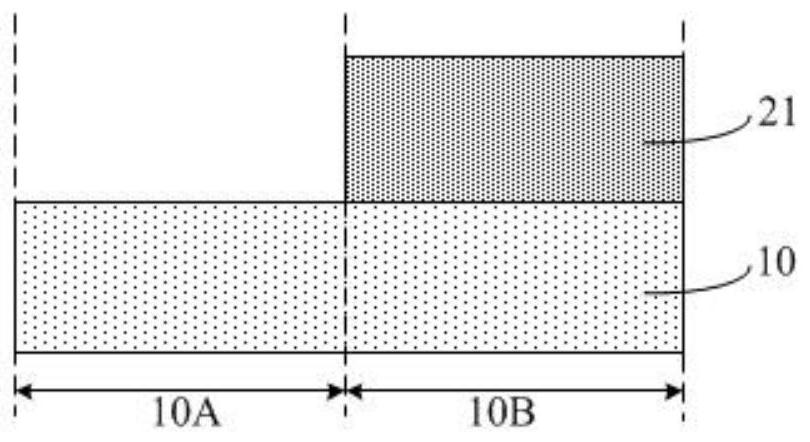

[0029] Step S1: providing a substrate, the substrate includes a PMOS region and an NMOS region, the PMOS region is used to form a PMOS transistor, the NMOS region is used to form an NMOS transistor, and a first fin material is formed on the substrate of the PMOS region layer;

[0030] Step S2: forming a second fin material layer on the base, the second fin material layer conformally covering the base of the NMOS region and the first fin material layer;

[0031] Step S3: conformally forming a mask layer on the second fin material layer;

[0032] Step S4: usi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More