Program running method supporting multi-instruction-set system structure, computer equipment and system

A program running and integrated system technology, applied in the direction of machine execution devices, register devices, etc., to achieve the effect of small implementation overhead, low hardware implementation overhead, correctness and speed guarantee

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

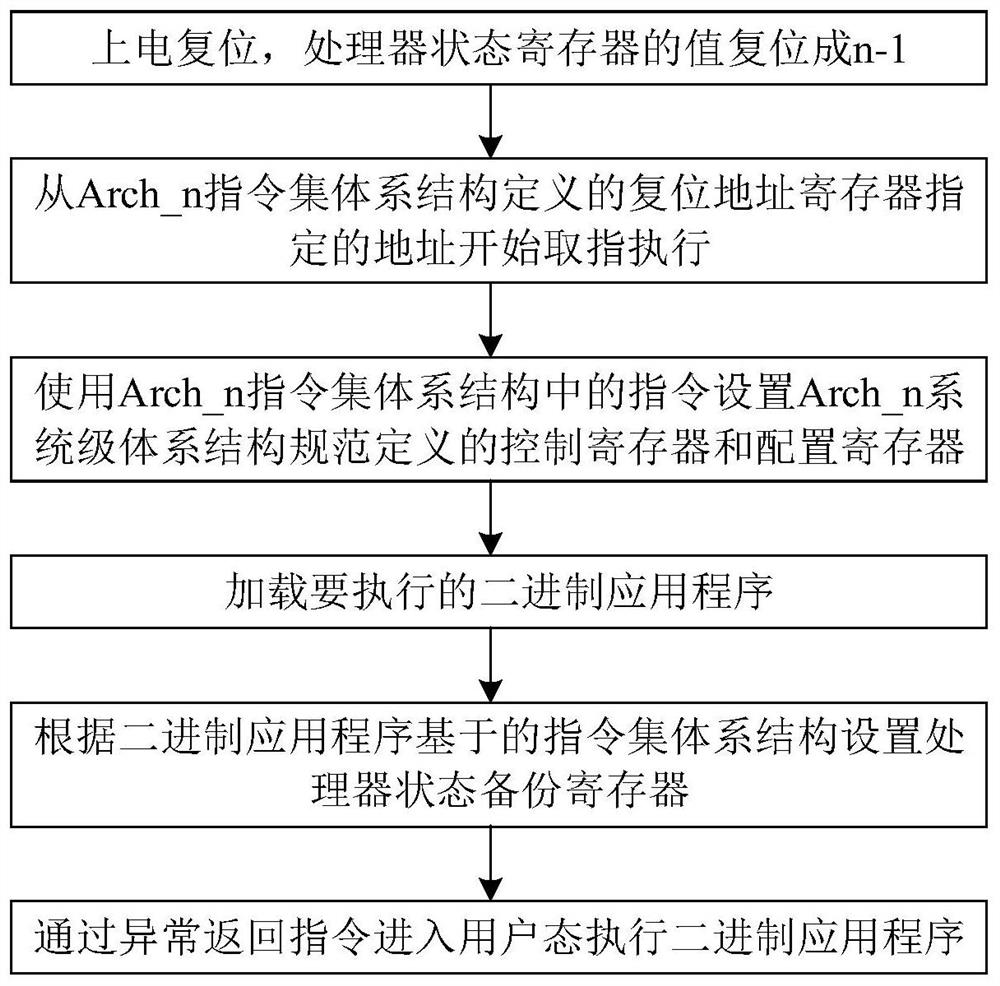

[0036] Such as figure 1 As shown, the program running method of this embodiment supporting multiple instruction set architecture (referred to as mArch) includes:

[0037] 1) After power-on reset, reset the processor status register to the encoding corresponding to the default instruction set architecture; see figure 1 , the various instruction set architectures in this embodiment are Arch_1, Arch_2, ..., Arch_N, wherein N>1; the default instruction set architecture is Arch_n, and the code corresponding to the default instruction set architecture is n-1.

[0038] 2) Start fetching instructions from the address specified by the reset address register defined by the default instruction set architecture;

[0039] 3) using the instructions in the default instruction set architecture, respectively setting the control registers and configuration registers defined by the specification of the default instruction set architecture;

[0040] 4) When the binary application program needs ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More