SONOS memory and preparation method thereof

A memory and shallow trench isolation technology, applied in the field of SONOS memory and its preparation, can solve the problem of small voltage threshold of SONOS memory, and achieve the effect of increasing the effective contact area and increasing the voltage threshold

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

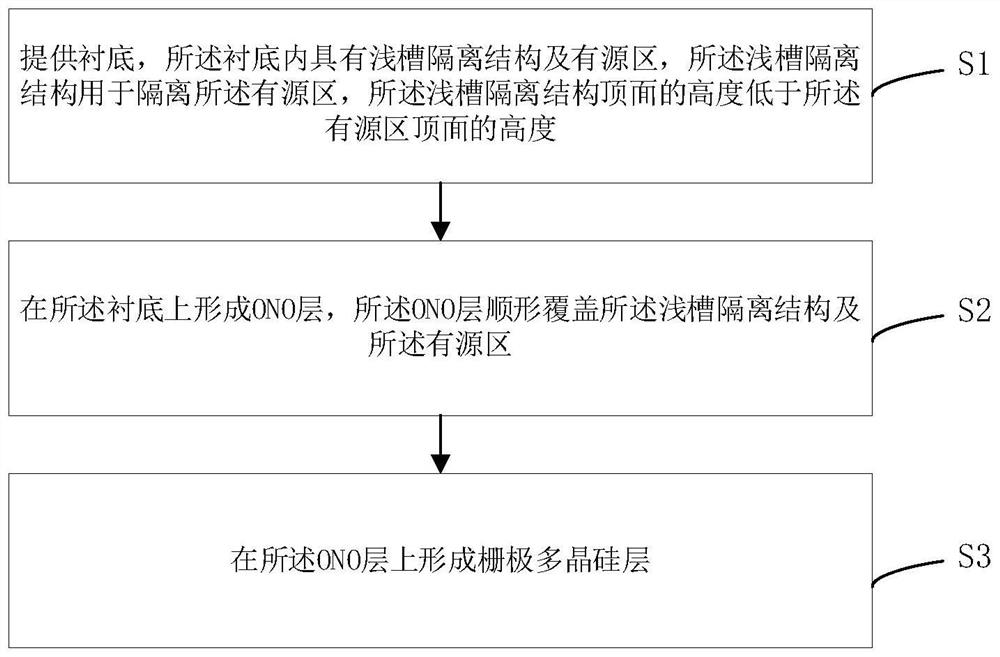

[0041] image 3 A flow chart of a method for preparing a SONOS memory provided in this embodiment, such as image 3 As shown, the invention provides a kind of preparation method of SONOS memory structure, comprising:

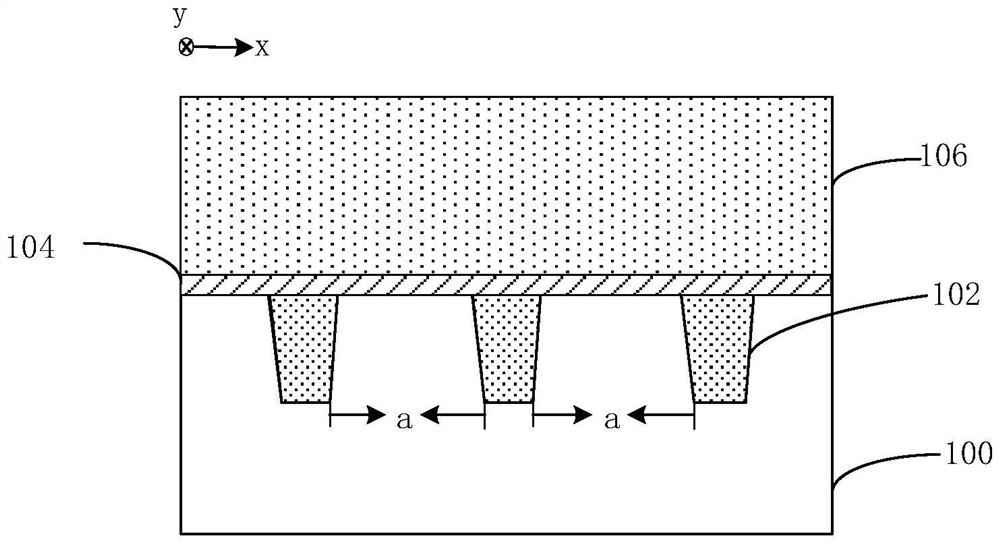

[0042] Step S1: providing a substrate, the substrate has a shallow trench isolation structure and an active region, the shallow trench isolation structure is used to isolate the active region, and the height of the top surface of the shallow trench isolation structure is lower than the height of the shallow trench isolation structure The height of the top surface of the active region;

[0043] Step S2: forming an ONO layer on the substrate, the ONO layer conformally covering the shallow trench isolation structure and the active region;

[0044] Step S3: forming a gate polysilicon layer on the ONO layer.

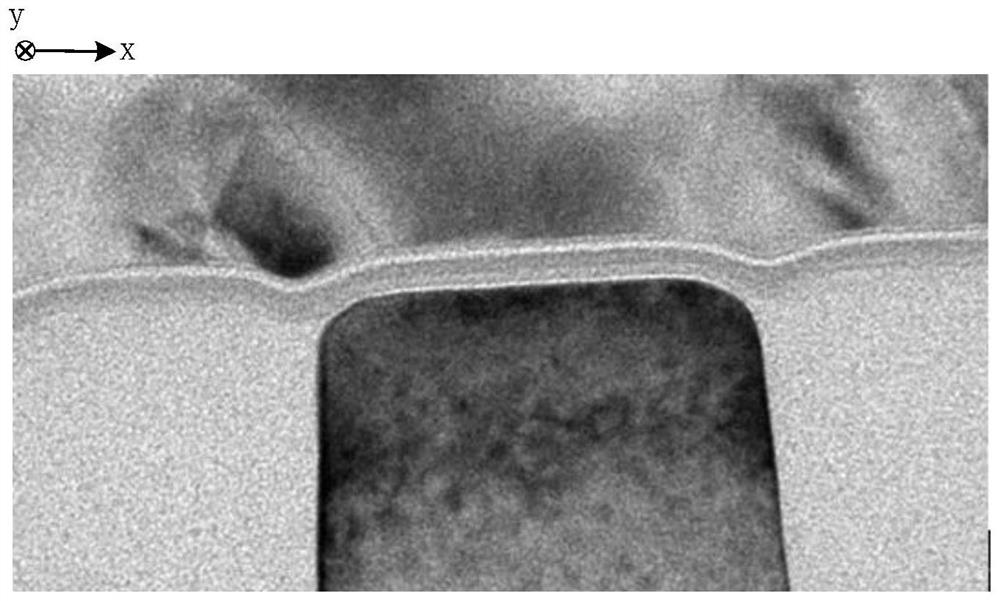

[0045] Figure 4a~4d A schematic structural diagram corresponding to the corresponding steps of the preparation method of a SONOS memory provided in this e...

Embodiment 2

[0057] Figure 7a~7b A schematic structural view of a method for preparing a SONOS memory provided in this embodiment, as Figure 7a As shown, the difference from Embodiment 1 is that in this embodiment, after the shallow trench isolation structure 202 is etched, the active region A is also etched, so that the top surface of the active region A is Wavy, sawtooth, or square.

[0058] For example, in this embodiment, the top surface of the active region A is zigzag, and in other optional embodiments, the top surface of the active region A can also be wave-shaped or square-shaped, etc. . Changing the shape of the top surface of the active region A is to increase the area of the top surface of the active region A, thereby increasing the effective contact area between the ONO layer 204 and the active region A, and increasing the SONOS memory voltage threshold.

[0059] Wherein, the active region A may be etched by a wet etching process or a dry etching process.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More