A device and method for accelerated aging reliability test of chip atomic clock

A chip atomic clock and accelerated aging technology, which is applied in the direction of adjustment devices, clocks, clocks, etc., can solve the problems of high cost and low efficiency of reliability testing, and achieve the effect of saving material costs, saving test time costs, and improving detection efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

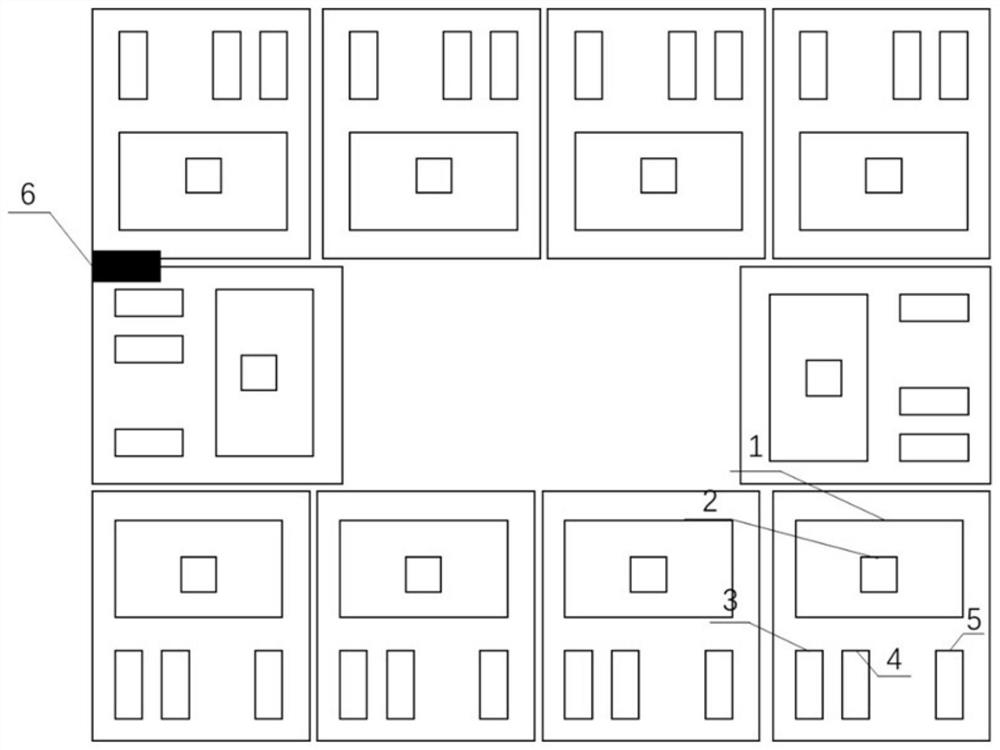

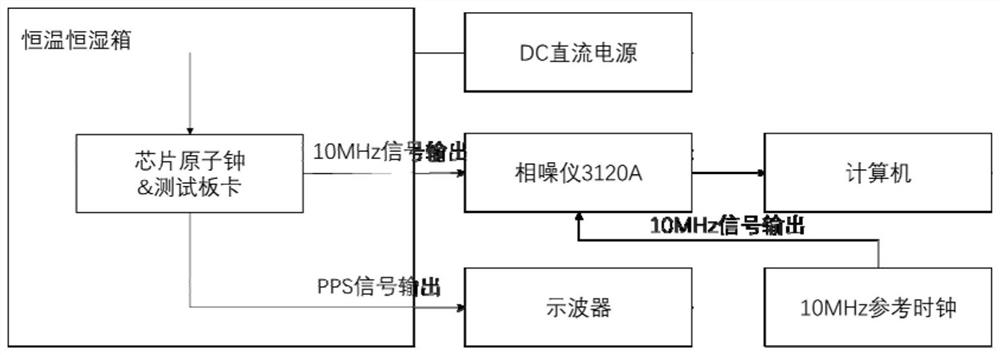

[0038] This embodiment discloses an accelerated aging reliability test device for a chip atomic clock. The device includes: a test board, a temperature and humidity box, a reference clock, an oscilloscope, a DC power supply, a phase noise tester, and a computer. The test board The card is placed in a temperature and humidity box, and a plurality of chip atomic clocks are installed on a test board card. The test board card is provided with a chip atomic clock socket 1, a voltage conversion module, a signal output module and a power interface 6. The DC power supply The power supply interface 6 supplies power to the test board, the voltage conversion module supplies power to the chip atomic clock, and the signal output module is connected to an oscilloscope, a phase noise tester and computer equipment to evaluate the time and frequency signal quality of the chip atomic clock.

[0039] The power interface 6 is connected to the DC power supply, and a plurality of chip atomic clocks ...

Embodiment 2

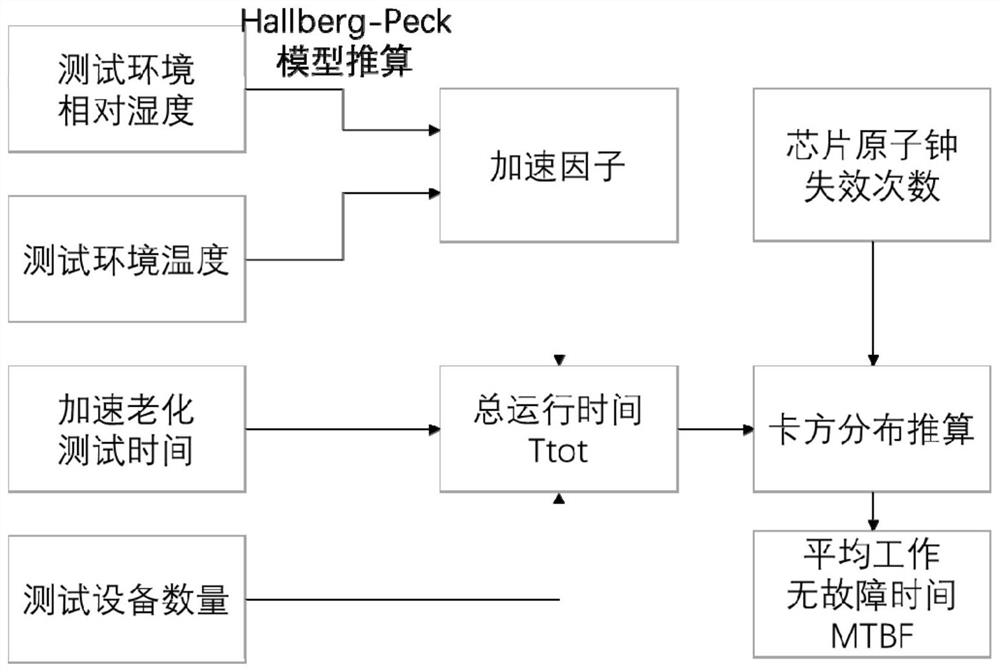

[0044] This embodiment discloses an accelerated aging reliability test method for a chip atomic clock, and the method is as follows:

[0045] Place a number of chip-level atomic clocks on the test board; place the board of the chip atomic clock in a temperature and humidity box, adjust the temperature inside the box to 40°C and 85% relative humidity, and connect the test board to the power supply outside the box and turn it on. Continue to work under the conditions, the oscilloscope tests the quality of the second pulse signal to detect the frequency of faults, the phase noise tester measures the measurement signal and sends it to the computer, calculates the acceleration factor through the acceleration model, and finally obtains the mean time between failures MTBF.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More