Method and system for measuring alignment error

An alignment error and measurement technology, applied in the field of alignment error measurement methods and systems, can solve problems such as affecting the performance of semiconductor devices and increasing alignment errors, so as to improve performance, reduce detection time, and improve process performance and productivity effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only a part of the embodiments of the present invention, but not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

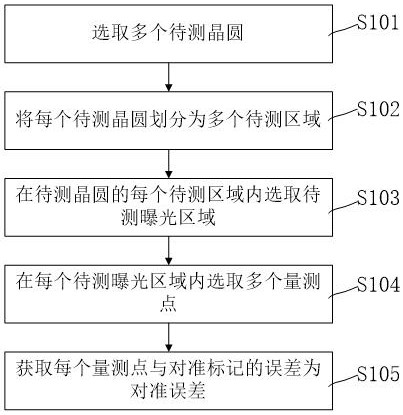

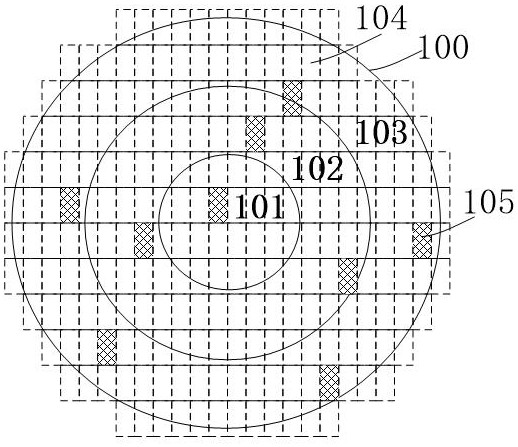

[0049] see figure 1 and image 3 As shown, in the field of semiconductor fabrication technology, a wafer is divided into a number of exposure areas 104, and the exposure area 104 is usually used as a basic unit in production. The exposure areas 104 are periodically repeated on the wafer, and each exposure area 104 includes one or more chips, and the chips are also periodically repeated on the wafer. And a dicing line is arranged bet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More