Aging screening device for anti-fuse FPGA (Field Programmable Gate Array) device

A screening device and anti-fuse technology, applied in the direction of measuring devices, instruments, electronic circuit testing, etc., can solve the problem of not providing the description and implementation method of the aging screening device.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

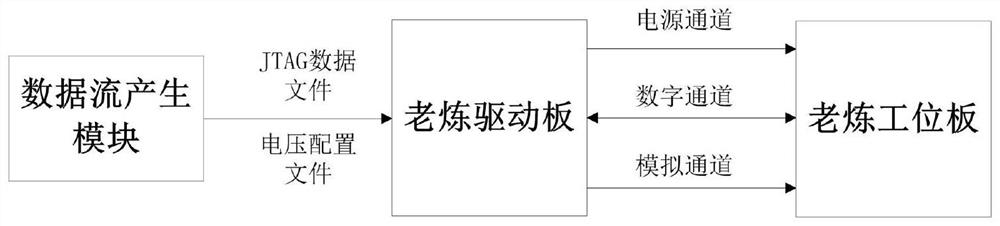

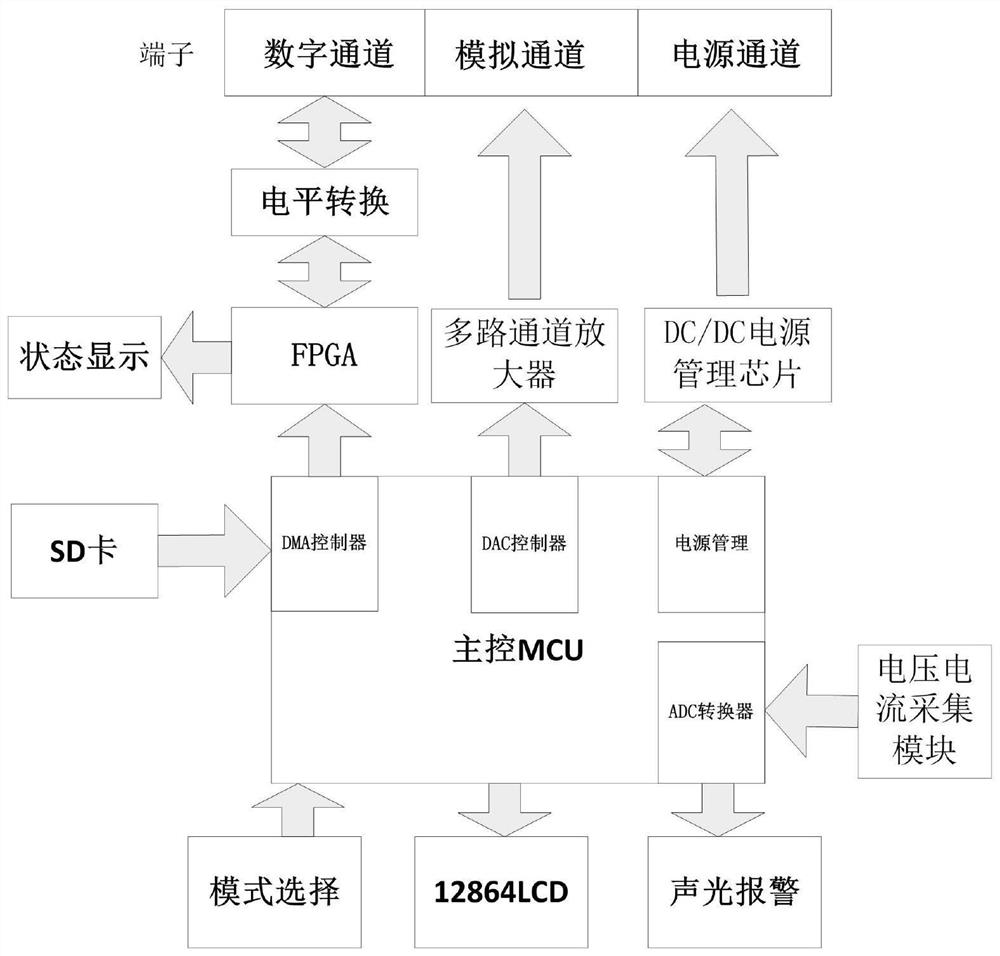

[0018] like figure 1 and figure 2 As shown, this embodiment provides a burn-in screening device for an anti-fuse type FPGA device, which includes a data stream generation module, a burn-in station board and a burn-in driver board. Its block diagram is as follows: figure 1 shown. The boards are connected to each other through two 2.54mm pitch gold finger connection terminals. The terminal can be customized and installed on the high-temperature aging box of the specified type, so as to form a standard interface inside and outside the box, and realize the reliable connection between the station board and the drive board under high temperature. The connection terminal defines the bit numbers of the power channel, digital channel and analog channel, and the aging driver board and the aging station board can be independently designed according to this definition. Each component of the aging screening device will be described separately below.

[0019] The data flow generation m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More