Flow control mechanism-oriented deadlock-free extensible interconnection bare core architecture

A deadlock-free, bare-core technology, applied in transmission systems, electrical components, etc., can solve the problems of Moore's Law failure, cost and high development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

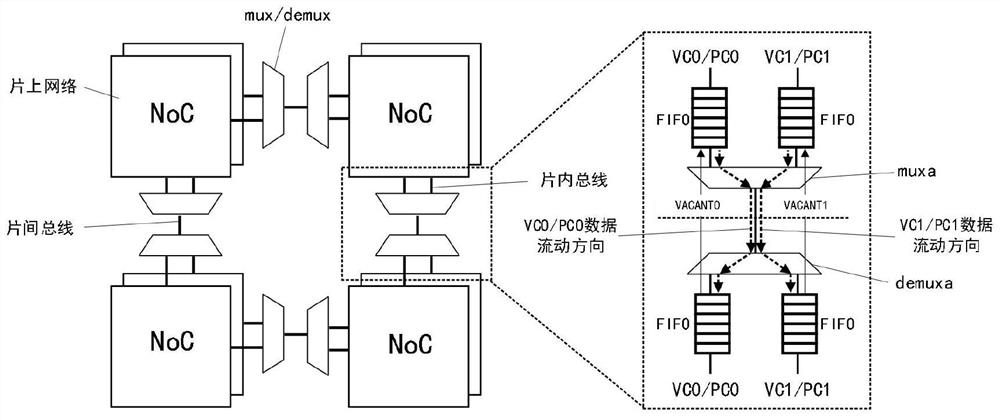

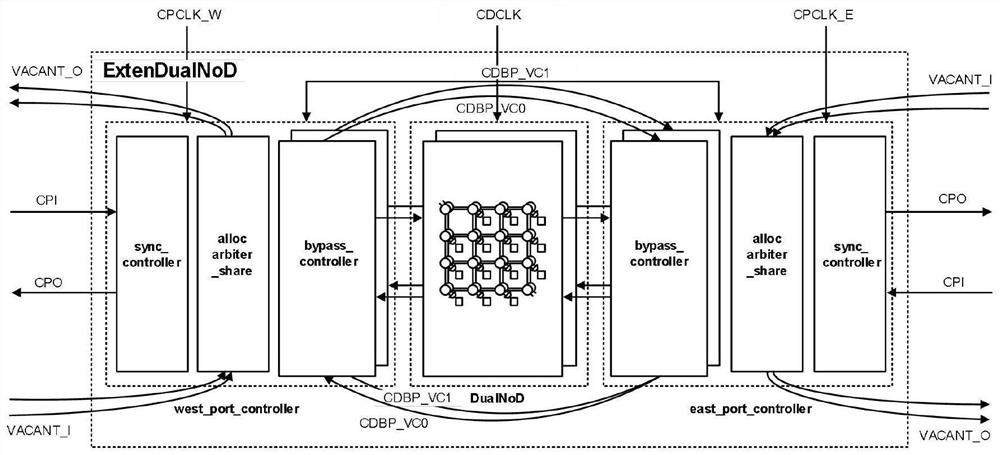

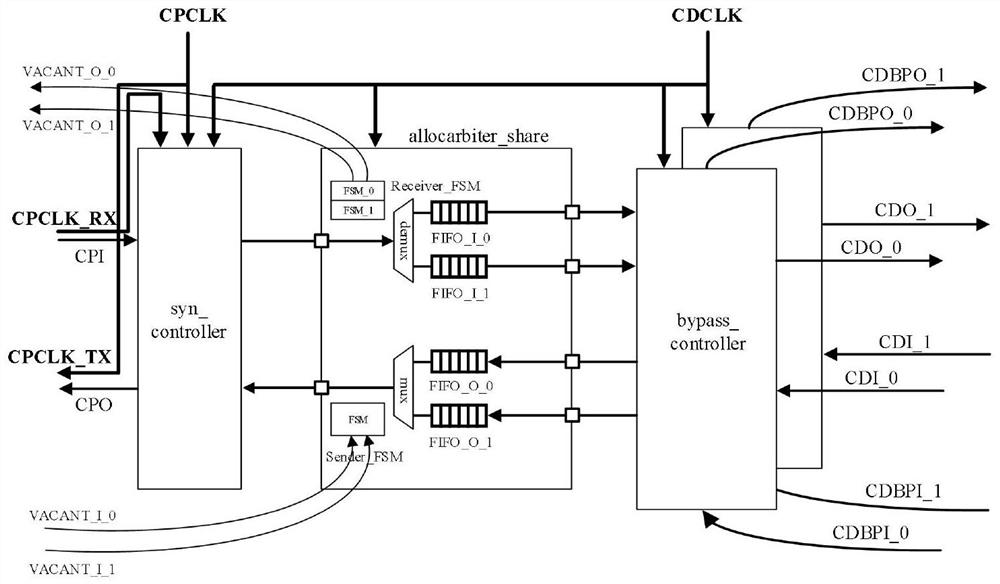

[0016] The present invention is oriented to the inter-chip ring network topology, that is, the on-chip inter-chip integrated network is generally connected to each other into a ring by a plurality of on-chip networks. Inside each bare chip, a dual virtual channel (Virtual Channel, VC) or Dual physical channel (Physical Channel, PC) on-chip network to achieve no deadlock on-chip. Data transmission between multiple die relies on the inter-chip ring bus. When data is transmitted from one die to an adjacent die, it first passes through a dual multiplexing unit (mux) in the current die. The function is to arbitrate the data in two virtual or physical channels (hereinafter referred to as channels) to an inter-chip physical link, and then the data is transmitted to the adjacent die through the inter-chip physical link, and then passes through the inter-chip physical link. The distribution unit (demux) is fed into a certain channel. The physical link between adjacent die is bidirecti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More