Wave field reconstruction method three-dimensional pre-stack reverse time migration method based on FPGA multi-board card architecture

A pre-stack reverse time offset, multi-board technology, applied in the computer field, can solve the problems of increased data transmission on computing resource consumption, large amount of 3D-RTM computing data, and high computing power requirements, so as to avoid transmission problems and reduce The consumption of computing resources and the effect of improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

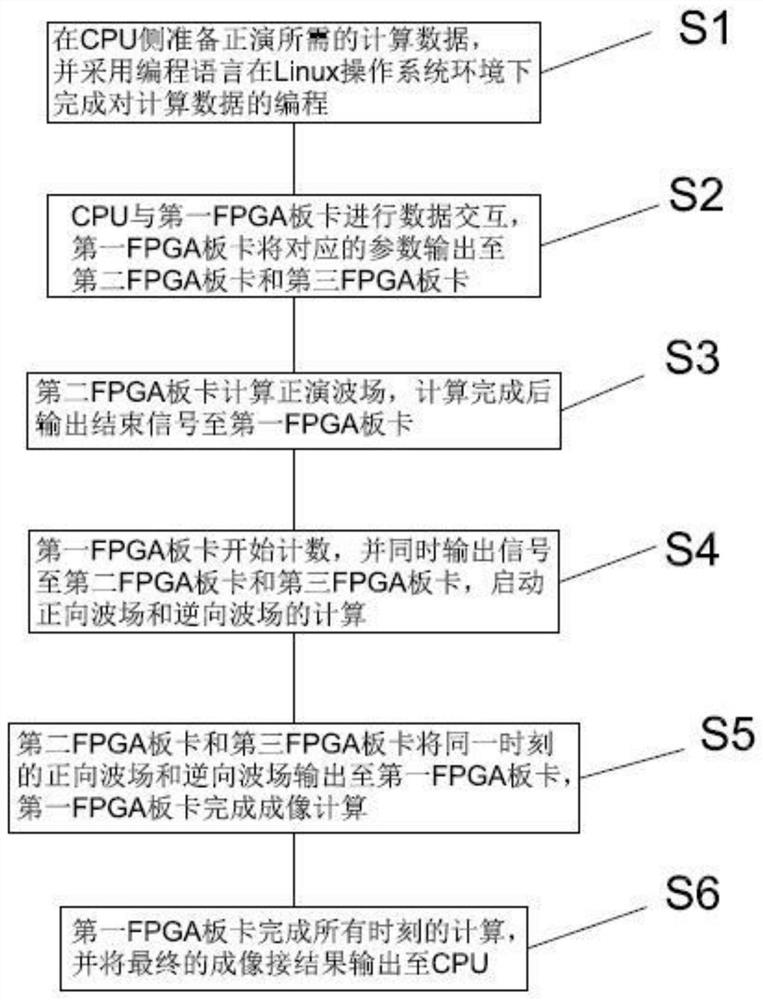

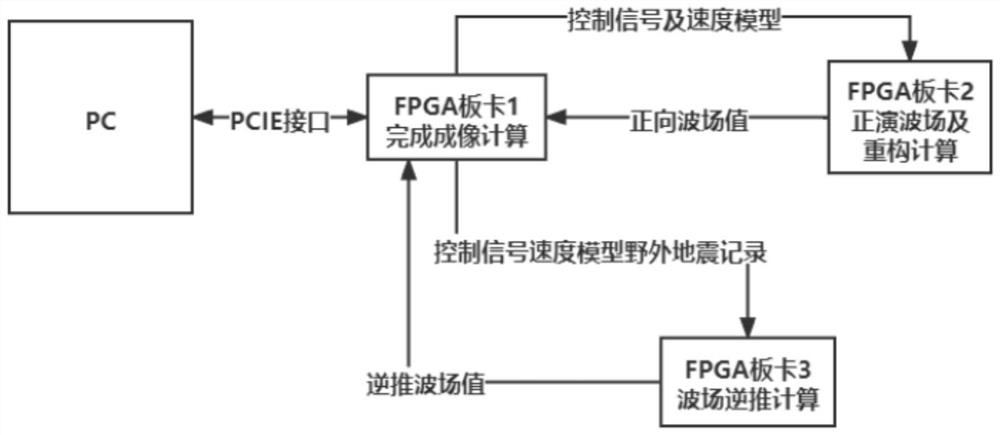

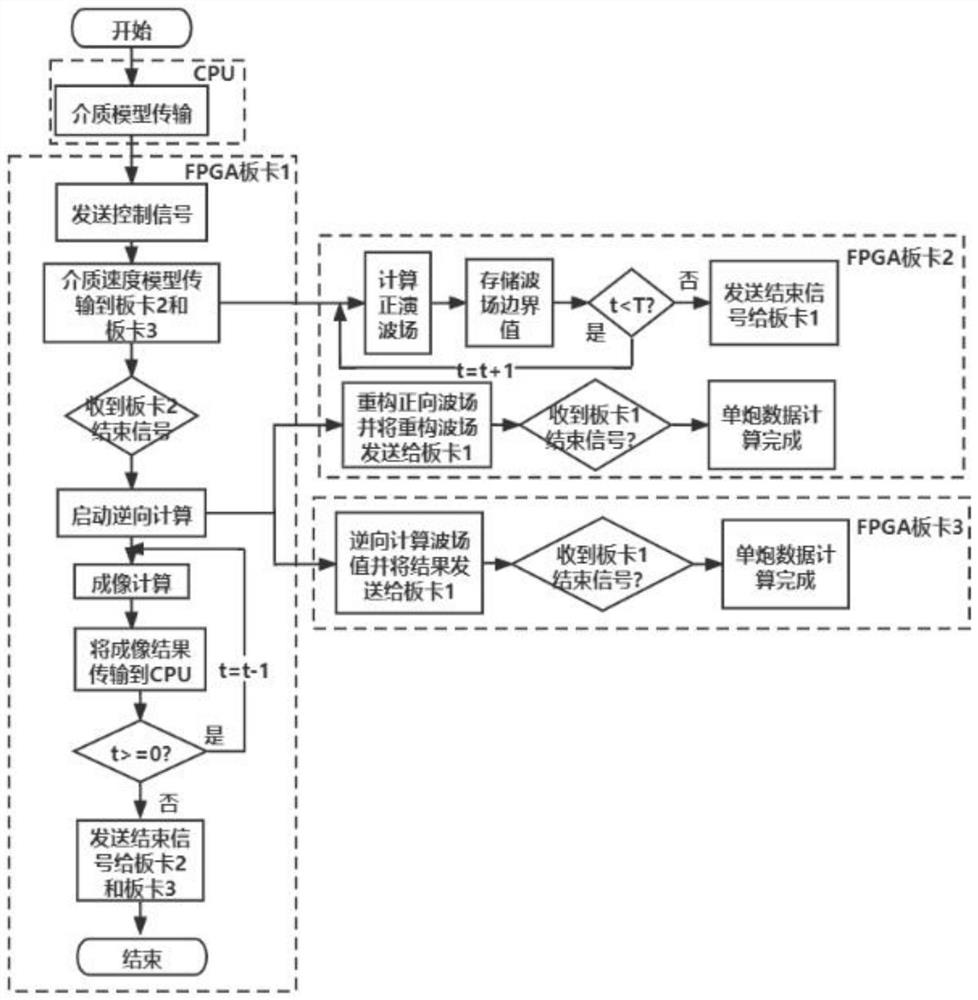

[0030] The technical solutions of the present invention will be clearly and completely described below with reference to the accompanying drawings. Obviously, the described embodiments are a part of the embodiments of the present invention, but not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

[0031] In the description of the present invention, it should be noted that when the terms "center", "upper", "lower", "left", "right", "vertical", "horizontal", "inner", "outer" appear. ”, etc., the indicated orientation or positional relationship is based on the orientation or positional relationship shown in the accompanying drawings, only for the convenience of describing the present invention and simplifying the description, rather than indicating or implying that the indicated device or element m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More