Memristor-based summator, driving method and electronic equipment

A driving method and memristor technology, applied in the field of electronics, can solve the problems of small delay, complex structure, difficult integration, etc., and achieve the effect of eliminating alignment work, reducing computing delay, and being easy to integrate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

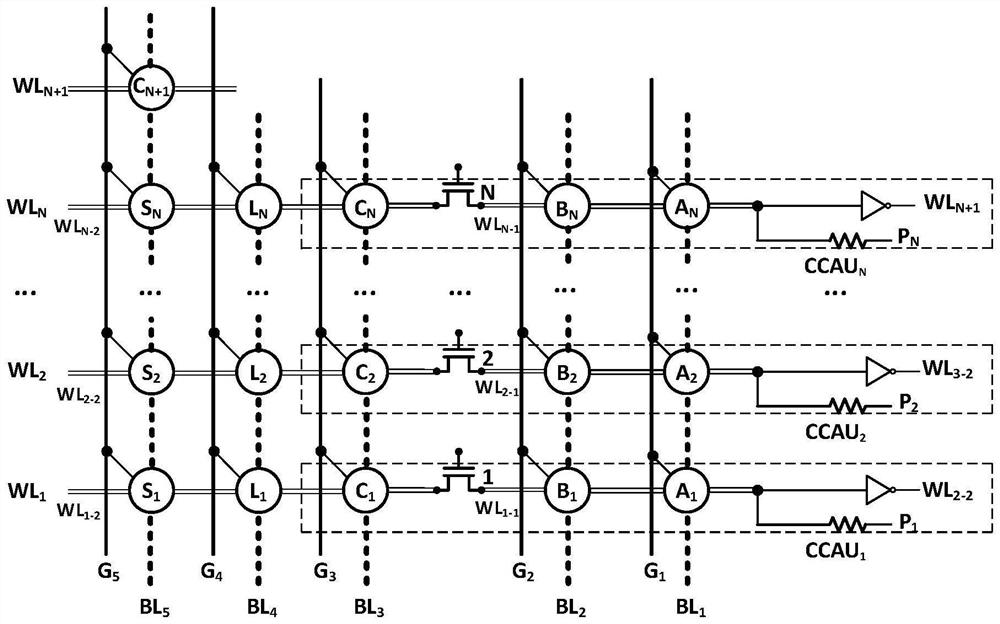

[0040] refer to figure 1 , figure 1This embodiment is a schematic structural diagram of a memristor-based adder. like figure 1 As shown, the memristor-based adder includes:

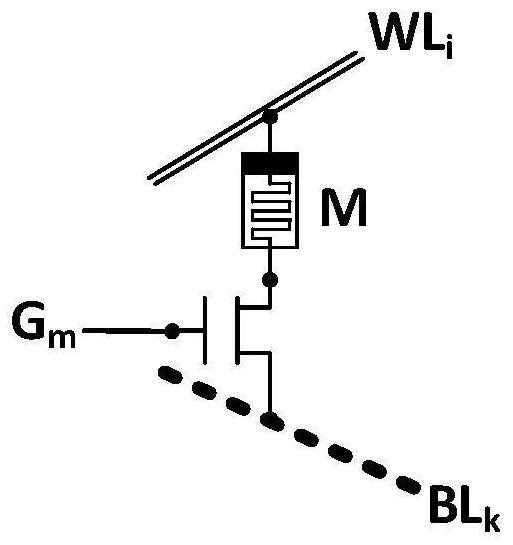

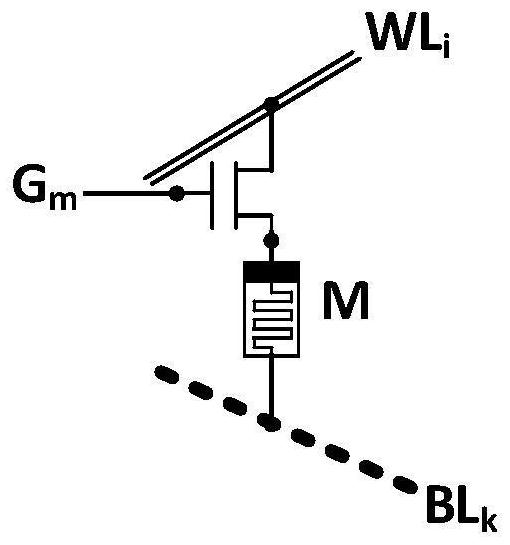

[0041] 1T1R array, N peripheral circuits, the 1T1R array includes a first 1T1R sub-array, a second 1T1R sub-array, a third 1T1R sub-array, a fourth 1T1R sub-array, and a fifth 1T1R sub-array arranged in sequence, the first 1T1R sub-array The 1T1R sub-array, the second 1T1R sub-array, the third 1T1R sub-array, and the fourth 1T1R sub-array respectively include N 1T1R units, and the fifth 1T1R sub-array includes N+1 1T1R units. The 1T1R unit includes a memristor and a MOS transistor, and the bottom electrode of the memristor is connected to the source or drain of the MOS transistor;

[0042] The drain or source of the MOS transistor in each 1T1R unit of each 1T1R sub-array is connected to the word line of the corresponding column, and the gate of the MOS transistor in each 1T1R unit of each 1T1R sub-arr...

Embodiment 2

[0096] refer to Figure 9 , Figure 9 This embodiment provides a driving method for an adder, which can be used to drive the memristor-based adder described in Embodiment 1 above. The following describes the steps of the driving method for the adder. To elaborate:

[0097] Step S901, according to the logic value of the memristor in the i-th 1T1R unit of the first 1T1R sub-array, the logic value of the memristor in the i-th 1T1R unit of the second 1T1R sub-array, and the logic value of the third 1T1R sub-array The logic value of the memristor in the i-th 1T1R cell, determines the logic value of the memristor in the i+1-th 1T1R cell of the third 1T1R subarray, 1≤i≤N-1, and according to the first 1T1R The logic value of the memristor in the Nth 1T1R cell of the subarray, the logic value of the memristor in the Nth 1T1R cell of the second 1T1R subarray, and the logic value of the memristor in the Nth 1T1R cell of the third 1T1R subarray The logic value of the memristor determin...

Embodiment 3

[0149] This embodiment provides an electronic device, which stores a computer program, and when the computer program runs on a processor, executes the method for driving an adder provided in Embodiment 2 above.

[0150] The electronic device provided in this embodiment can implement the steps of executing the method for driving the adder provided in Embodiment 2, which is not repeated here to avoid repetition.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com