Networking layout method and device, equipment and storage medium

A layout method and networking technology, applied in computer-aided design, instrumentation, computing, etc., can solve problems such as increased signal transmission delay, low communication efficiency, and increased device loss, so as to save the number of uses, compact and centralized layout, and speed up The effect of the verification process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

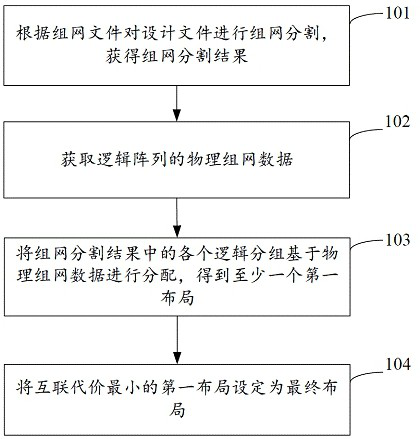

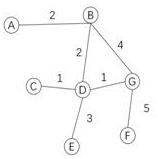

[0022] The embodiments of the present application will be described in detail below with reference to the accompanying drawings.

[0023] The embodiments of the present application are described below through specific specific examples, and those skilled in the art can easily understand other advantages and effects of the present application from the contents disclosed in this specification. Obviously, the described embodiments are only a part of the embodiments of the present application, but not all of the embodiments. The present application can also be implemented or applied through other different specific embodiments, and various details in this specification can also be modified or changed based on different viewpoints and applications without departing from the spirit of the present application. It should be noted that the following embodiments and features in the embodiments may be combined with each other under the condition of no conflict. Based on the embodiments ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More