Nonvolatile semiconductor memory

A memory, read-only memory technology, applied in the field of stretch, non-volatile memory, which can solve the problems of high current and increased complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

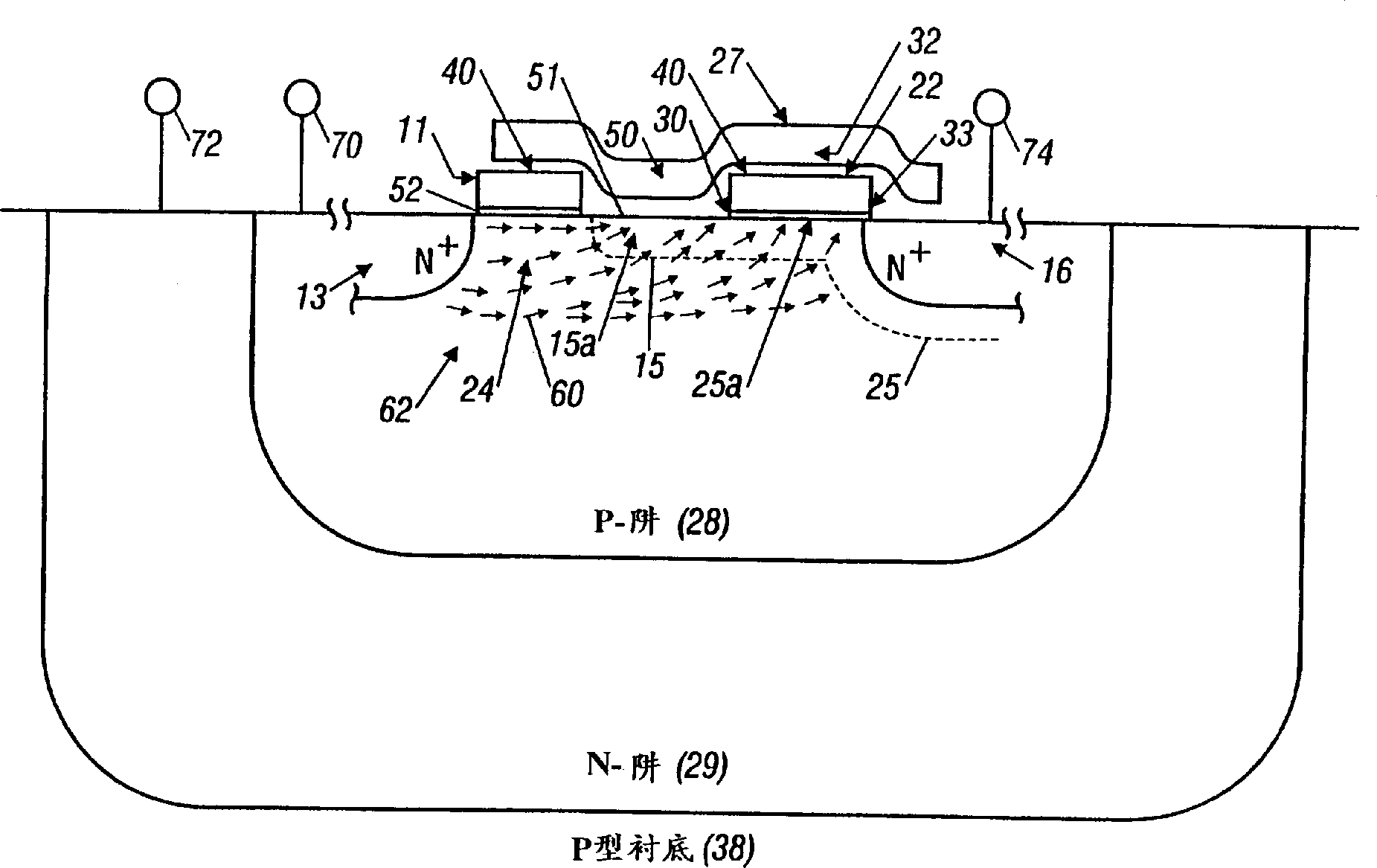

[0019] Description of preferred embodiments

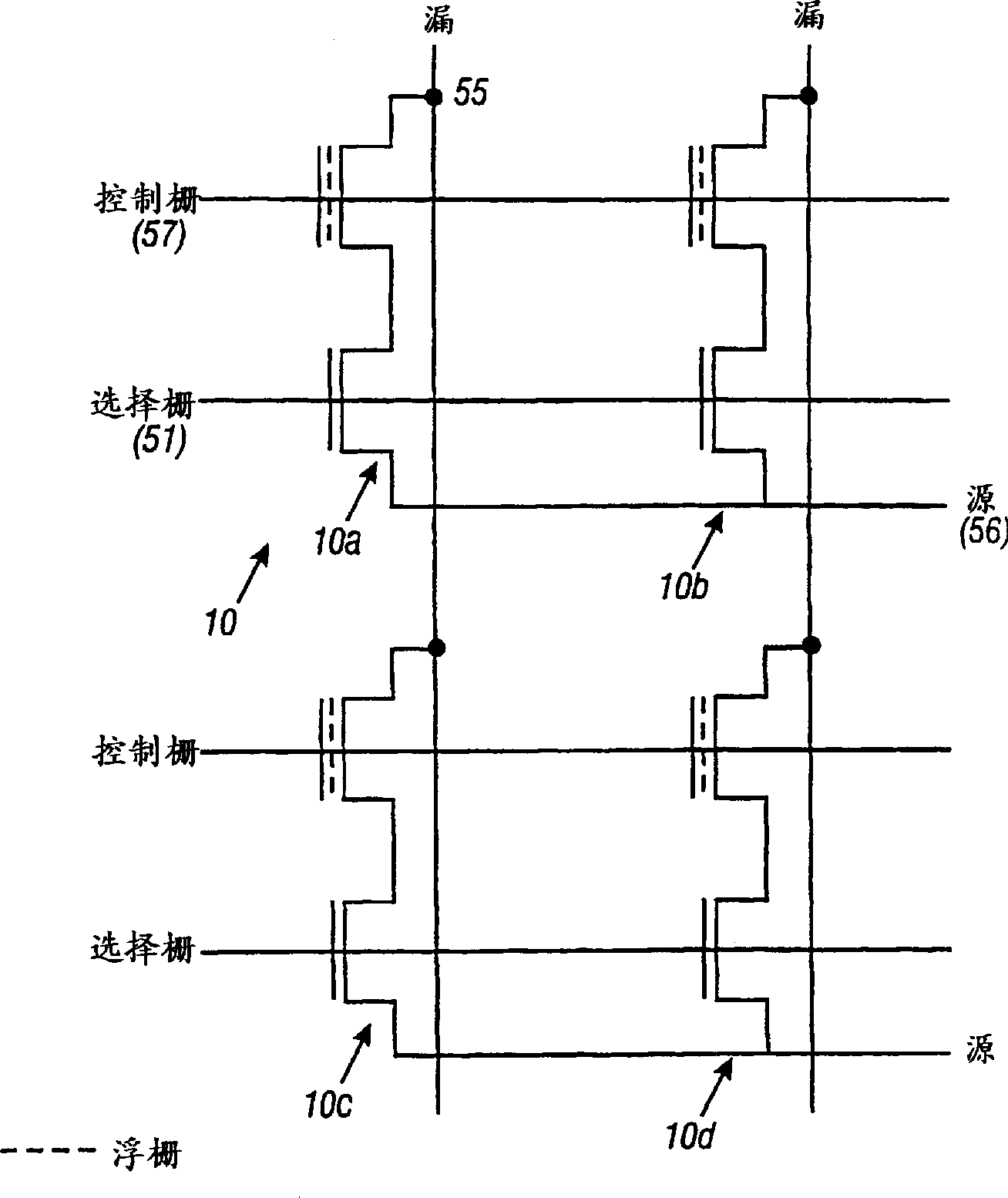

[0020] Referring to the accompanying drawings, wherein the same reference signs are used for like parts in each figure, figure 1 The illustrated memory cell 10 includes a read transistor 12 and a select transistor 14 . This structure is advantageously implemented on a semiconductor layer on which the electrically isolated floating gate 22 is arranged.

[0021] Source 13 of select transistor 14 is controlled by source node 56 for each cell 10a-10d. The gate of select transistor 11 is controlled by node 51 . The control gate 27 of the read transistor 12 is controlled by a control node 57 . Drain 16 of read transistor 12 is connected to drain node 55 .

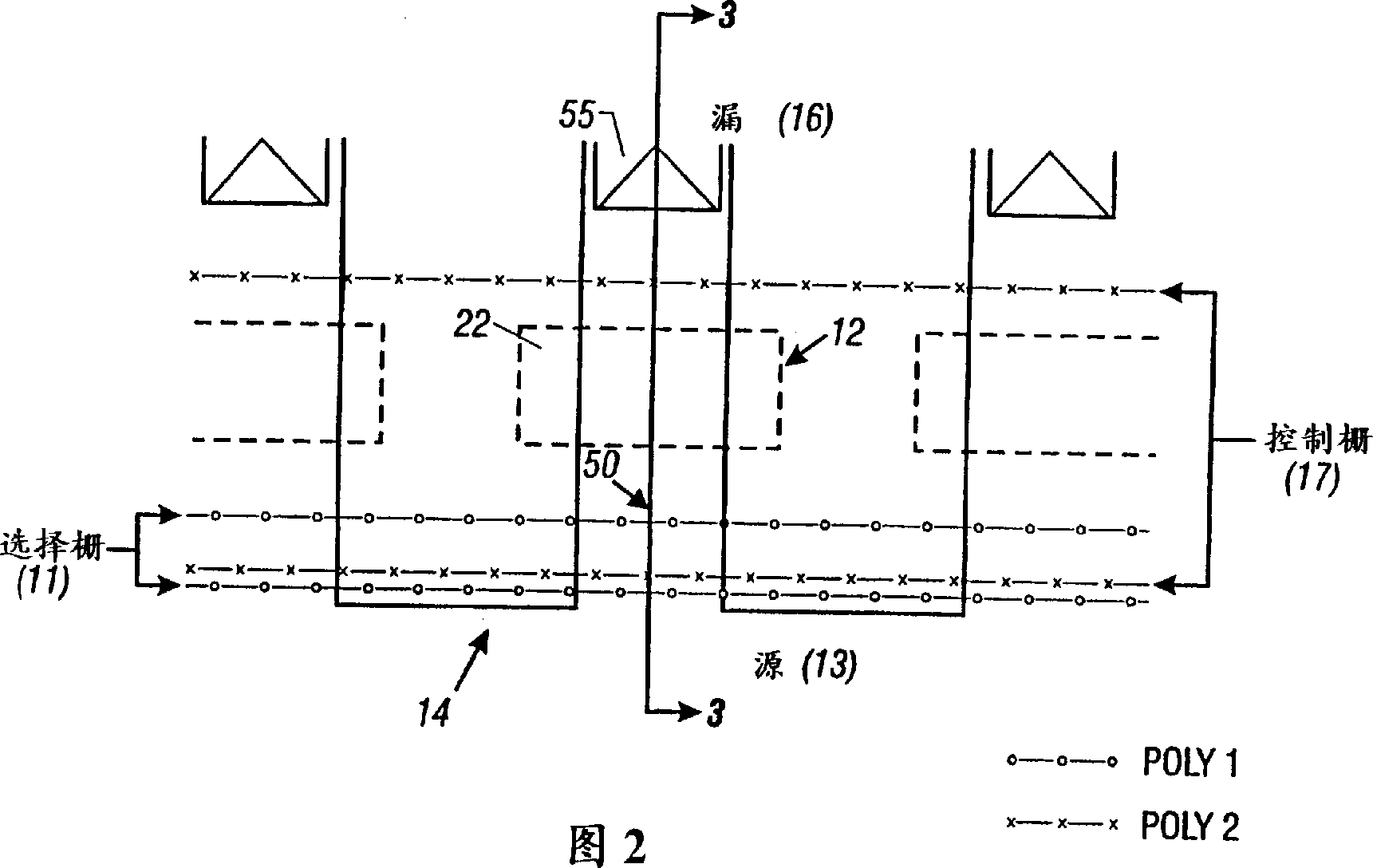

[0022] One implementation of the cell 10 layout shown in FIG. 2 includes a control gate 17 . The control gate 17 extends across an active region 18 adjacent to the drain 16 of the read transistor 12 and the source 13 of the select transistor 14 . The select gate 11 extends paral...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com