High-current triggered electrostatic discharge protector

A technology of electrostatic discharge protection and electrostatic discharge, which is applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of crashing and burning semiconductor chips, and achieve the effect of small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

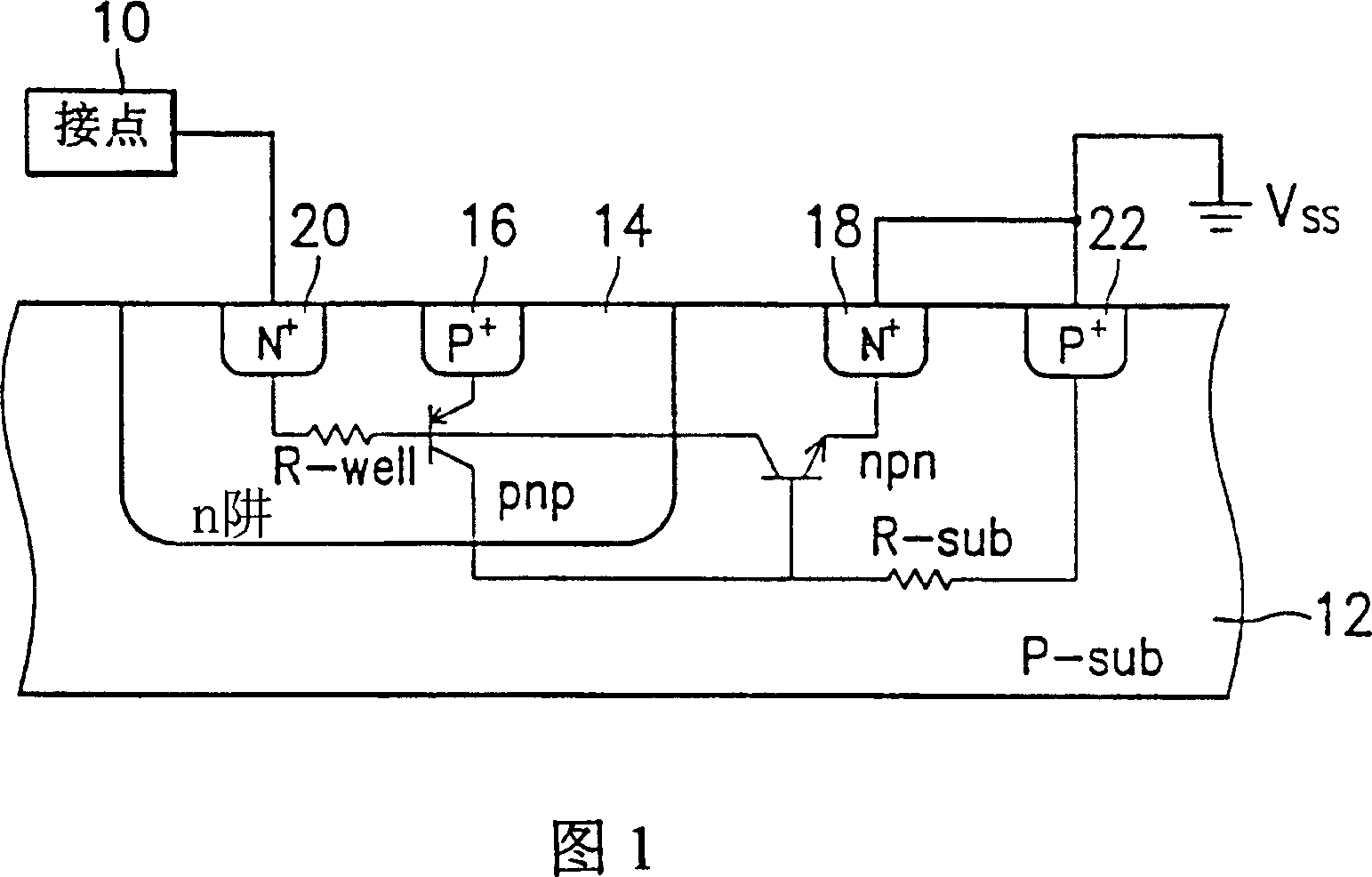

[0038]Please refer to FIG. 1 . FIG. 1 is a schematic cross-sectional view of a first embodiment of the ESD protection circuit of the present invention. The present invention provides an ESD protection circuit for releasing the ESD current on the contact 10 to a reference potential, such as VSS in FIG. 1 . The ESD protection circuit includes a substrate 12 of a first conductivity type, a well region 14 of a second conductivity type, a first doped region 16 of a first conductivity type, a second doped region 18 of a second conductivity type, and a A third doped region 20 of the second conductivity type and a fourth doped region 22 of the first conductivity type. For the convenience of explanation, the first conductivity type is p-type, and the second conductivity type is n-type. The substrate 12 is electrically coupled to the reference potential VSS through the fourth doped region 22 . That is, the fourth doped region 22 is disposed on the surface of the substrate 12 as an ohm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More