Method for plating via hole with copper

A technology of via holes and copper plating, which is applied in circuits, printed circuits, printed circuits, etc., can solve the problem that the via holes cannot meet the thermal shock test.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

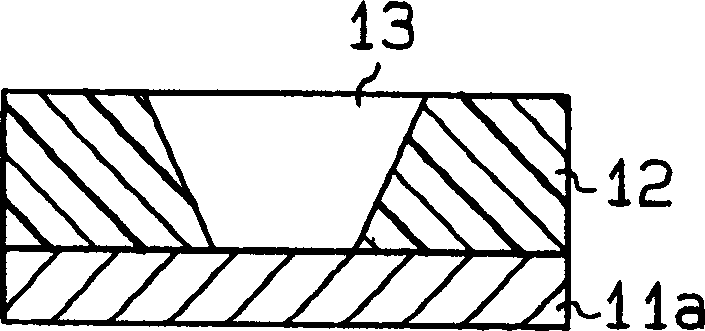

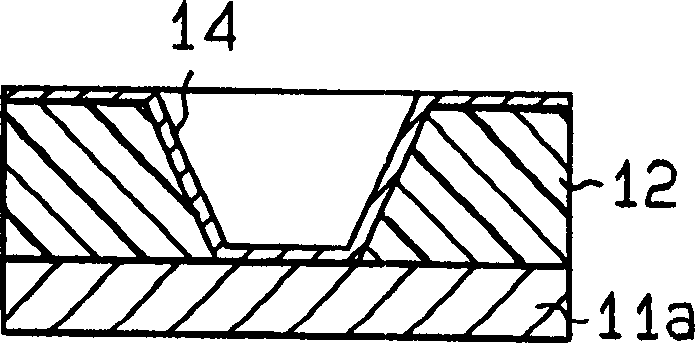

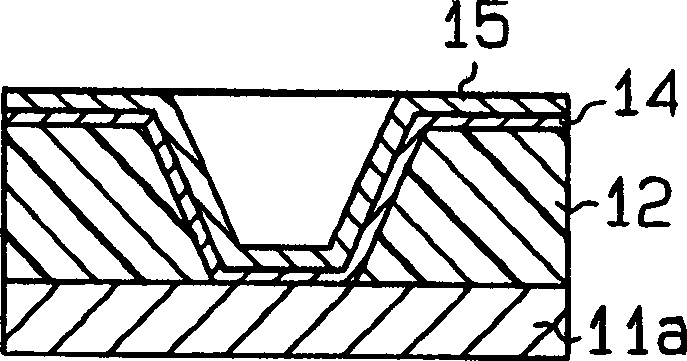

[0020] An embodiment of the method of forming a via hole of the present invention will be described below with reference to FIGS. 1(a) to 3(b). In this embodiment, the diameter of the formed via hole is 40 μm.

[0021] In order to form a conductive layer that fills the plated via hole to form an electrical connection on the upper and lower sides of the multilayer substrate, an insulating layer 12 is first formed on the bottom conductive layer 11a, and then, a via hole 13 is formed by laser radiation, As shown in Figure 1(a). Then carry out the degreasing method. A catalyst coating step and an electroless copper plating step are then performed on the inner wall of the via hole 13 and the upper layer forming the conductive layer 11b to form a thin electroless copper plating layer 14, as shown in FIG. 1(b).

[0022] An electrolytic copper plating step is then performed. The electrolytic copper plati...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More