Digital PLL regulating crystal oscillator frequency and its regulation method

A technology of crystal oscillator and digital phase-locked loop, applied in the direction of digital transmission system, automatic control of power, communication between multiple stations, etc., can solve the problem of network environment that cannot adapt to timing quality, clock tolerance and smooth large jitter/ Problems such as limited drifting ability, to achieve the effect of improving online survivability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

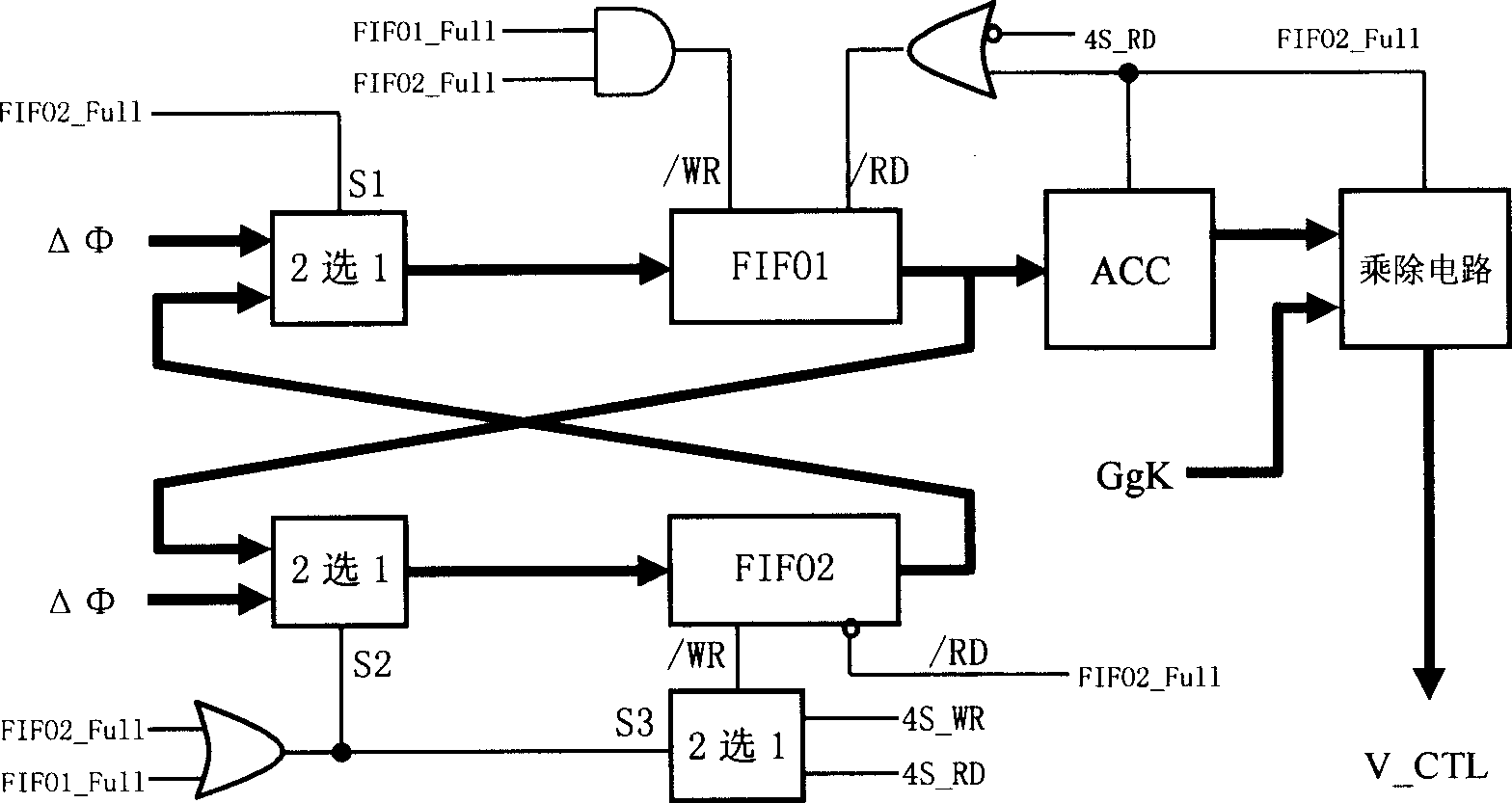

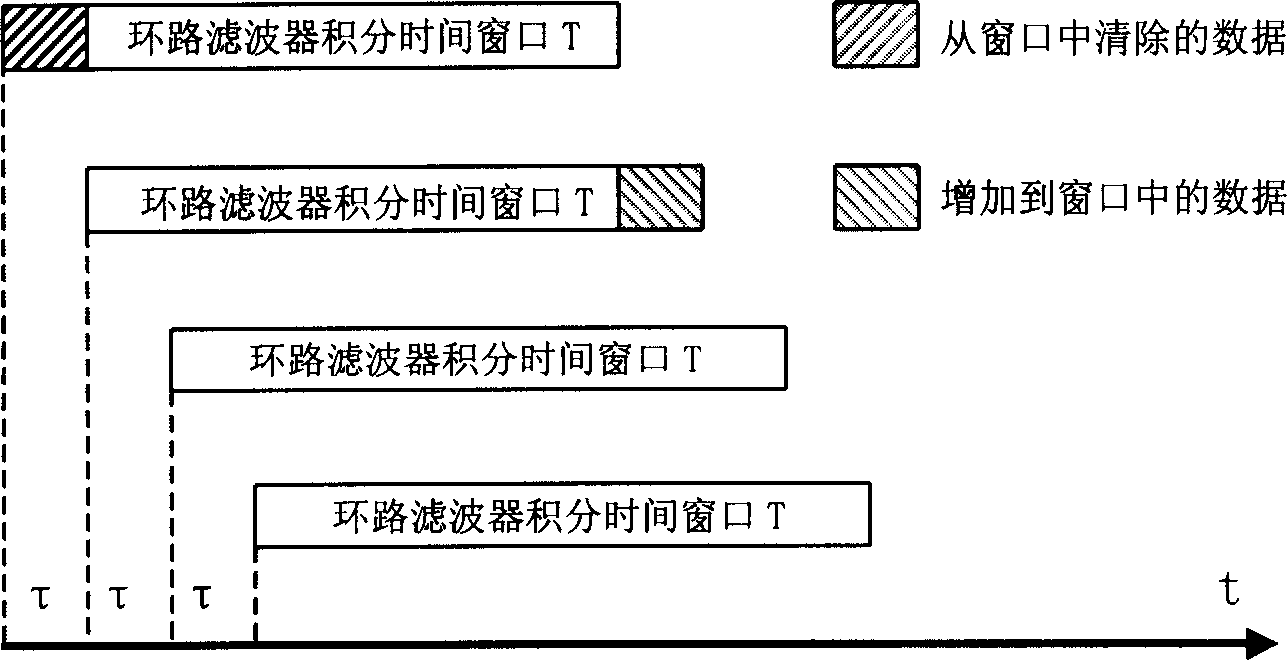

[0017] The basic idea of the sliding window DPLL design of the present invention is that the large integration time window slides forward with a smaller step value, that is, only a small part of data is refreshed in the integration time interval, and this part of data is together with most of the unrefreshed data. Sum and average. The hardware implementation method and the software implementation method are the sliding window DPLL hardware implementation circuit and software algorithm flow. The connection relationship and signal flow of each functional block of the sliding window DPLL.

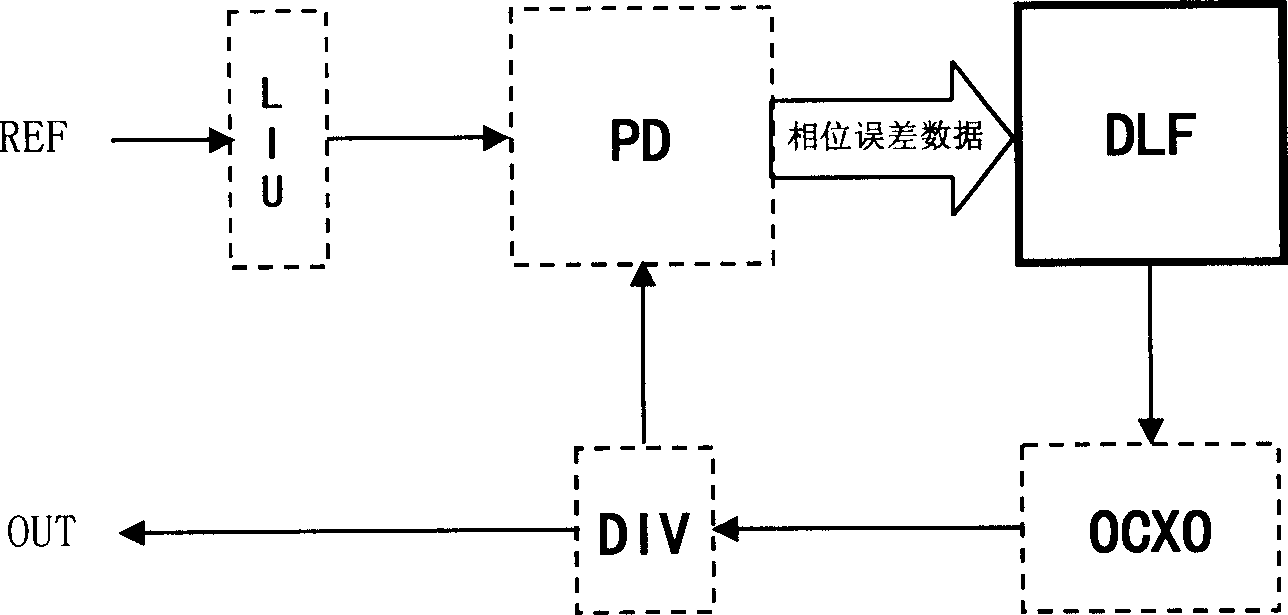

[0018] figure 1 A sliding window digital phase-locked loop for use in a telecommunication network of the present invention is shown, which includes a LIU line interface unit, a PD phase detector, a DIV frequency divider, a DLF digital loop filter, and an ove...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com