Single-output feedback-free sequential test response compression circuit

A circuit and compressor technology, which is applied in the field of single-output non-feedback timing test response compression circuit, which can solve the problems of long test time, low compression rate, and inability to guarantee

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

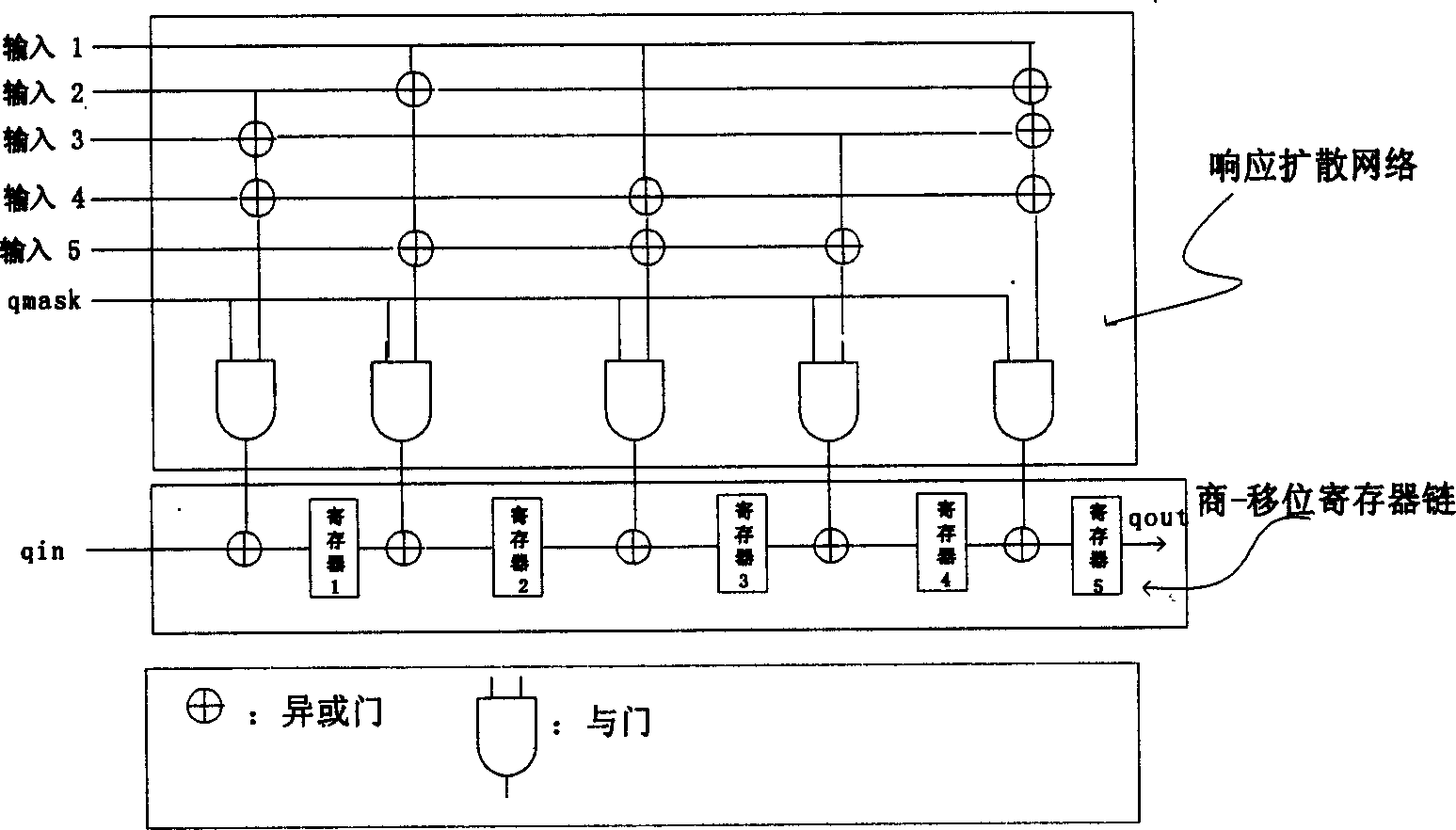

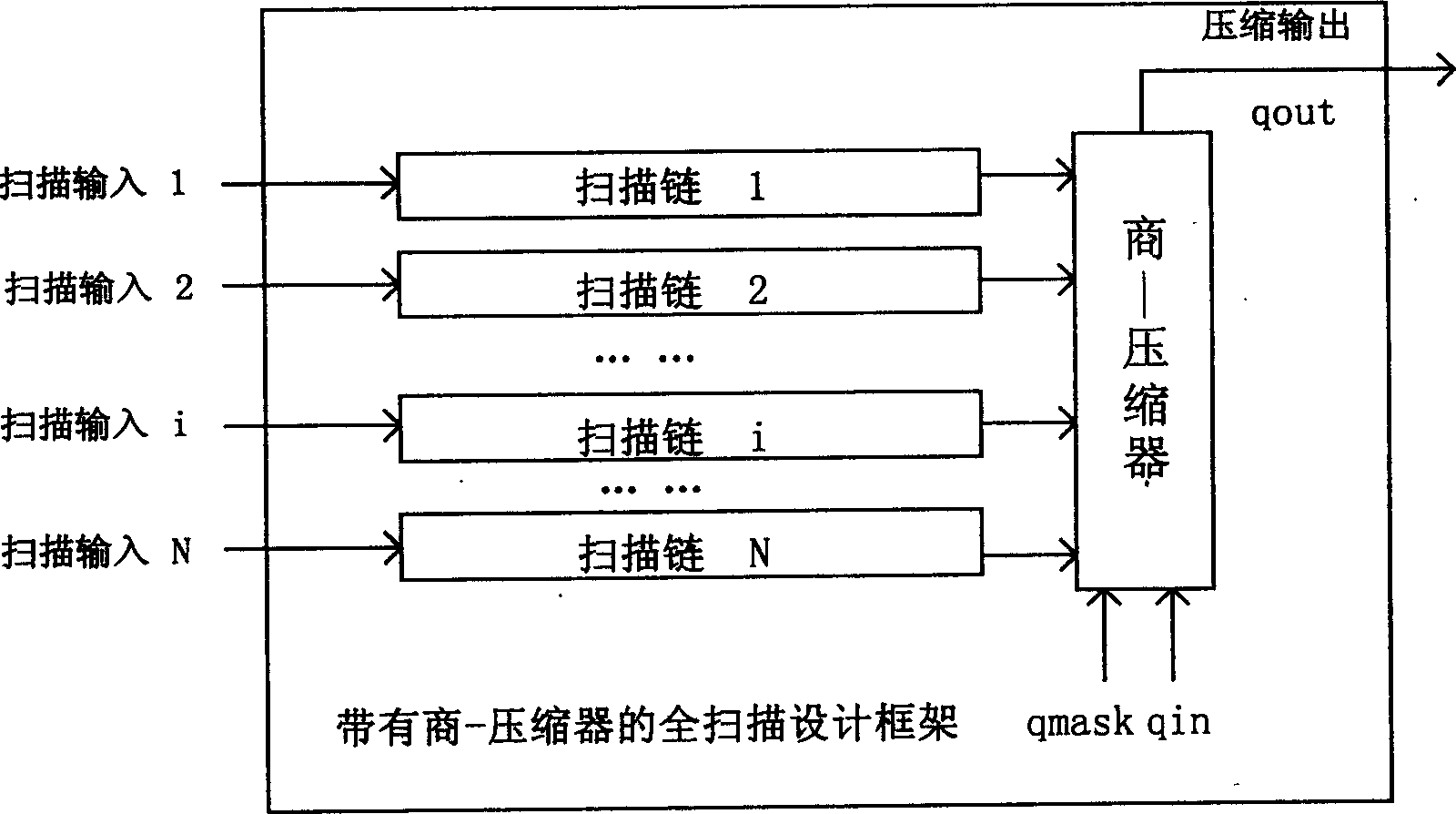

[0051] The invention is applied to compress the test response. Figure 2 depicts the full scan design framework with quotient-compressor. It can be seen from the figure that the response compressor is designed on the output of the scan chain. Compress the output of multiple scan chains into one output, and output to the test equipment through a scan output pin for comparison. Therefore, from the perspective of the entire design process, the design of the response compressor and the design of the scan chain are basically independent of each other. Therefore, there is no need to modify the design flow of the original chip in response to the insertion of the compressor, nor does it need to modify the testability design flow of the original chip.

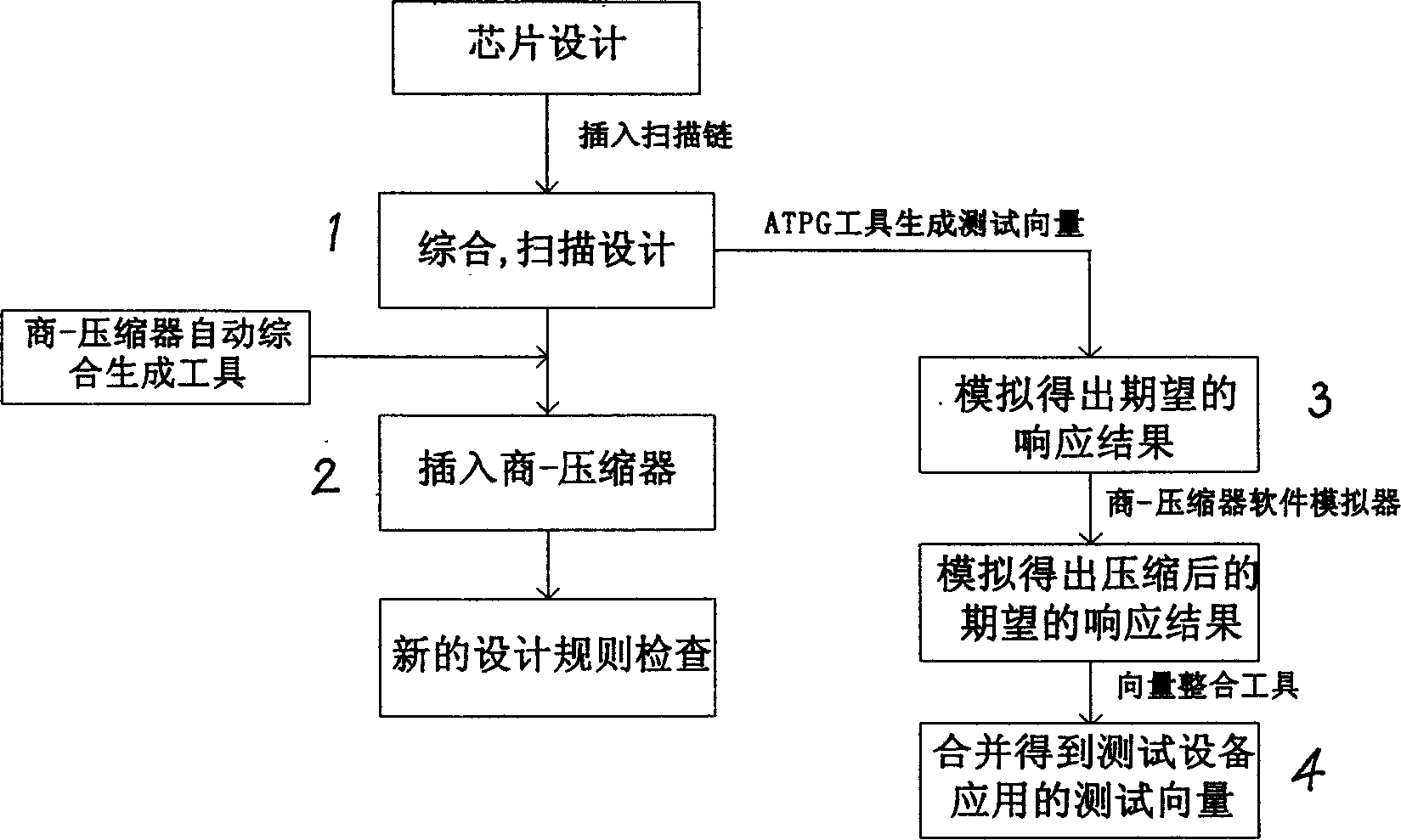

[0052] Figure 3 lists the applicator-compressor design flow for testability. It can be seen that the testability design process for an applier-compressor can be divided into the following steps:

[0053] 1) Comprehensive, scan chain design. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More