Packaging baseplate having electrostatic discharge protection

A technology for electrostatic discharge protection and packaging substrates, applied in circuits, electrical components, electrical solid devices, etc., can solve problems such as failure of packaging products, chip damage, and static electricity generation, so as to improve the good rate and protect from electrostatic charge damage. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

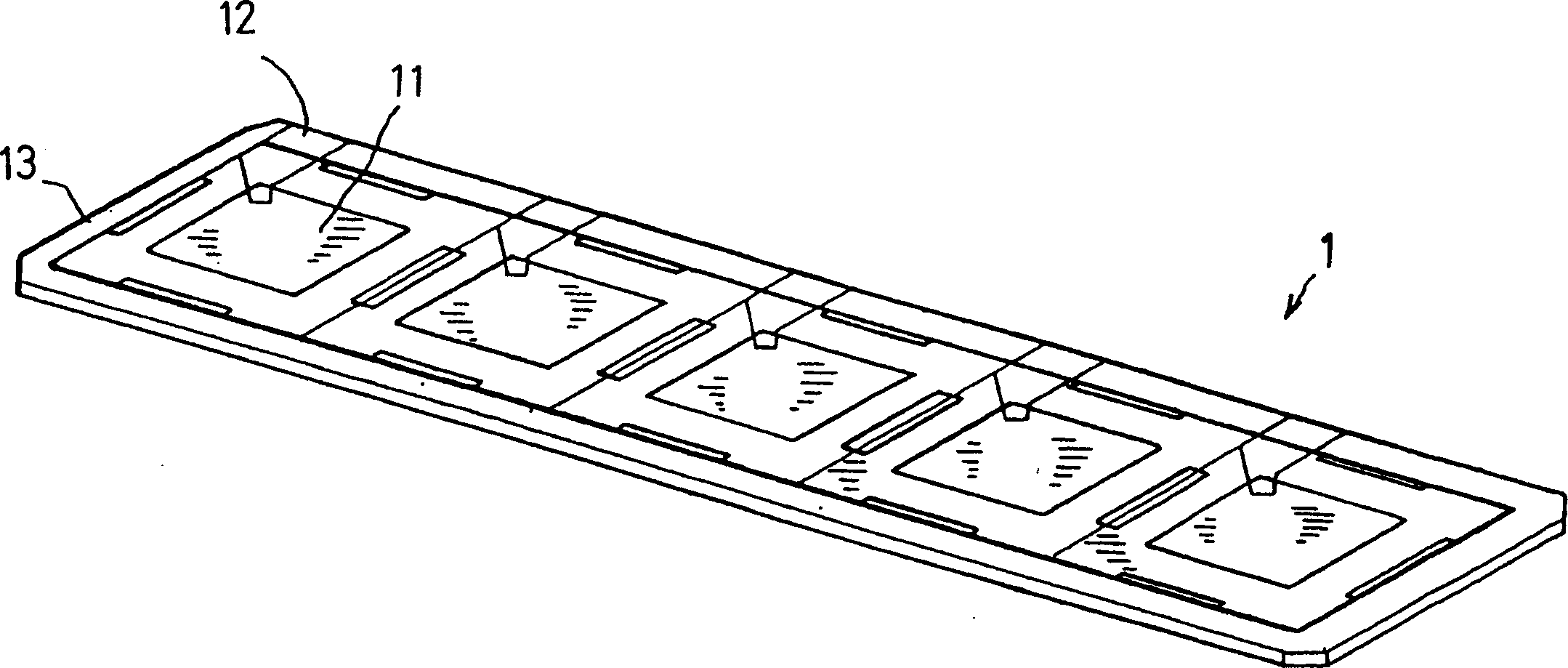

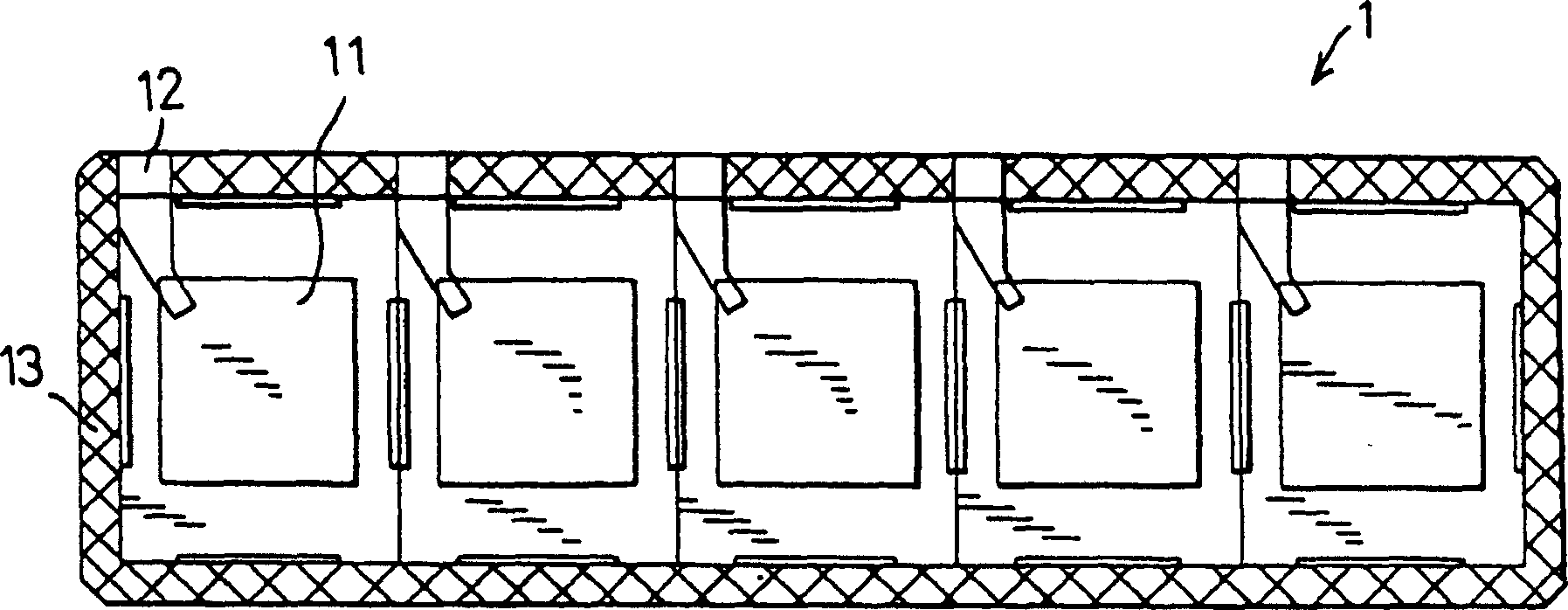

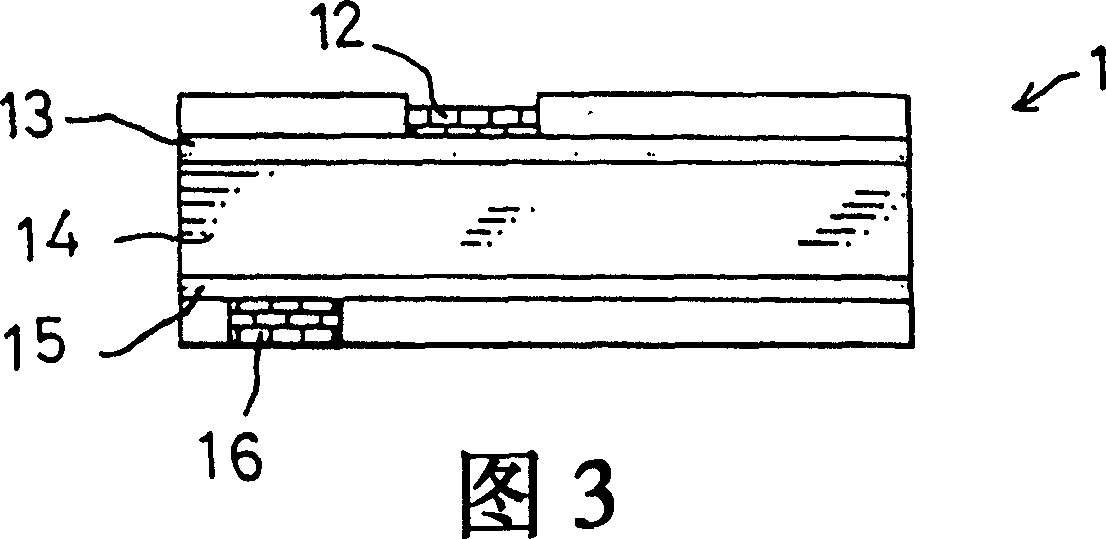

[0029] refer to figure 1 , figure 2 And Fig. 3, the packaging substrate 1 with electrostatic discharge protection of the first embodiment of the present invention comprises: five chip holders 11, five injection molding ports 12, a first copper mesh layer 13, a dielectric layer 14, a second Copper mesh layer 15 and a metal pad 16 . The chip holder 11 is used to carry the chip to be packaged. Each injection molding port 12 is connected to each die holder 11 by the edge of the packaging substrate 1 , and is used for guiding the encapsulant to inject into each die holder 11 . The injection molding ports 12 are disposed on the top surface of the packaging substrate 1 . The metal pad 16 is disposed on the bottom surface of the packaging substrate 1 .

[0030] The first copper mesh layer 13 is disposed on the periphery of the packaging substrate 1 , and the first copper mesh layer 13 is electrically connected to each injection molding port 12 at the periphery of the packaging su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More