'Fule nouhan' bi-directional write/erase flash memory in low voltage

A low-voltage, memory technology, applied in the field of low-voltage bidirectional Fowler Nohan write/erase flash memory, which can solve the problems of large chip area and high production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

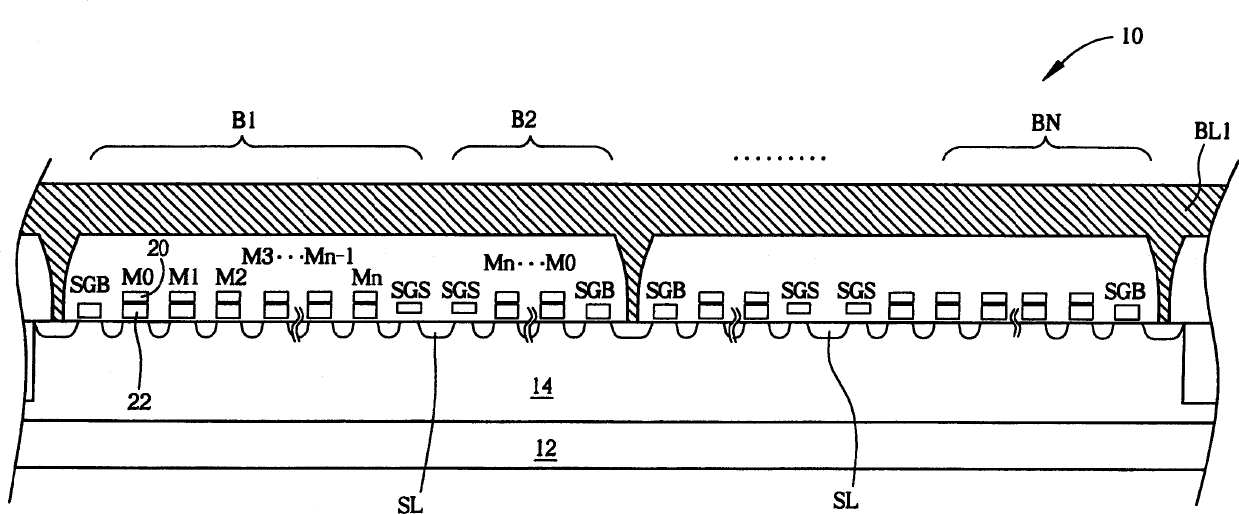

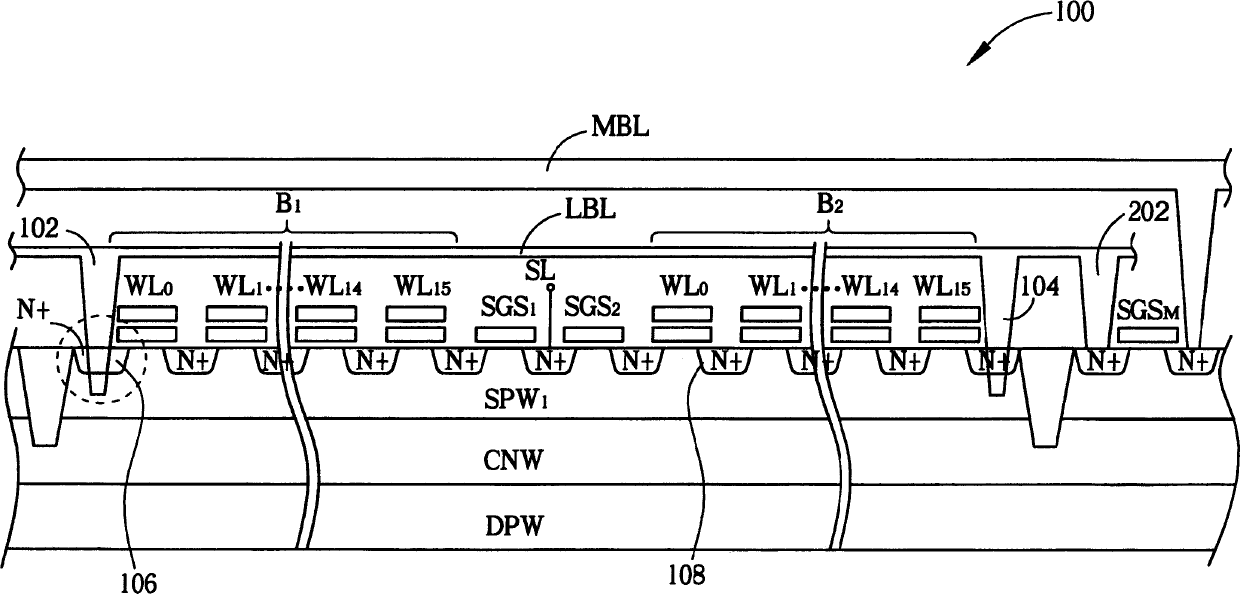

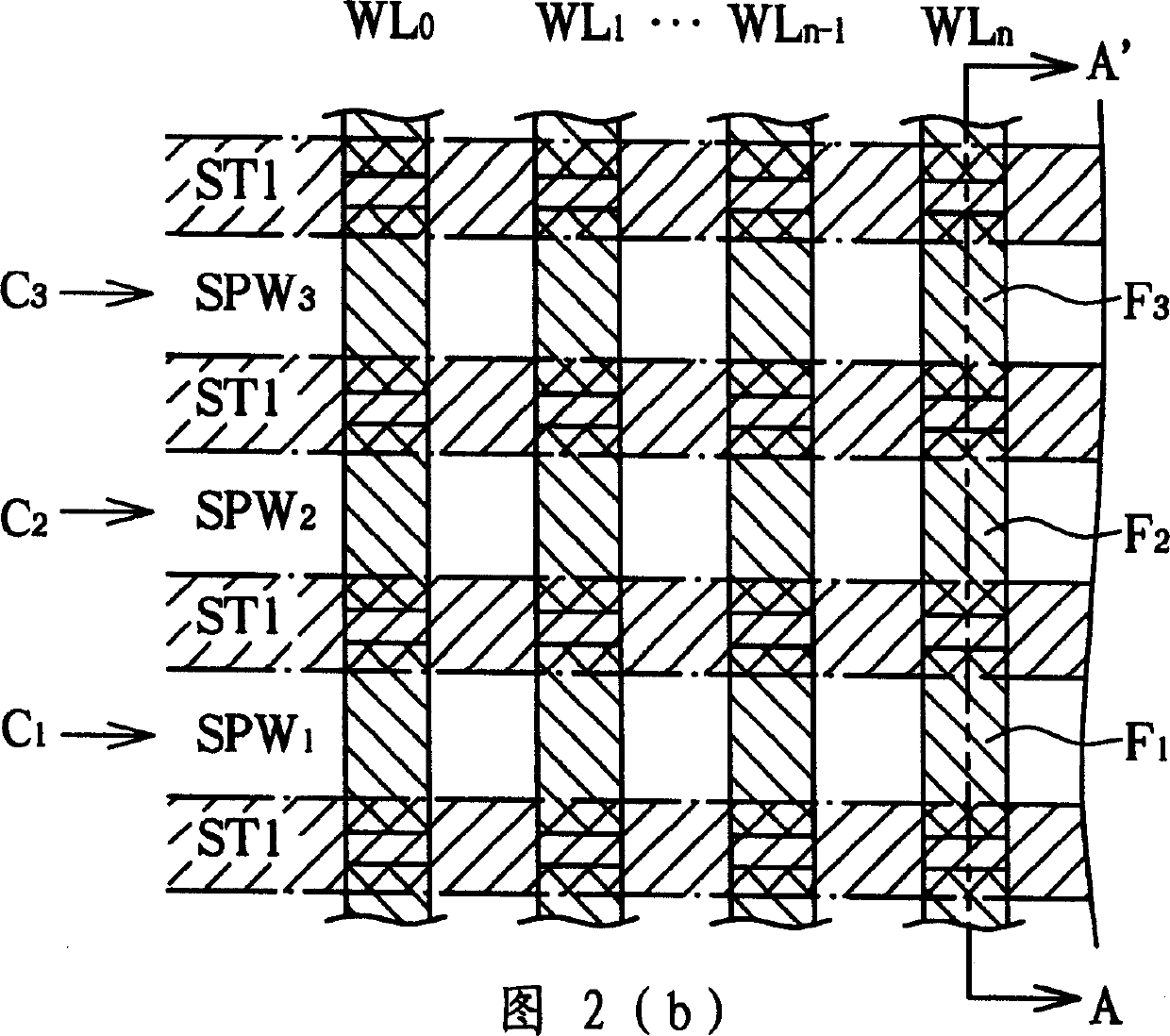

[0036] Please refer to FIG. 2( a ). FIG. 2( a ) is a partial cross-sectional structural diagram of the EEPROM 100 according to the first embodiment of the present invention. As shown in FIG. 2, EEPROM 100 is a low-voltage bidirectional FN write / erase NAND flash memory array structure, including a P-type semiconductor deep well (deep P-well, hereinafter referred to as DPW), and a memory cell sharing N-type well (cell N-Well, hereinafter referred to as CNW), a shallow P-well (shallow P-well, hereinafter referred to as SPW) arranged in parallel and isolated from each other by a shallow trench insulation region, used as a buried Type bit line (buried bit line). In Fig. 2(a), only one of the multiple rows of SPWs is displayed: SPW1. A plurality of NAND cell blocks are arranged in the same column and formed on SPW1, and a local bit line (hereinafter referred to as LBL) is arranged above the plurality of NAND cell blocks. For the convenience of describing the present invention, onl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More