Phase-locked loop having phase detector error signal reshaping and method thereof

A technology of phase error and phase-locked loop, which is applied to the automatic control of power and electrical components, etc., can solve the problems of fast response time, unsatisfactory, and insufficient response time, and achieve the effect of reducing the dead zone

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

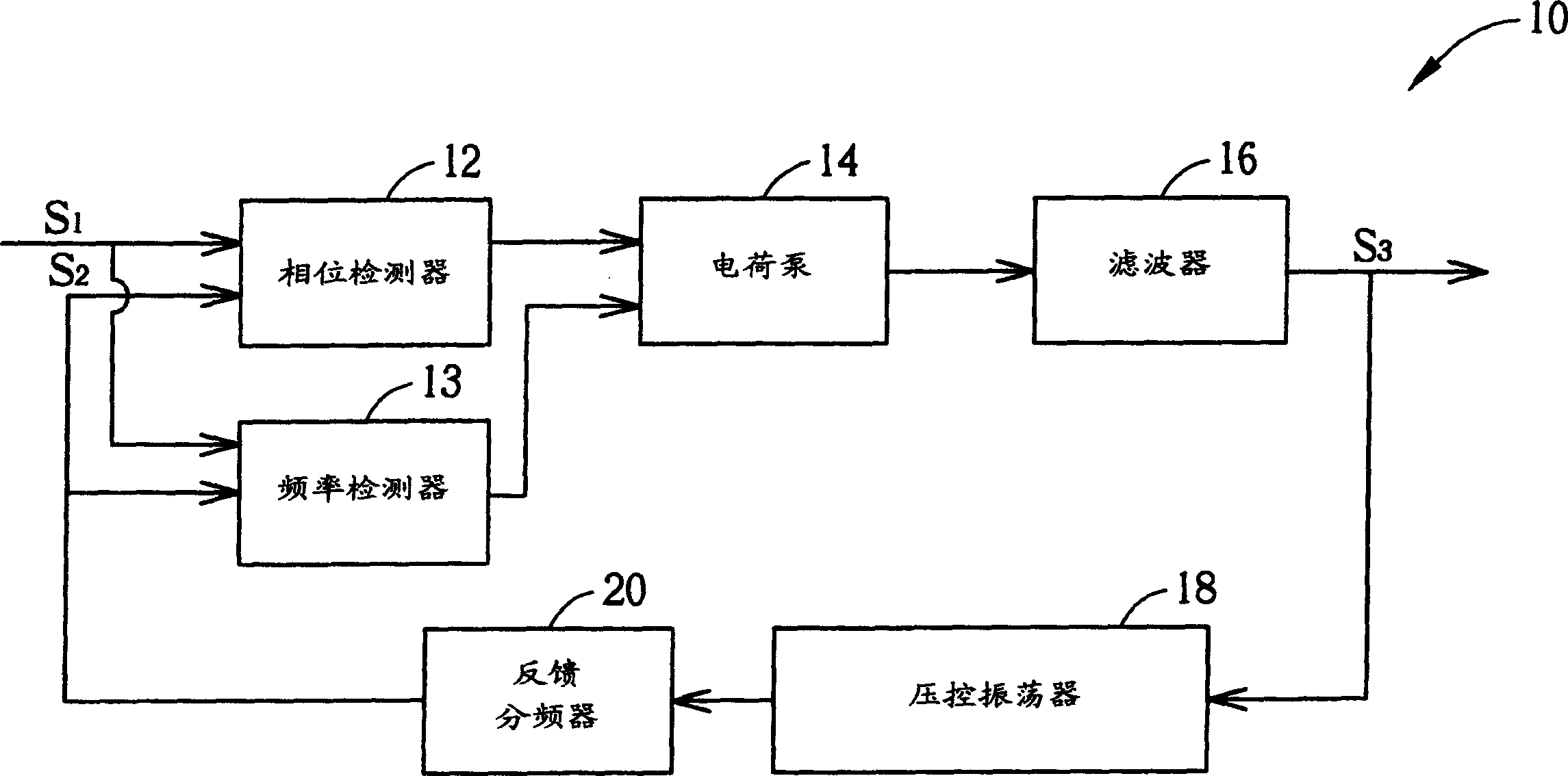

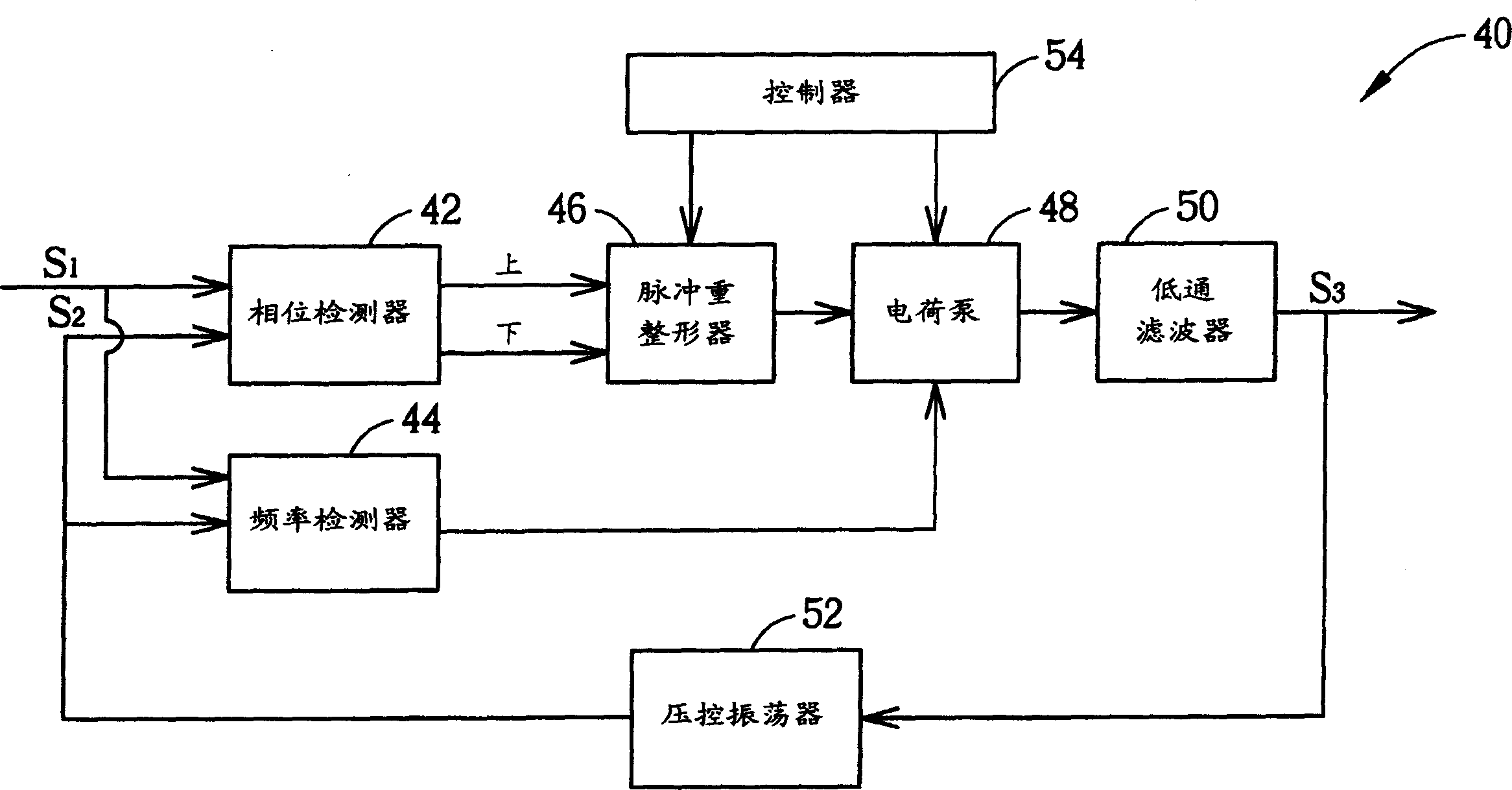

[0032] This paper will illustrate the present invention with two examples. The PLL of the first embodiment of the present invention includes a frequency detector and a controller, while the second embodiment does not have the controller. Furthermore, the first embodiment of the present invention utilizes a pulse reshaper as a signal reshaper.

[0033] see image 3 , image 3 It is a block diagram of a phase-locked loop 40 according to the first embodiment of the present invention. The PLL 40 includes a phase detector 42 and a frequency detector 44 for receiving an input signal S1 and a feedback signal S2. The phase detector 42 is connected to a pulse reshaper 46 that reshapes the pulses of the phase error signal from the phase detector 42 . The PLL 40 further includes a charge pump 48 which receives the signals from the pulse reshaper 46 and the frequency detector 44 and outputs a charge pump signal to the low-pass filter 50 . The low-pass filter 50 outputs an output sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More