Loading method for ensuring to load programmable part reliably

A reliable and device-based technology, applied in the field of delayed loading, can solve problems such as negative impact on chip life and reliability, chip damage, etc., to avoid side effects and ensure correctness and reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

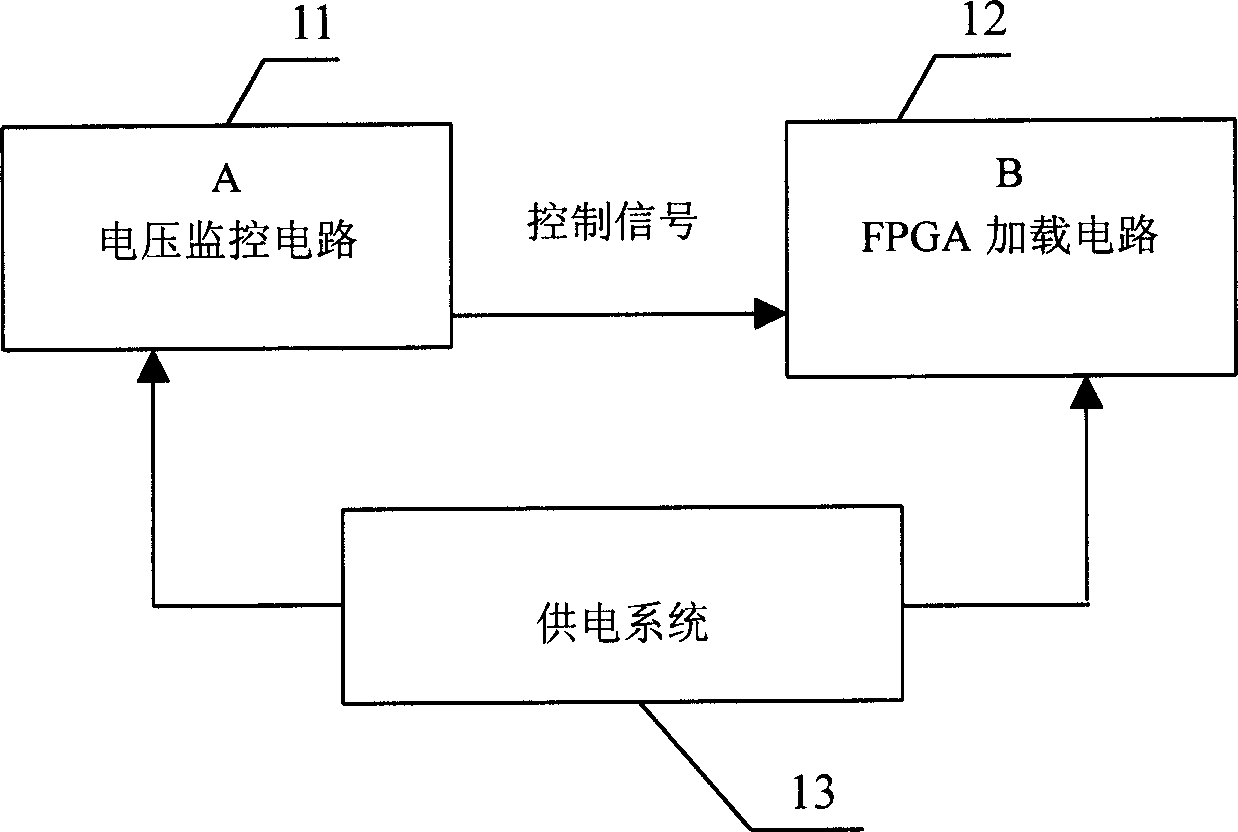

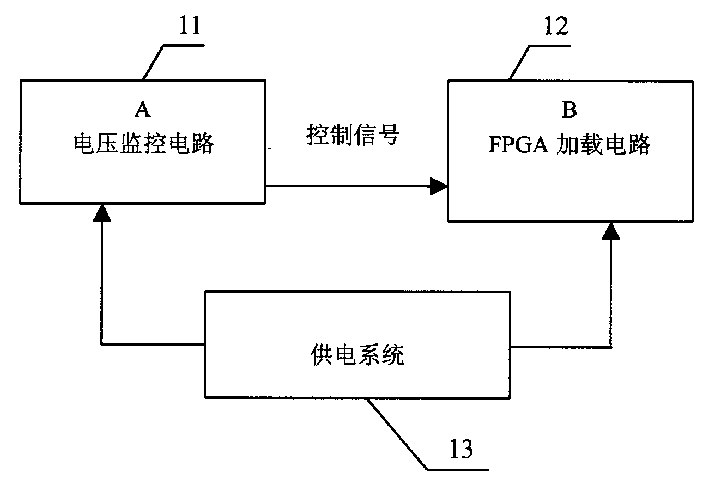

[0013] The invention utilizes the voltage detection function of the voltage monitoring chip to realize accurate monitoring of the voltage, thereby obtaining a reliable time to start the loading action of the FPGA. This solution consists of the following two parts: a voltage monitoring circuit 11 and an FPGA loading circuit 12 . The relationship between the two see figure 1 . The power supply circuit 13 supplies power to both, which will be described in detail below.

[0014] 1. Voltage monitoring circuit

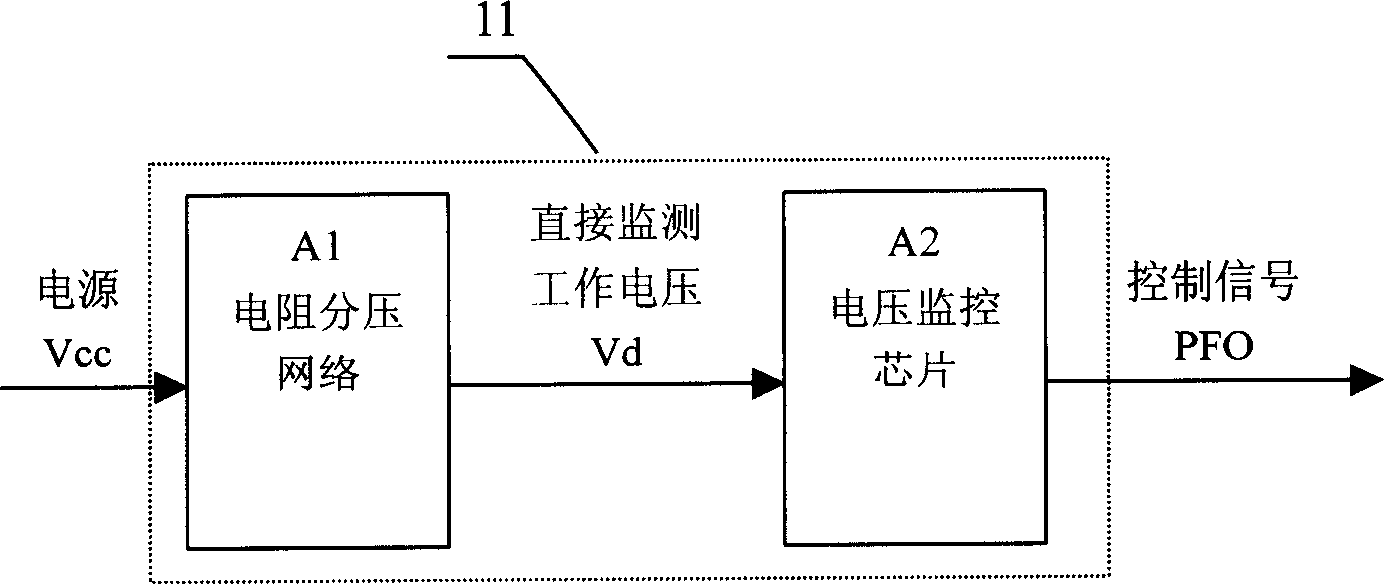

[0015] Voltage monitoring circuits can also be subdivided into figure 2 The two parts shown.

[0016] A2 is the voltage monitoring chip part of this circuit. In addition to monitoring the power supply voltage, usually this type of chip can also provide a PFI pin to monitor a specific voltage value Vd. When the voltage value Vd on the PFI pin is greater than When Vpfi (Vpfi is the threshold voltage of the voltage monitoring circuit), the corresponding output pin PFO out...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More