Self-testing method and apparatus for synchronous dynamic random memory

A random access memory, synchronous dynamic technology, applied in the direction of instruments, error detection/correction, electrical digital data processing, etc., can solve SDRAM SDRAM controller failure, timing difficult to meet the requirements, data path paralysis and other problems, to increase maintainability, The effect of increasing complexity and increasing reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

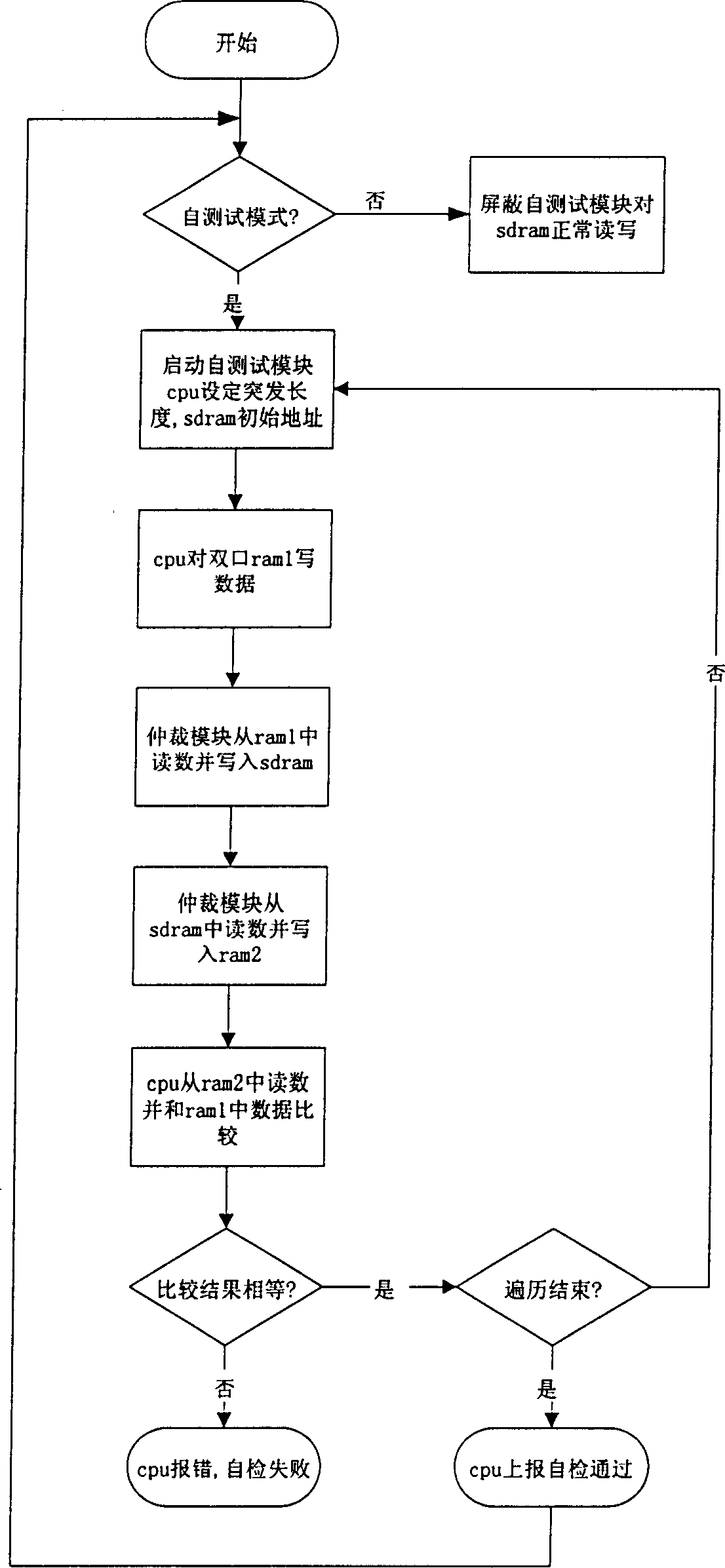

[0019] The present invention embeds an SDRAM self-test module in the module of the flow control unit to realize normal business. The CPU performs self-test on the SDRAM at the beginning of power-on. There is no mutual influence between the self-test state and the normal working state, which can greatly increase the reliability and testability of the SDRAM part.

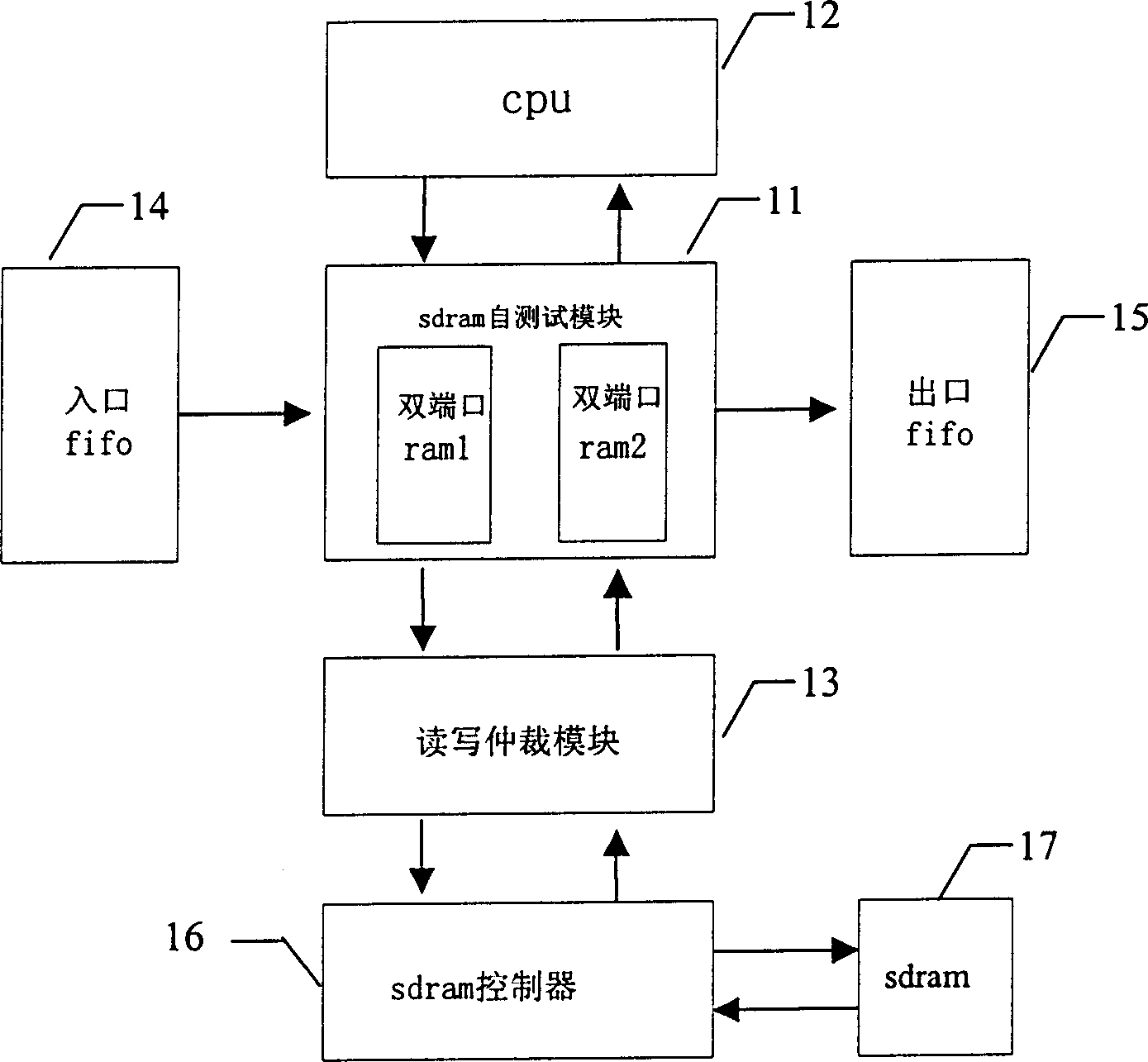

[0020] Such as figure 1 As shown, the SDRAM self-test module 11 is embedded in the system flow control unit, and is connected with the CPU 12 and the read-write arbitration module 13 respectively, and is also connected with the data input / output ports 14 and 15. It includes a first dual-port RAM1 and a second dual-port RAM1. Port RAM2 and its read and write control logic, others also include the switching switch between the entrance fifo, the exit fifo and the dual-port RAM.

[0021] When the system is in the normal working mode, that is, when the business is normally transmitted, the SDRAM self-test module 11 is shi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More