Processor and compiler

A processor and compiler technology, applied in electrical digital data processing, instruments, memory systems, etc., can solve problems such as the increase in circuit size, and achieve the effects of reducing energy consumption, reducing the number of times, and reducing the bus width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

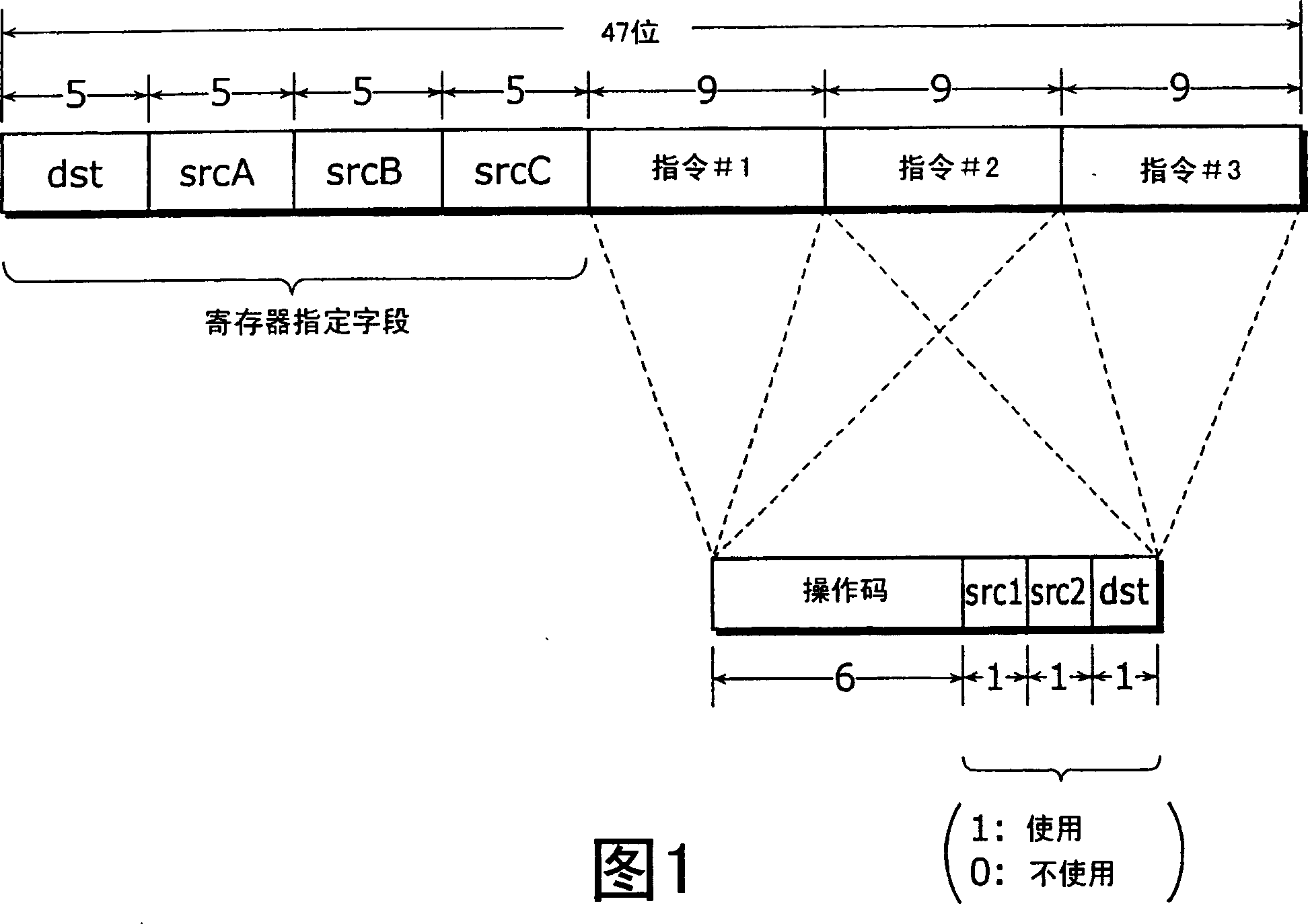

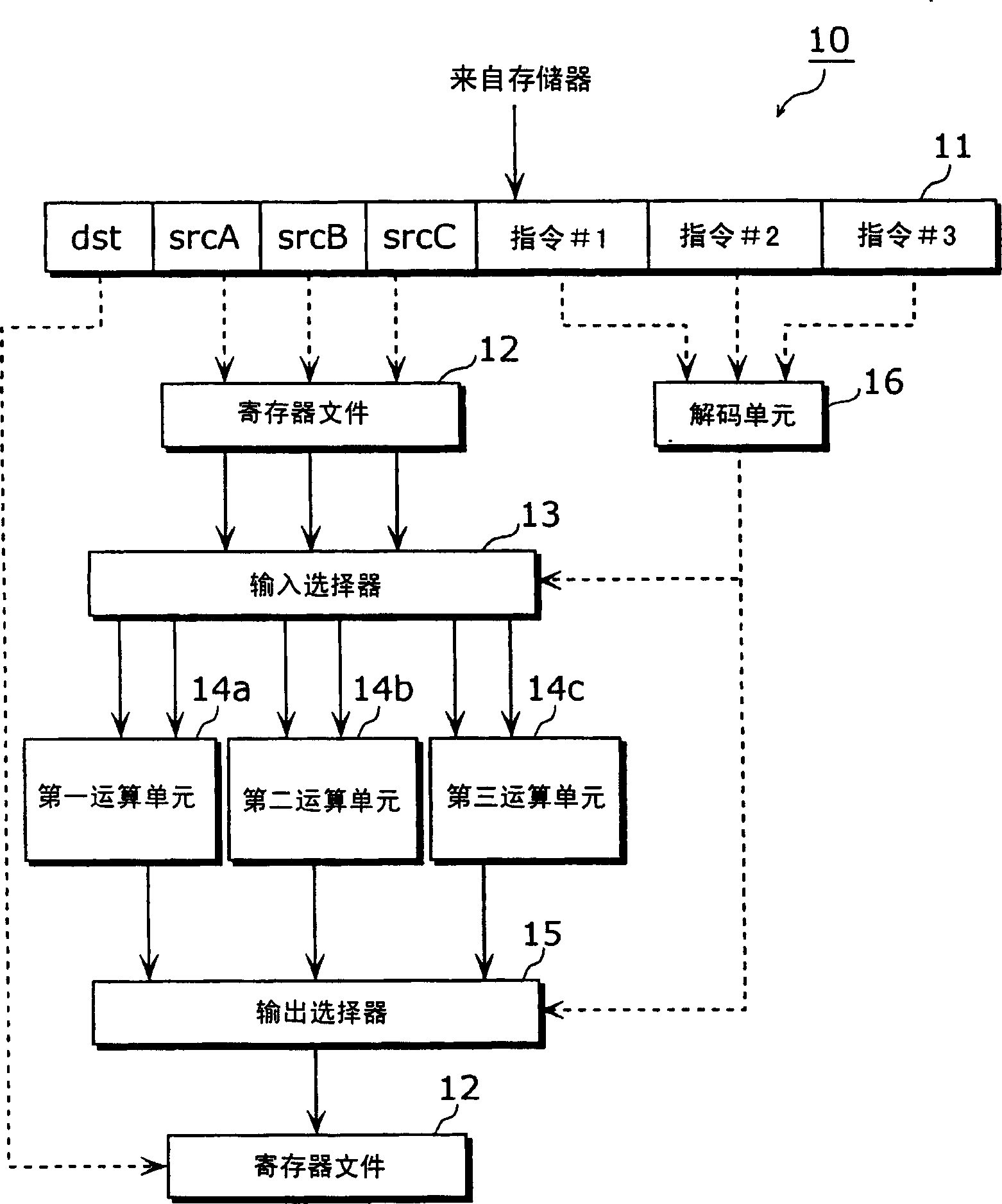

[0049] FIG. 1 is a diagram showing the instruction format of a very long instruction word executed by a VLIW processor according to a first embodiment. As shown in FIG. 1, the VLW is 47 bits long and includes a register designation field and three instruction fields.

[0050] The register designation field is a common field that designates registers used in the three instruction fields, and includes four register designation areas (one destination register dst and bit fields designating three source registers srcA-srcC). Each of the register specifying areas dst and srcA-srcC has 5 bits for specifying one register among 32 general-purpose registers (register files) included in the VLIW processor.

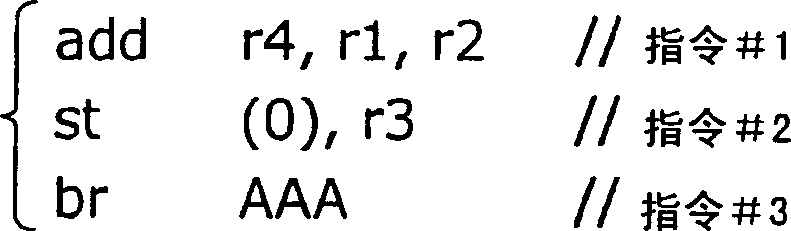

[0051] The three instruction fields (first-third instruction fields) are arranged into three instructions (instructions #1-#3) that can be executed in parallel. In the case of register arithmetic instructions, a 6-bit opcode and a 3-bit operand are placed in each instruction field....

no. 2 example

[0088] Next, a VLIW processor and compiler according to the second embodiment will be explained. The VLIW processor according to the second embodiment executes a VLIW of a characteristic instruction format similar to that of the first embodiment. However, the VLIW processor according to the second embodiment includes, in addition to the register file, temporary registers that temporarily hold operation results. The difference between the VLIW processor and the compiler according to the second embodiment and the first embodiment will be mainly explained below.

[0089] attached Figure 6 is an instruction format representing a very long instruction word executed by the VLIW processor according to the second embodiment. as attached Figure 6 As shown in , the VLOW is 56 bits long and includes a register designation field and three instruction fields.

[0090] As with the first embodiment, each of the register designation areas dst and srcA-srcC included in the register desig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More