Method for implanting ions in semiconductor device

A technology of ion implantation and semiconductor, which is applied in semiconductor/solid-state device manufacturing, instruments, table utensils, etc., and can solve problems such as differences

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

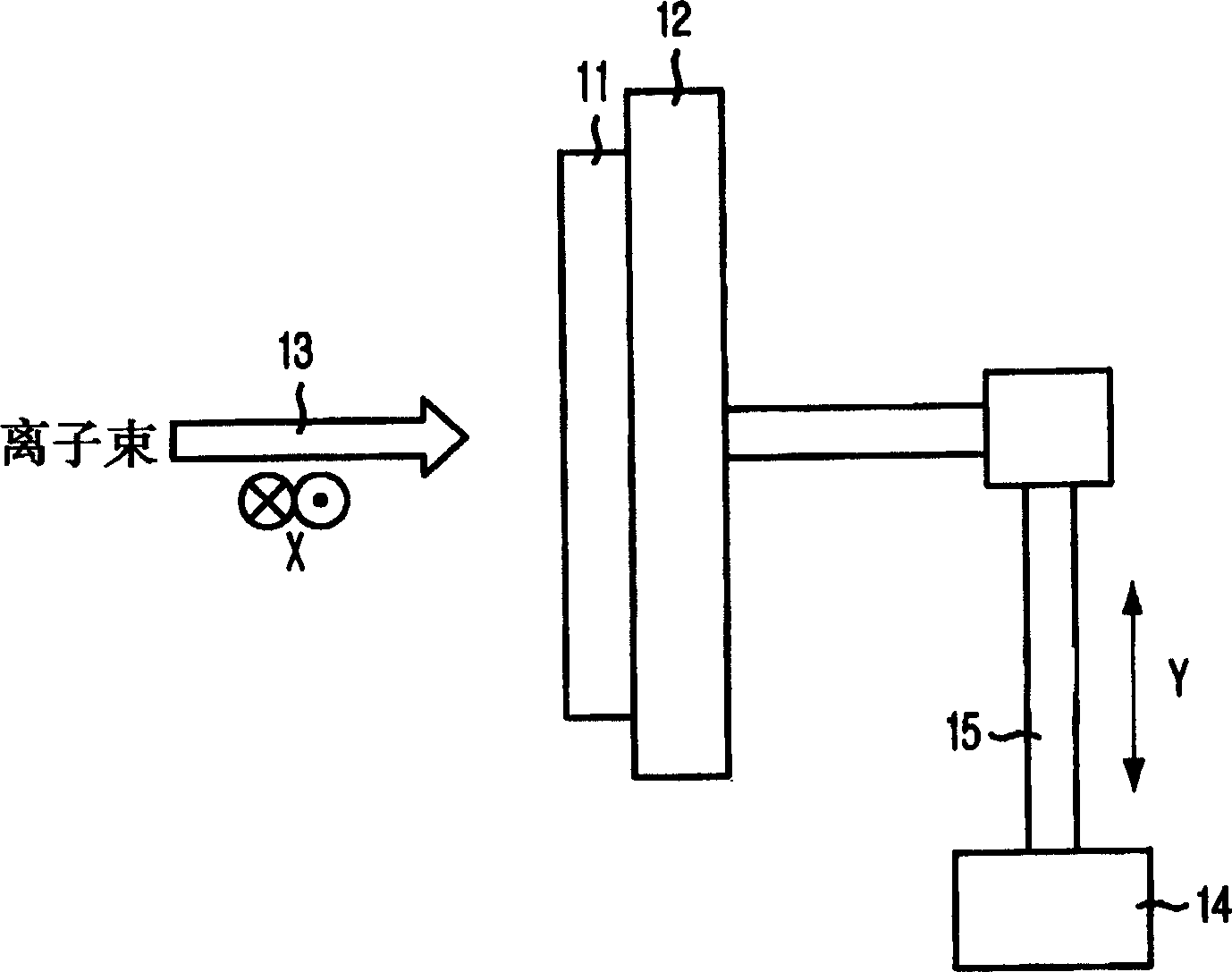

[0033] The ion implantation method in the semiconductor device according to the first embodiment of the present invention will be described in detail with reference to the accompanying drawings.

[0034] According to the present invention, the reciprocating scanning speeds in the X and Y directions are set differently according to the position of the substrate used in the non-uniform ion implantation method.

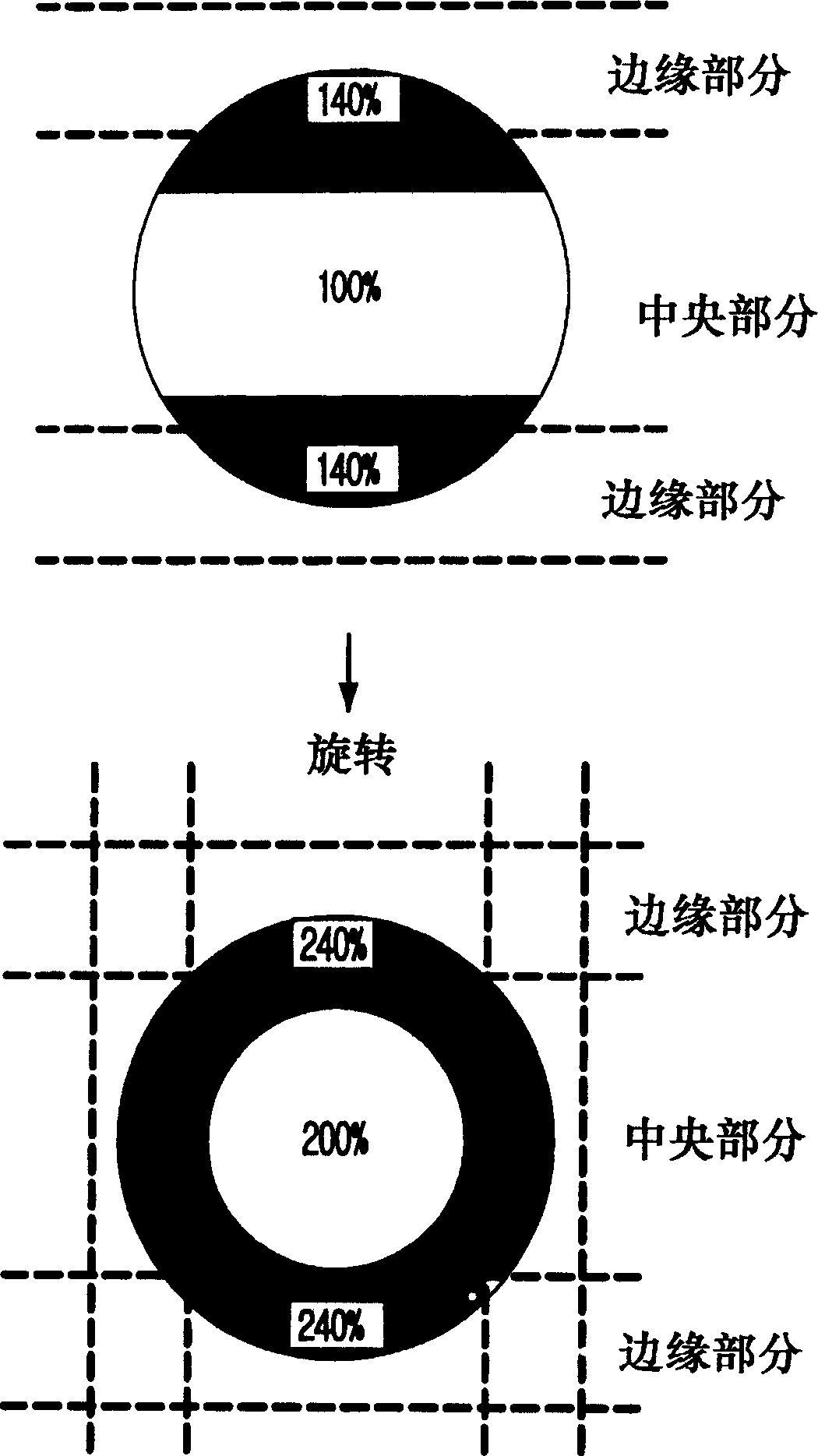

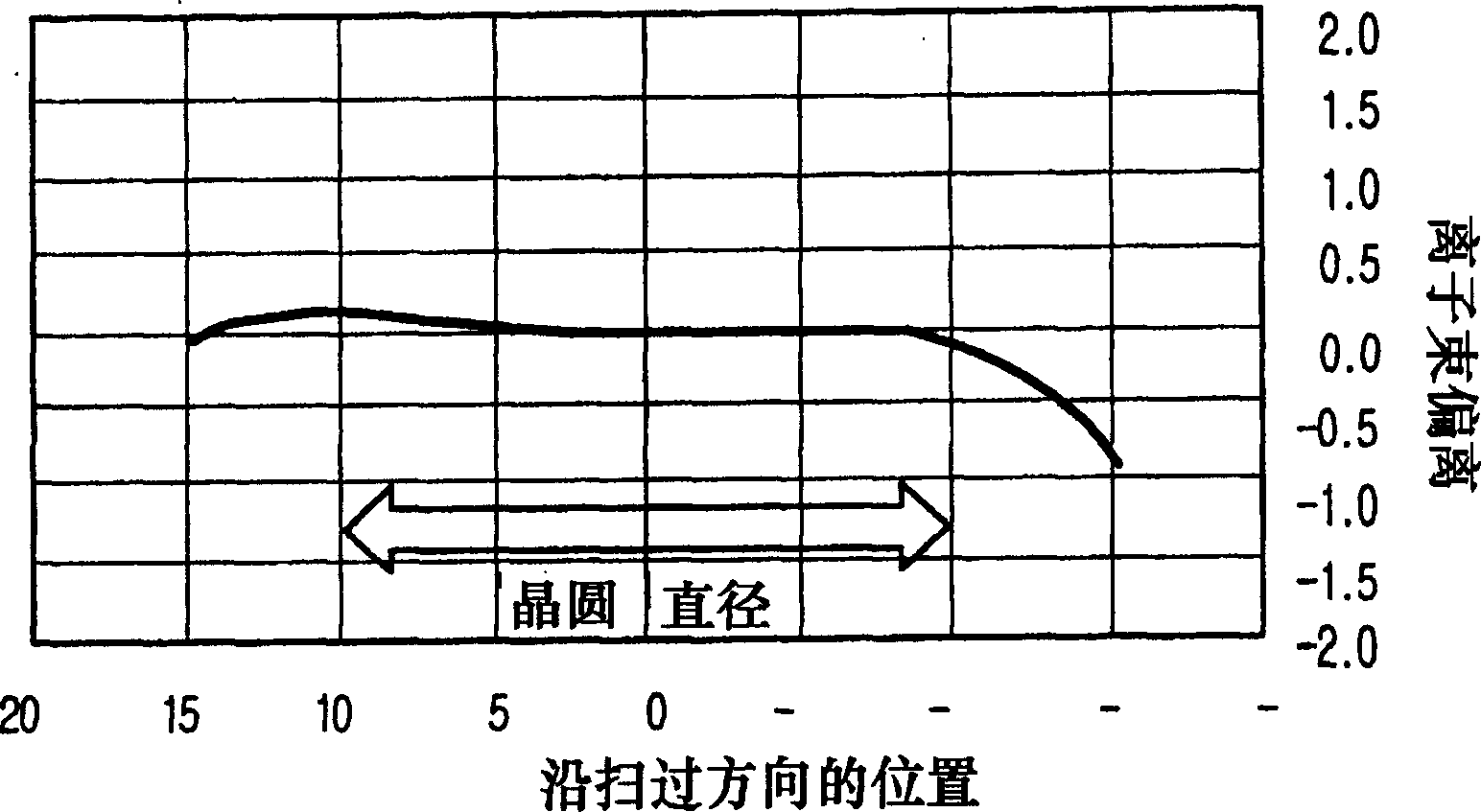

[0035] The present invention is based on a technical principle to identify the critical dimension (CD) of a gate in a substrate without causing differences in semiconductor device parameters in the substrate by performing a non-uniform ion method.

[0036] For example, if the CD of the gate in the central portion of the semiconductor is greater than in the edge portion of the substrate, the central portion of the semiconductor device will have a higher threshold voltage (V T ). Therefore, at the threshold voltage (V T ), for example, by non-uniform ion implantation, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com