Wafer testing device and method with automatic reversion function

A technology of automatic reply and wafer testing, which is applied in the direction of semiconductor/solid-state device testing/measurement, etc., can solve problems such as low production efficiency, increased production cost, and extended testing time, so as to reduce the overall process time and cost and improve production. efficiency effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

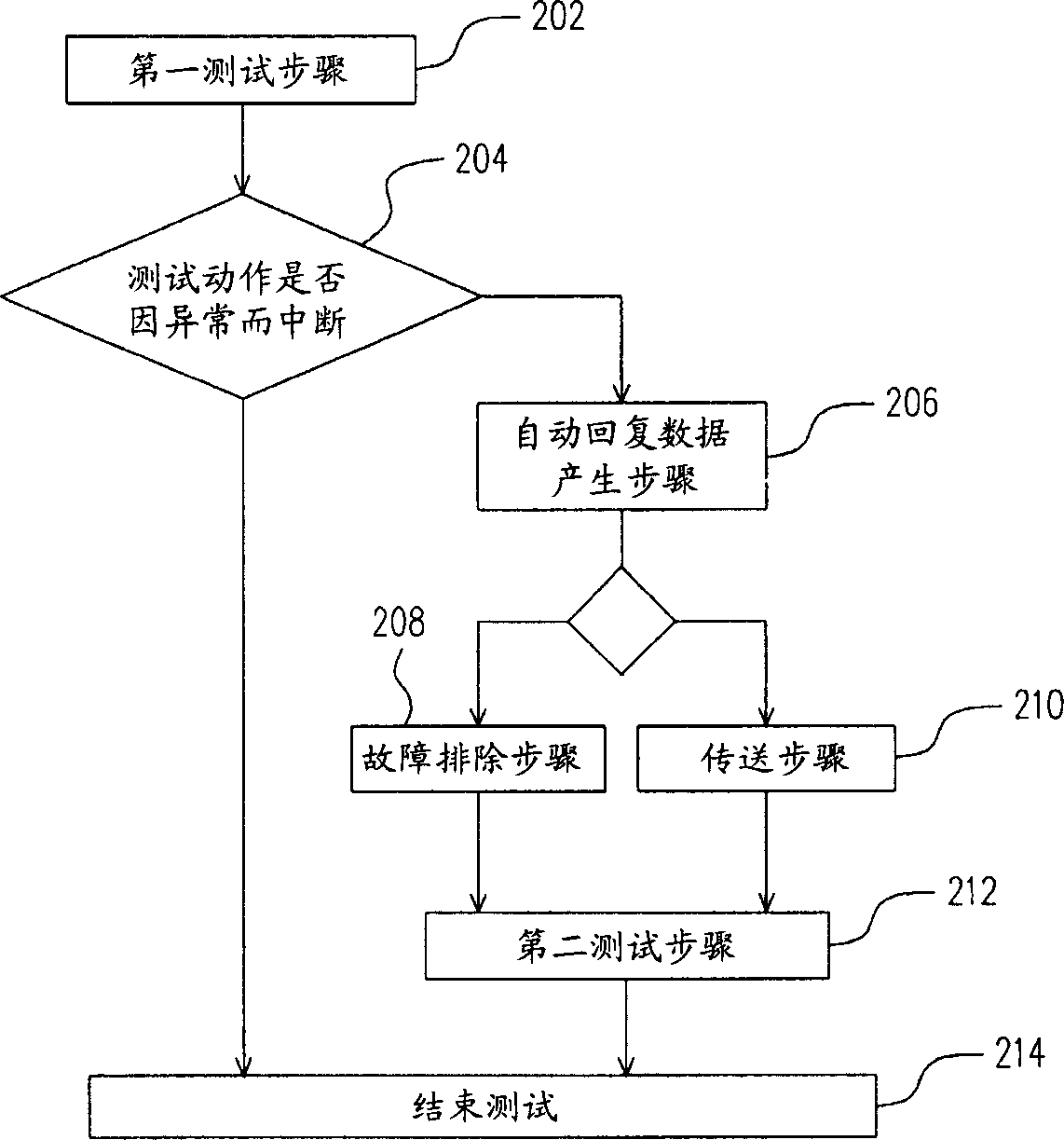

[0041] The wafer testing device and wafer testing method with automatic recovery function of the present invention are suitable for performing operations such as wafer needle testing, laser repairing or final testing in the semiconductor process on a plurality of dies on the wafer.

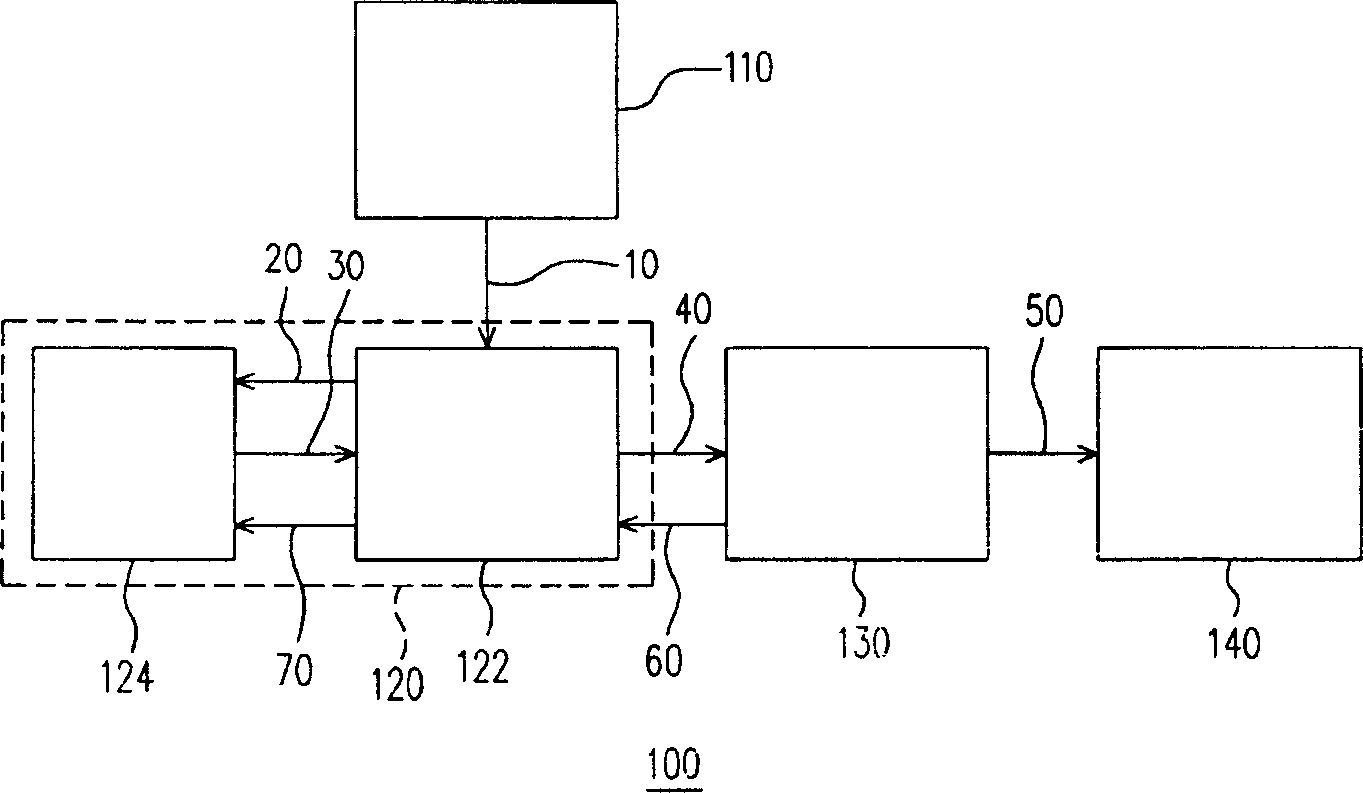

[0042] Please refer to figure 1 , which shows a schematic view of the wafer testing device with automatic recovery function of the present invention. The wafer testing device 100 includes, for example, a host system 110, a test system (tester) 120, a real-time access module 130, and a database 140, wherein the host system 110 is, for example, a process control system (Manufacturing Execution System, MES), which is It is used to control the overall wafer testing process, including parameters such as wafer movement, process type, wafer batch number, wafer serial number, and process time.

[0043] please refer again figure 1, the test system 120 includes, for example, a control module 122 and a tes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More