Method for verification of resolution enhancement techniques and optical proximity correction in lithography

An optical proximity correction, resolution enhancement technology, applied in the fields of originals for optomechanical processing, optics, special data processing applications, etc., which can solve problems such as inter-stage interactions that are not easy to define or measure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

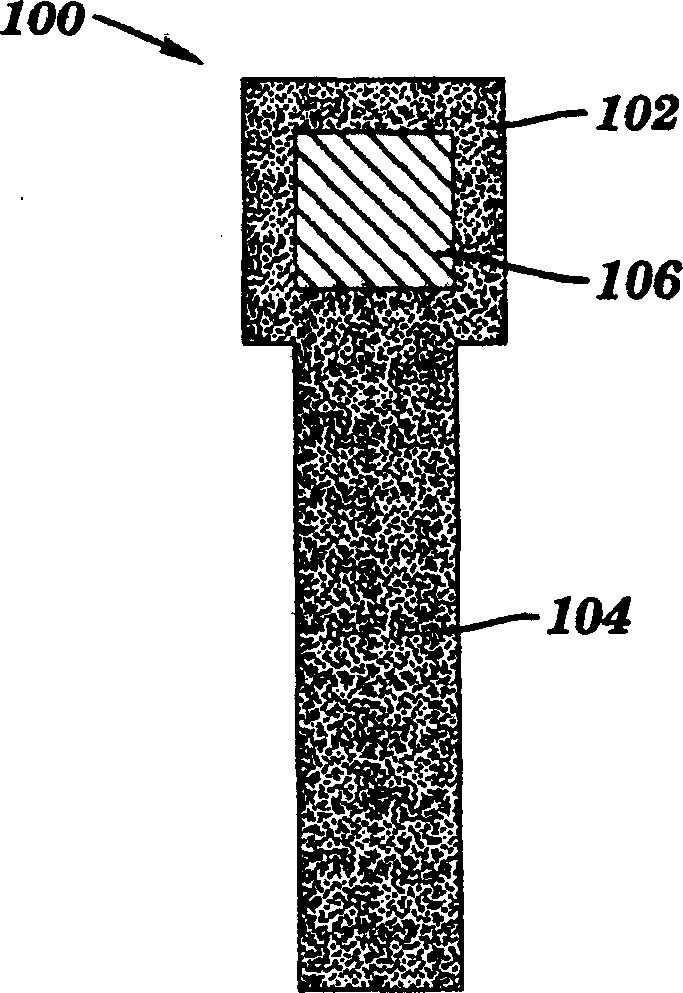

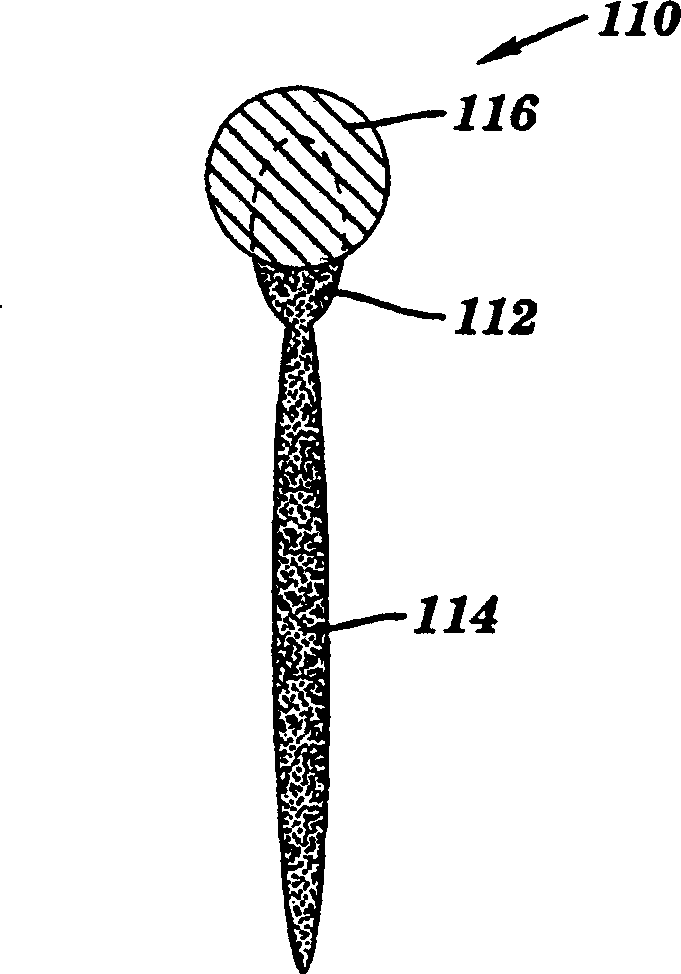

[0020] Referring first to FIG. 1( a ), there is shown a portion of an example integrated circuit layout 100 featuring a polymer conductor (PC) 102 (shown in solid color) and an associated conductive path 104 that communicates with a contact area (CA) 106 (shown as diagonal hatching) together solder the connection to the PC to the previous wiring level. As noted above, when a photolithographic system attempts to print circuit elements whose dimensions are close to the wavelength of the exposing radiation, the shape of the resulting printed circuit element becomes significantly different from the corresponding pattern on the mask. Therefore, to provide qualitative insight into patterning specific layout shapes, simulated wafer images of layout shapes have been enhanced using RET and OPC. FIG. 1( b ) thus shows an example diagram of one possible simulated wafer image 110 of the design layout 100 of FIG. 1( a ). Note that the simulated wafer image 110 shows deformations in the si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More