Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of semiconductor substrate damage and difficult filling, and achieve the effect of not being easily damaged

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

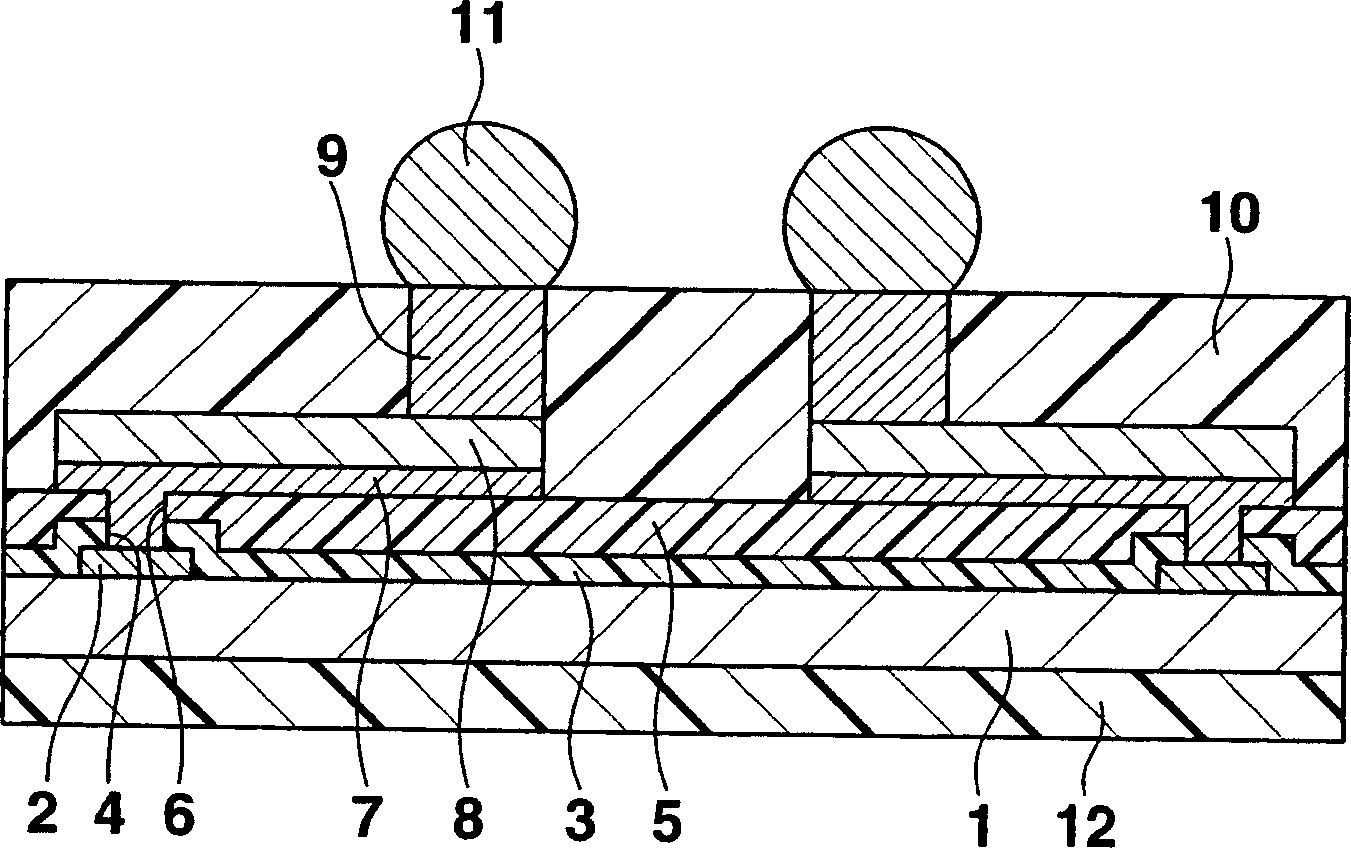

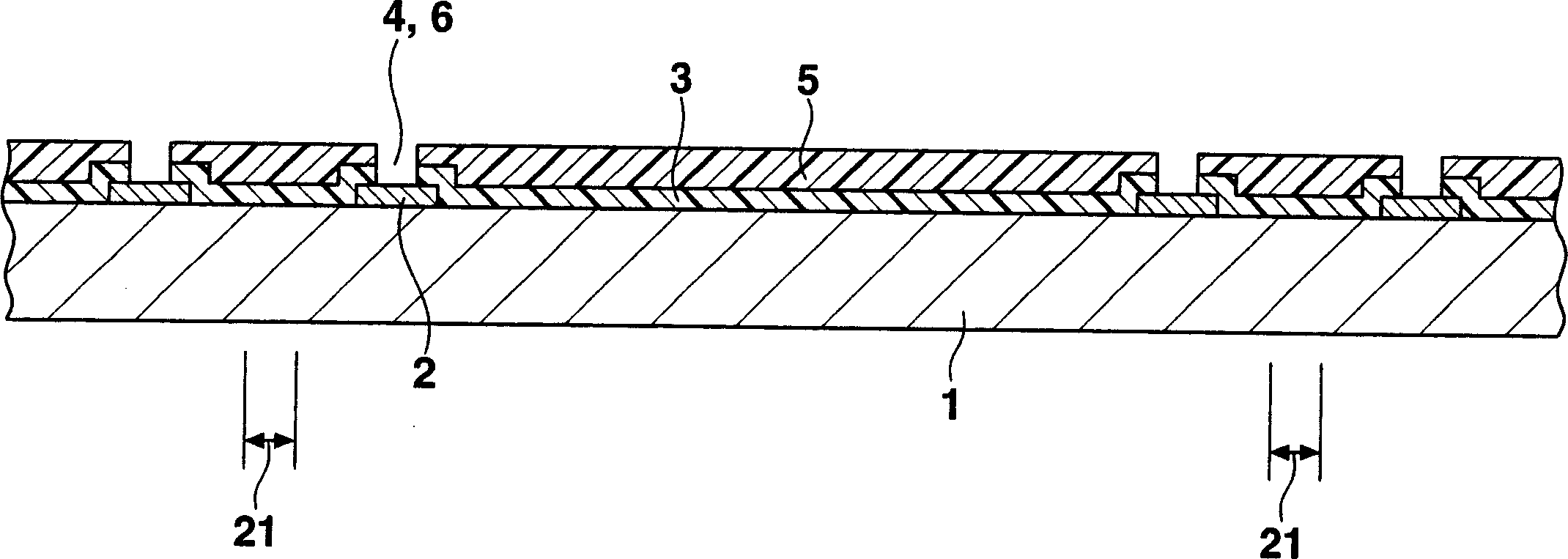

[0034] figure 1 A cross-sectional view of a semiconductor device as an embodiment of the invention is shown. This semiconductor device is generally called a CSP (chip size package), and includes a silicon substrate (semiconductor substrate) 1 . An integrated circuit (not shown) having a predetermined function is provided on the upper surface of the silicon substrate 1 , and a plurality of connection pads 2 made of aluminum-based metal or the like are provided on the periphery of the upper surface to connect to the integrated circuit.

[0035] An insulating film 3 made of silicon oxide or the like is provided on the upper surface of the silicon substrate 1 except for the central portion of the connecting pad 2, and the central portion of the connecting pad 2 is opened through the opening 4 provided in the insulating film 3. exposed. A protective film 5 made of epoxy resin, polyimide resin, or the like is provided on the upper surface of the insulating film 3 . In this case, ...

no. 2 Embodiment approach

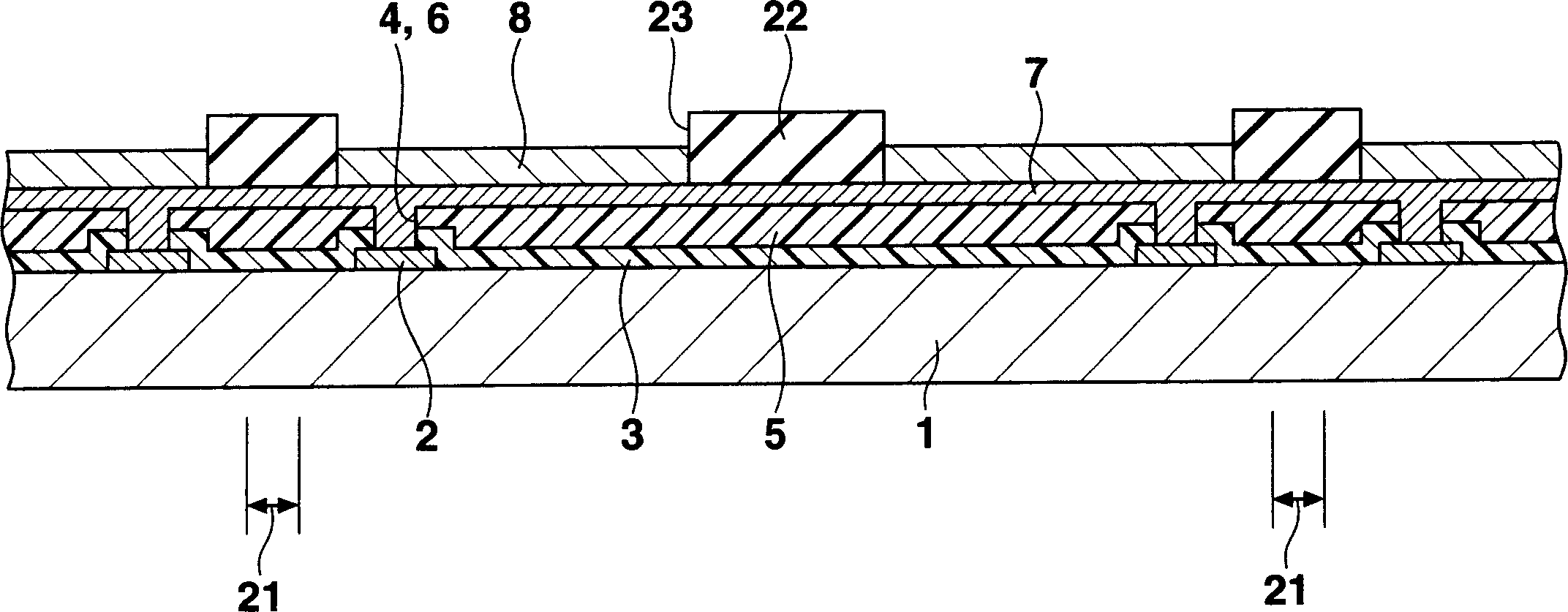

[0053] Figure 14 The second embodiment of the invention is shown. An integrated circuit (not shown) with a predetermined function is provided on the upper surface of the silicon substrate, and a plurality of connection pads 2 made of aluminum-based metal or the like are provided on the periphery of the upper surface to connect to the integrated circuit.

[0054] An insulating film 3 made of silicon oxide or the like is provided on the upper surface of the substrate 1 , and the central portion of the connection pad 2 is exposed through an opening 4 provided in the insulating film 3 . A protective film 5 made of epoxy resin or polyimide resin is provided on the upper surface of the insulating film 3 . In this case, an opening 6 is provided in a portion of the protective film 5 corresponding to the opening 4 of the insulating film 3 .

[0055] A base metal layer 7 made of copper or the like is provided on the upper surface of the protective film 5 . Wiring 8 made of copper is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More