System for improving SRAM process EPGA design safety by asynchronous circuit

An asynchronous circuit and process technology, applied in computing, electrical digital data processing, special data processing applications, etc., can solve problems such as inconsistent production processes, increased costs, and reduced system stability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

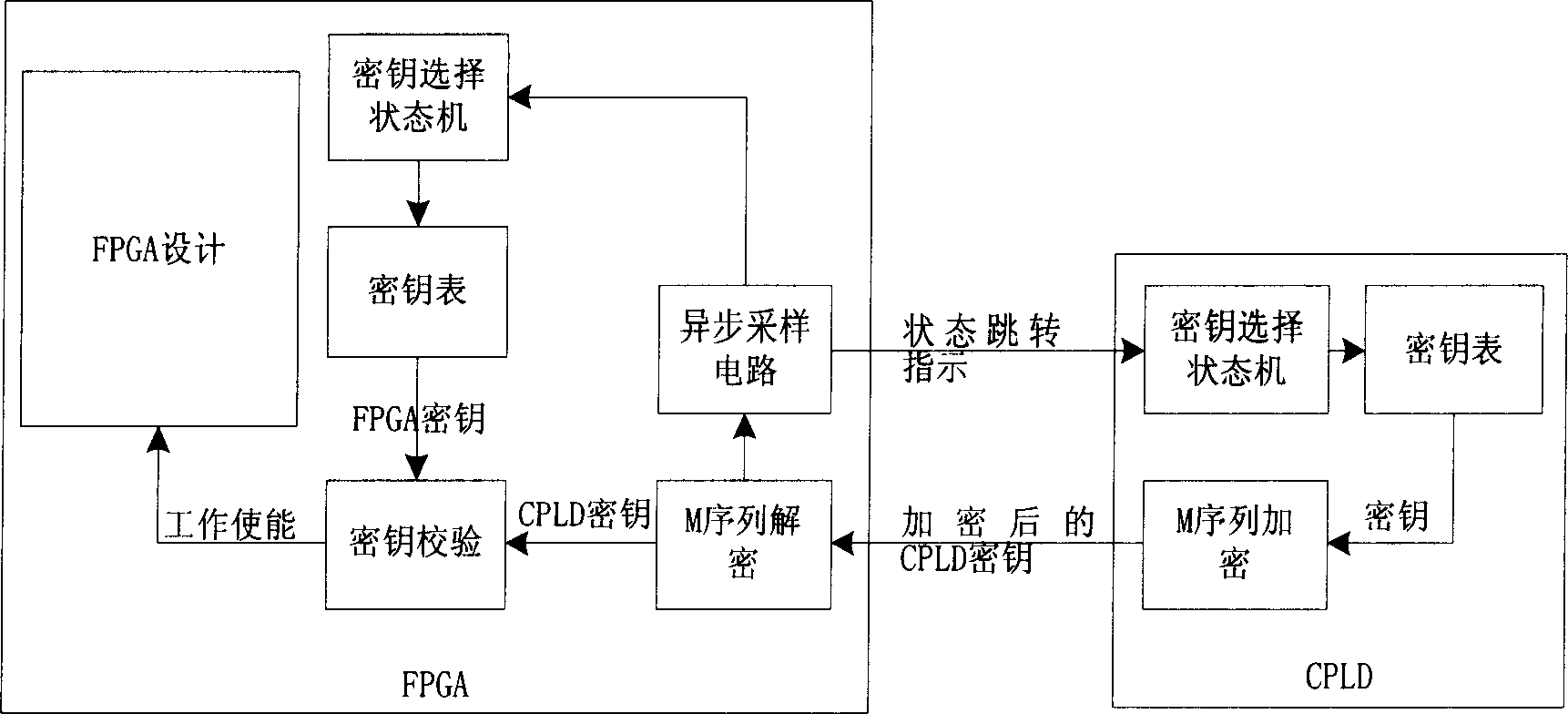

[0044] figure 1 It is the functional block diagram of the whole system. In the following, the function and realization of each functional module will be introduced according to the generation and verification sequence of the verification information of the whole system.

[0045] (1) Asynchronous sampling circuit

[0046] The asynchronous sampling circuit uses one clock to sample the signal driven by another clock. Due to the inconsistency of different clock frequencies and the clock jitter caused by various random factors, an unpredictable random sequence will be generated. In this system, 3 Bits are sent to the key selection state machine to randomly generate a key. In addition, since the signal phase difference of the clock changes each time the power is turned on, the sequence generated on the circuit board is also different.

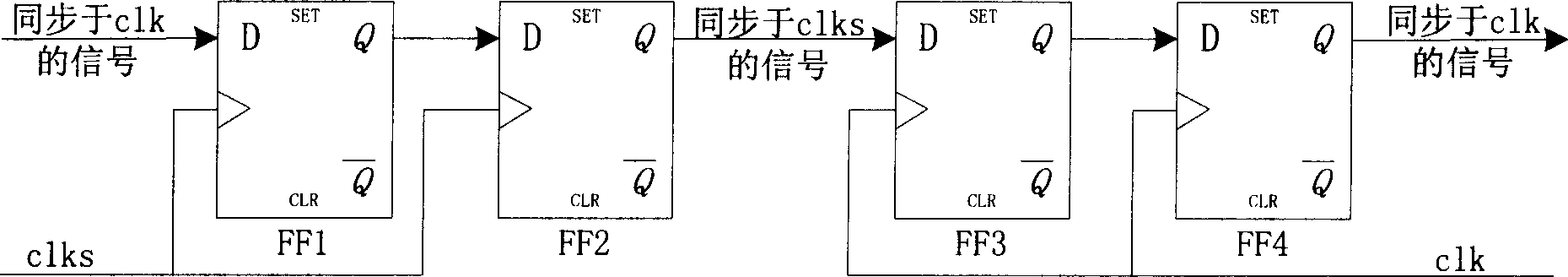

[0047] figure 2 A schematic diagram of a single-bit asynchronous sampling circuit is shown. In the figure there are 4 flip-flops (FF1, FF2, FF...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More