Clock recovery method and apparatus

A clock recovery and clock signal technology, applied in the field of network communication, can solve the problems of limited operation speed of digital signal processor, increase of system complexity and cost, bandwidth limitation of system phase-locked loop, etc., to achieve improved jitter performance, low jitter, etc. The effect of output, high realization cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0060] Embodiment 1: A clock recovery scheme in which the digital filter is placed outside the phase-locked loop

[0061] This solution is preferably but not limited to be implemented inside the demapping processing chip.

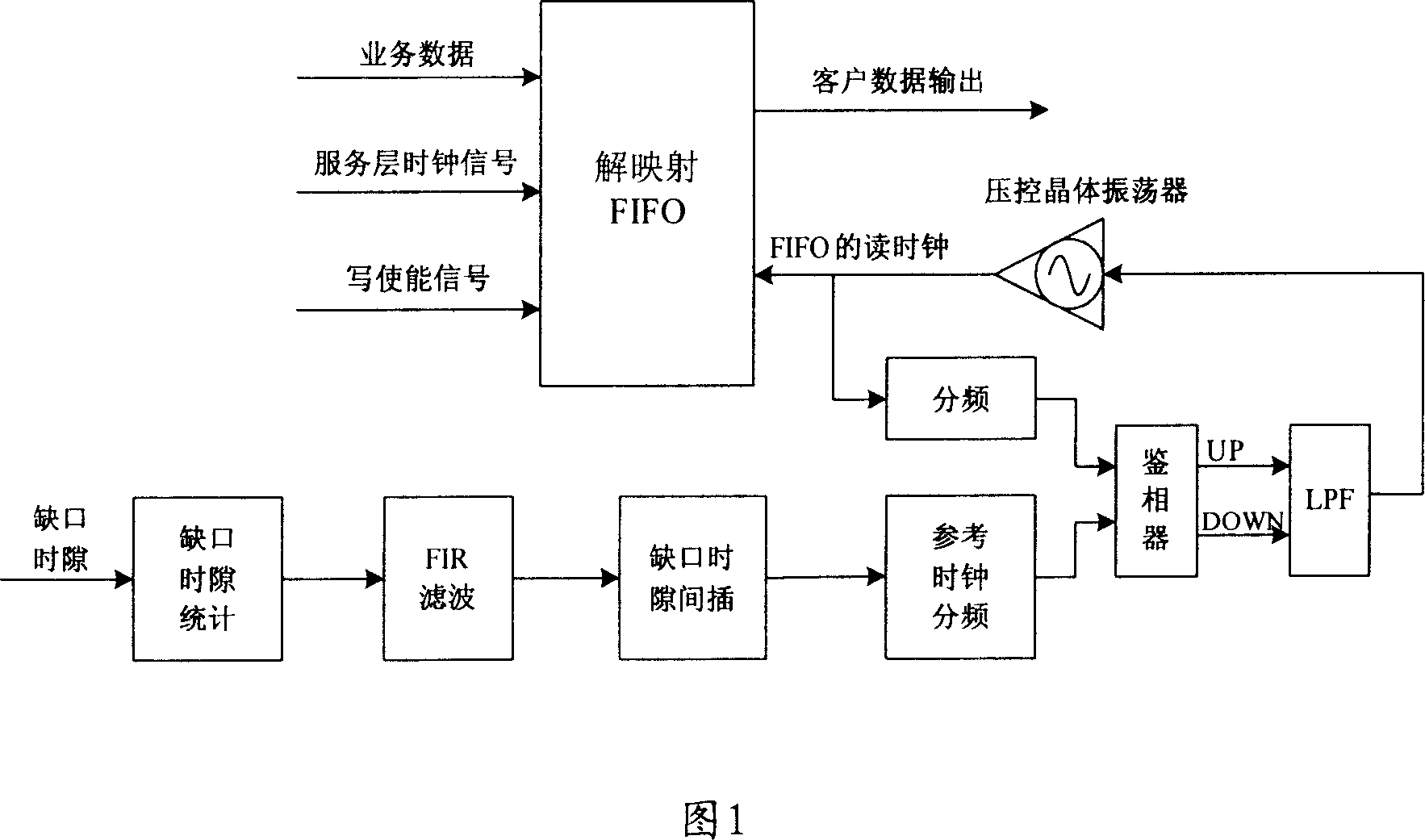

[0062] In this implementation scheme, a demapping circuit with excellent performance can be formed by specifically adopting a digital filter, an external low-pass filter (LPF) and a voltage-controlled crystal oscillator. The digital filter can use FIR (finite length Unit Impulse Response) filter, the corresponding specific implementation circuit structure is shown in Figure 1, in which the FIR filter is used as an example, but the actual application is not limited to the FIR filter.

[0063] As shown in Figure 1, the usual business data processing flow in the corresponding demapping process includes:

[0064] When the signal time slot of the client layer is valid, the write enable signal of the demapping FIFO is valid, so that the customer data can be writ...

Embodiment 2

[0084] Embodiment 2: A clock recovery scheme in which a digital filter is placed inside a phase-locked loop

[0085] For applications where the loop bandwidth is not required, the digital filter can also be placed inside the clock phase-locked loop. The specific implementation structure of the implementation scheme provided by this embodiment is shown in Figure 4, including:

[0086] Write data statistics unit, read data statistics unit, take difference unit and digital filtering unit, wherein, the output of data statistics unit and read data statistics unit are respectively used as the input of difference take unit, and the output of take difference unit is connected to all The above-mentioned digital filter unit, and the digital filter unit is connected with the phase-detection pulse conversion unit of the phase-locked loop.

[0087] The specific implementation of each processing unit included in FIG. 4 will be described respectively below:

[0088] (1) Read data statistic...

Embodiment 3

[0101] Embodiment 3: A solution for improving the jitter performance of the demapping clock by using a digital filter

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More