Directly electric connected crystal covered encapsulation structure of semiconductor chip

An electrical connection, flip chip packaging technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, circuits, etc., can solve the problems of unstable electrical, mechanical and physical quality, high packaging cost, long production cycle, etc. Achieve the effect of improving heat dissipation efficiency, improving electrical quality, and reducing overall height

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

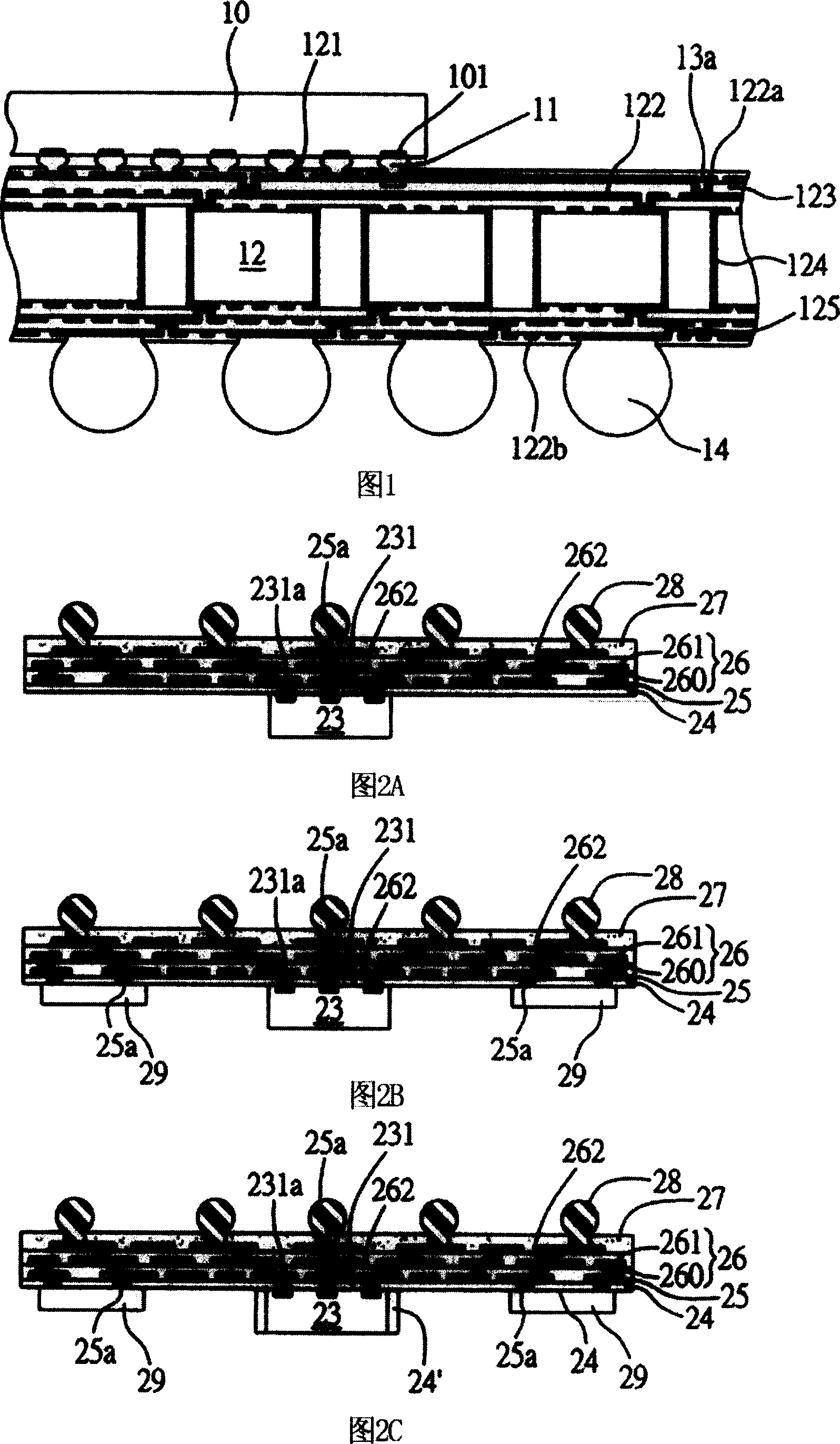

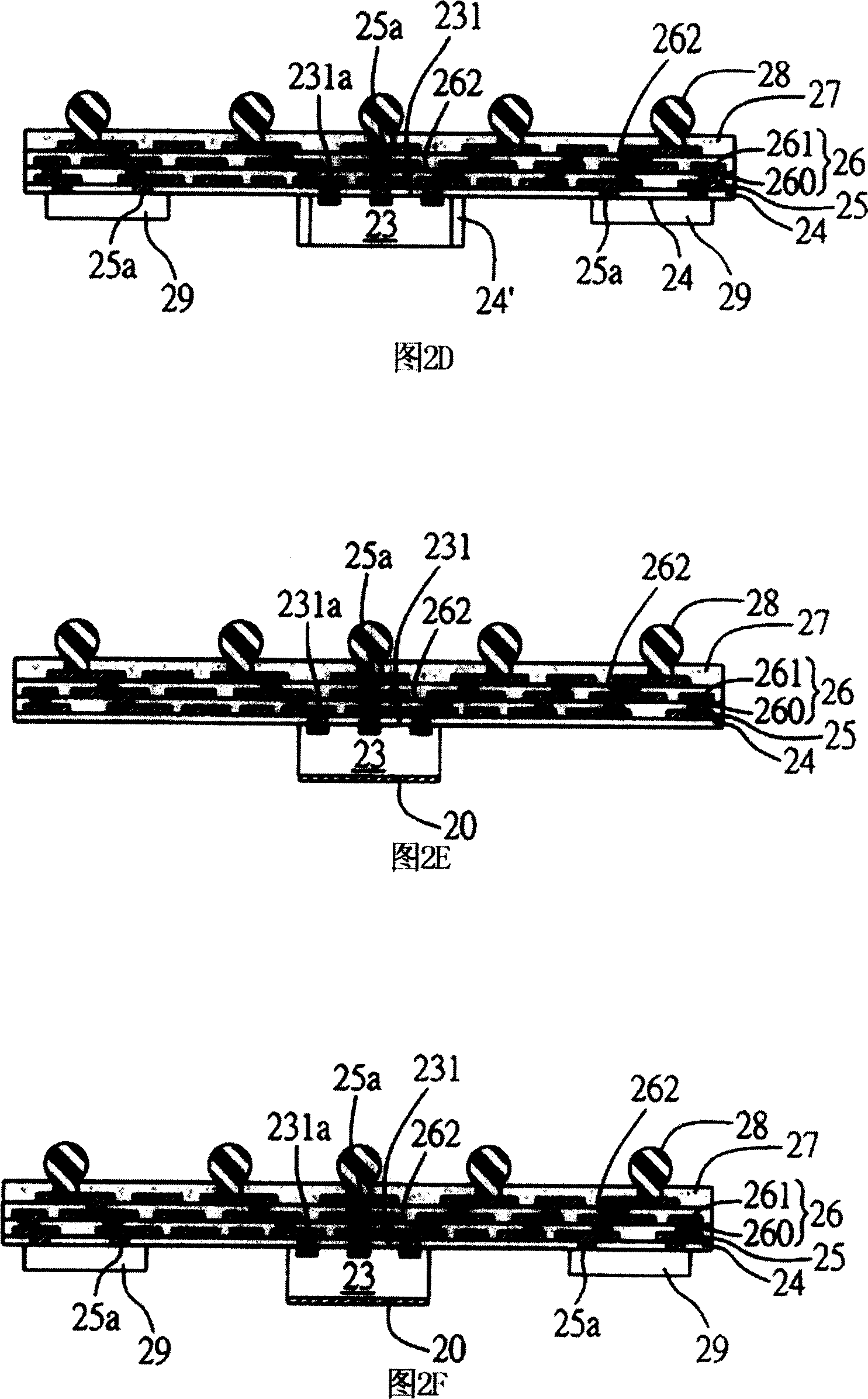

[0022] 2A to 2D are schematic cross-sectional views of Embodiment 1 of the direct electrical connection flip-chip package structure of the semiconductor chip of the present invention. One point to be noted here is that these drawings are simplified schematic diagrams, which only illustrate the basic structure of the present invention in a schematic manner, so only the structures related to the present invention are shown, and the shown structures are not the number of actual implementations , shape and size ratio, the number, shape and size ratio in actual implementation is a selective design, and its composition and layout may be more complex.

[0023] The direct electrical connection flip-chip packaging structure of the semiconductor chip of the present invention shown in FIG. 2A includes: at least one semiconductor chip 23, the semiconductor chip has an active surface 231 and a non-active surface, and the active surface 231 of the semiconductor chip 23 forms There is an ele...

Embodiment 2

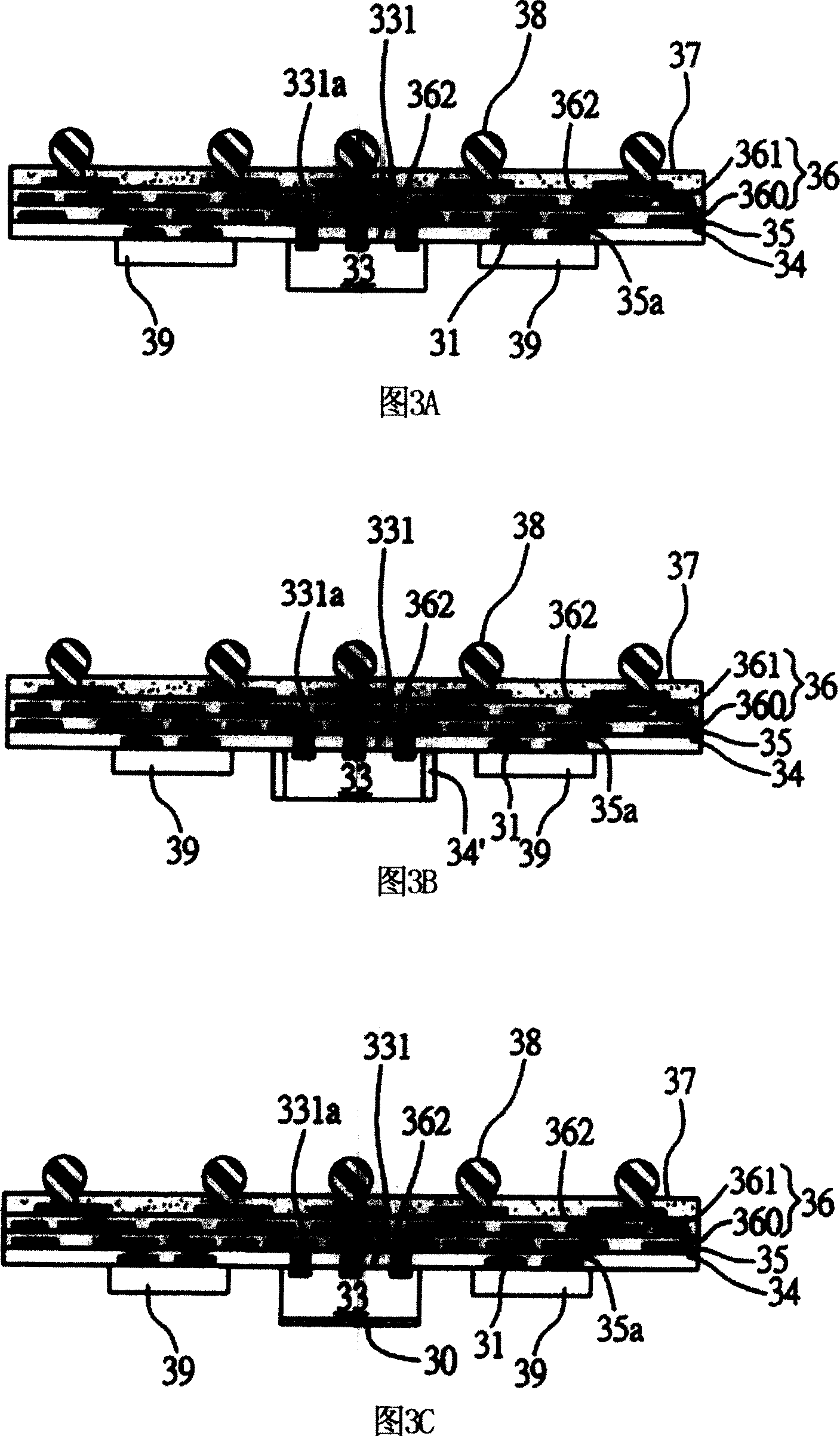

[0033] Please also refer to FIG. 3A to FIG. 3C , which are schematic cross-sectional views of Embodiment 2 of the direct electrical connection flip-chip package structure of the semiconductor chip of the present invention. Embodiment 2 of the present invention is similar to Embodiment 1, and the main difference is that an electrode pad is formed on the lower surface of the dielectric layer, so that the semiconductor chip and the electrode pad are exposed to the outside, reducing the overall height of the structure, and realizing the purpose of lightness, thinness and shortness. And because it has electrode pads, it can further provide electrical connection to external electronic components.

[0034] Please refer to FIG. 3A, the semiconductor chip direct electrical connection flip-chip packaging structure of the present invention includes: at least one semiconductor chip 33, and the active surface 331 of the semiconductor chip 33 is formed with an electrical connection pad 331a;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More