Safety detecting method for system integrated chip with built-in non-volatile memory

A non-volatile memory and system integration technology, applied in static memory, semiconductor/solid-state device testing/measurement, electronic circuit testing, etc., can solve problems such as low security, inflexible application, and inability to re-enter test mode. Achieve high security and ensure data security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

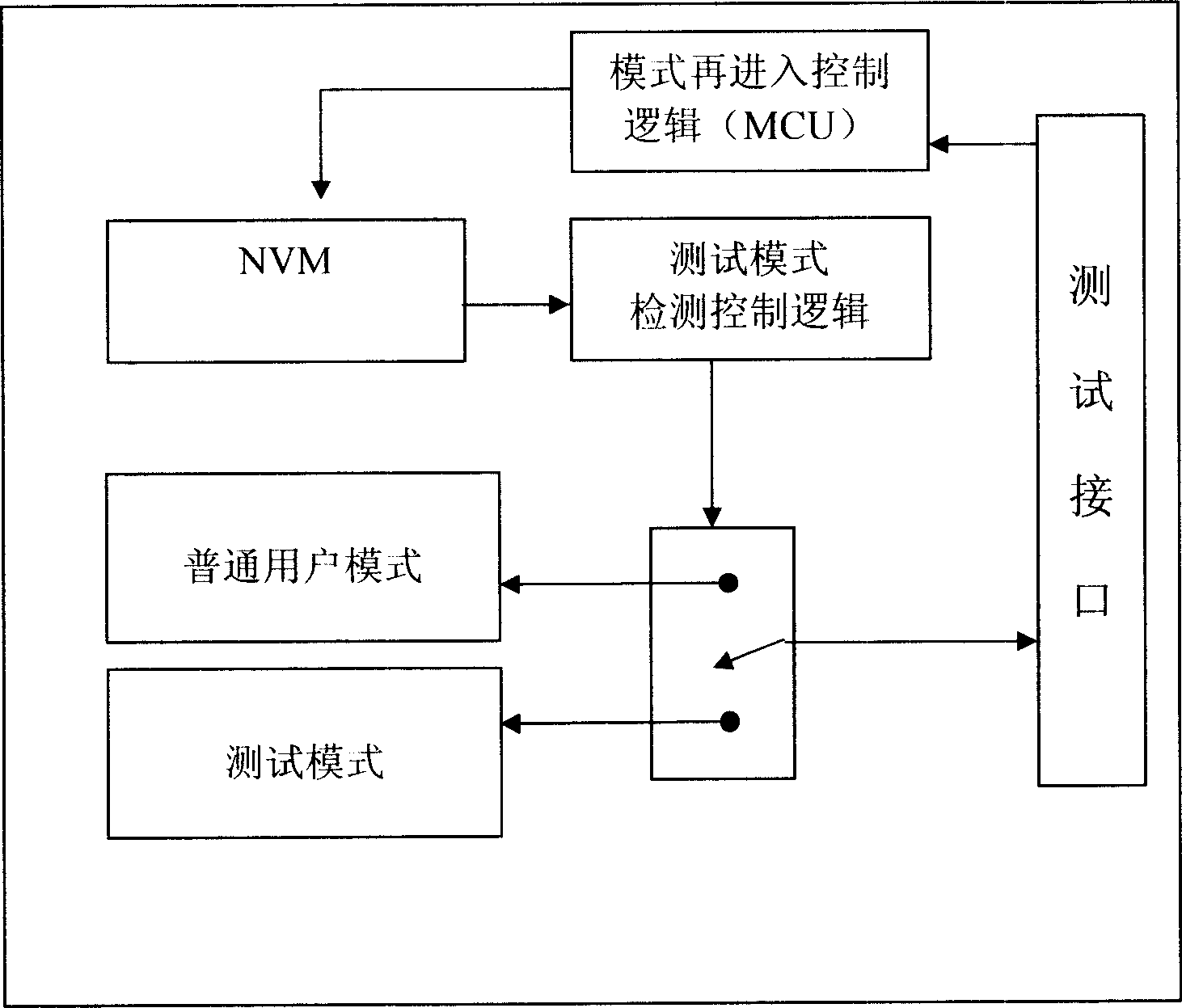

[0011] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0012] The NVM embedded in the SOC chip, such as flash memory (Flash), electrically erasable programmable read-only memory (EEPROM) etc., its data has the characteristic of power-down retention, the present invention utilizes this characteristic to carry out between test mode and user mode switch.

[0013] Referring to the accompanying drawings, the present invention sets a test mode detection control logic, which realizes the switching of the test mode based on the judgment of the data of the embedded NVM specific address, which is inaccessible in the user mode. In the initial state after the chip is manufactured, since the data at the specific address of the NVM is non-specified data, the chip is in the test mode state, and the internal module test can be realized directly through the chip pins. When the test is completed, the specified mode setting data i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More