Semiconductor structure and method of forming a semiconductor structure

a technology of semiconductor structure and semiconductor structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of worse control capability of gate for corresponding channels, and achieve the effect of enhancing heat dissipation effect, widening width, and increasing the volume of the bottom fin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

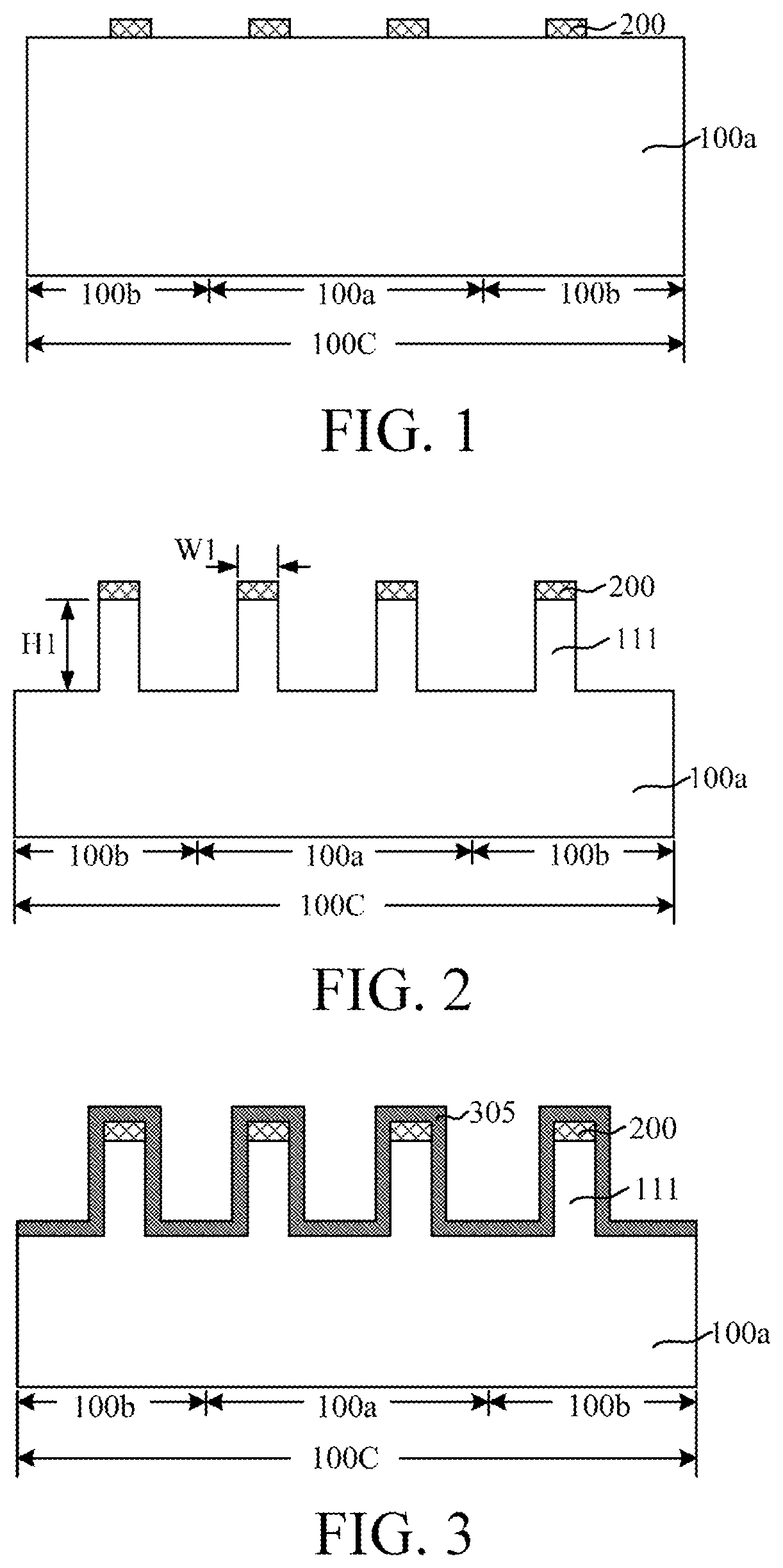

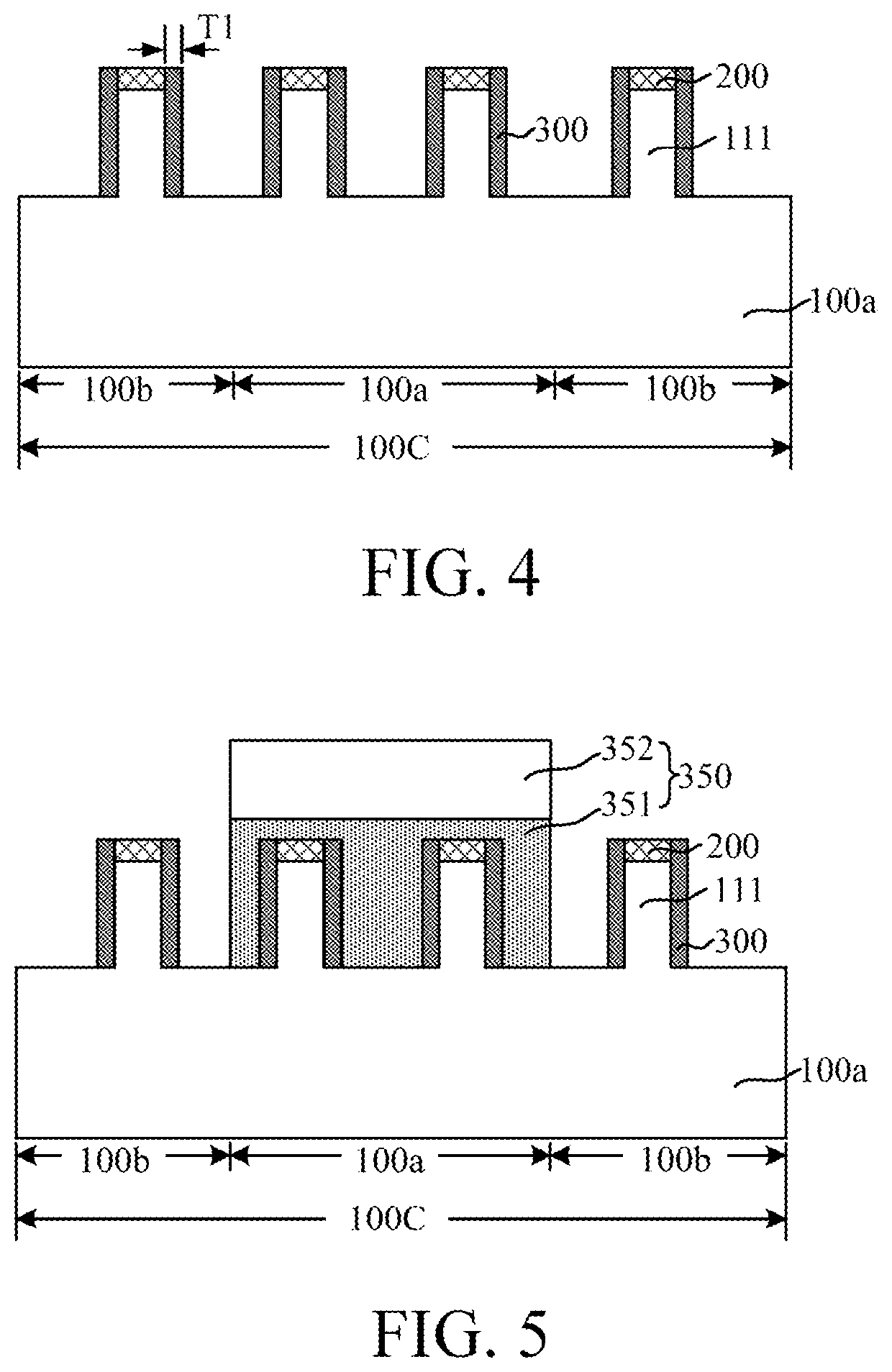

[0014]At present, after a fin structure is introduced to a semiconductor structure, the device performance is easily degraded. The cause of the performance degradation is as follows:

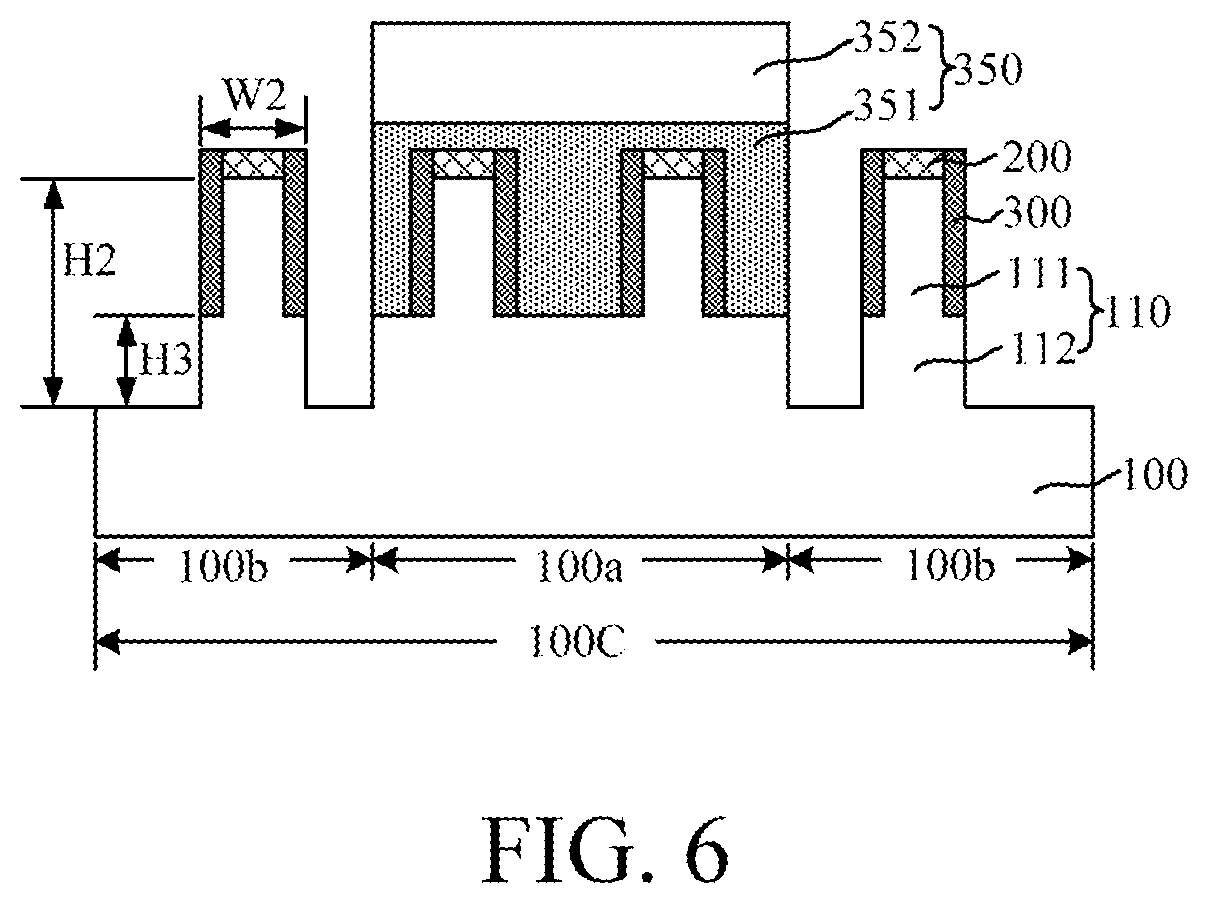

[0015]Compared with a planar transistor, a space occupied by an isolation structure in a FinFET is enlarged, and the area of a contact surface of a fin and a substrate is relatively small, thereby worsening a heat dissipation effect of a device. Further, the material of the isolation structure is generally silicon oxide, which has a smaller heat conductivity coefficient compared with the material of the substrate, thereby further worsening the heat dissipation effect of the device, and causing a more severe self-heating effect of the device, and correspondingly more severe performance degradation of the device.

[0016]To address the technical problem, in some implementations of the present disclosure, a formed fin includes a bottom fin and a top fin located on the bottom fin, where a width of the bottom fi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| pressure | aaaaa | aaaaa |

| semiconductor structure | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More