Signal processing semiconductor integrated circuit device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] Preferred embodiments of the present invention are explained by referring to the diagrams as follows.

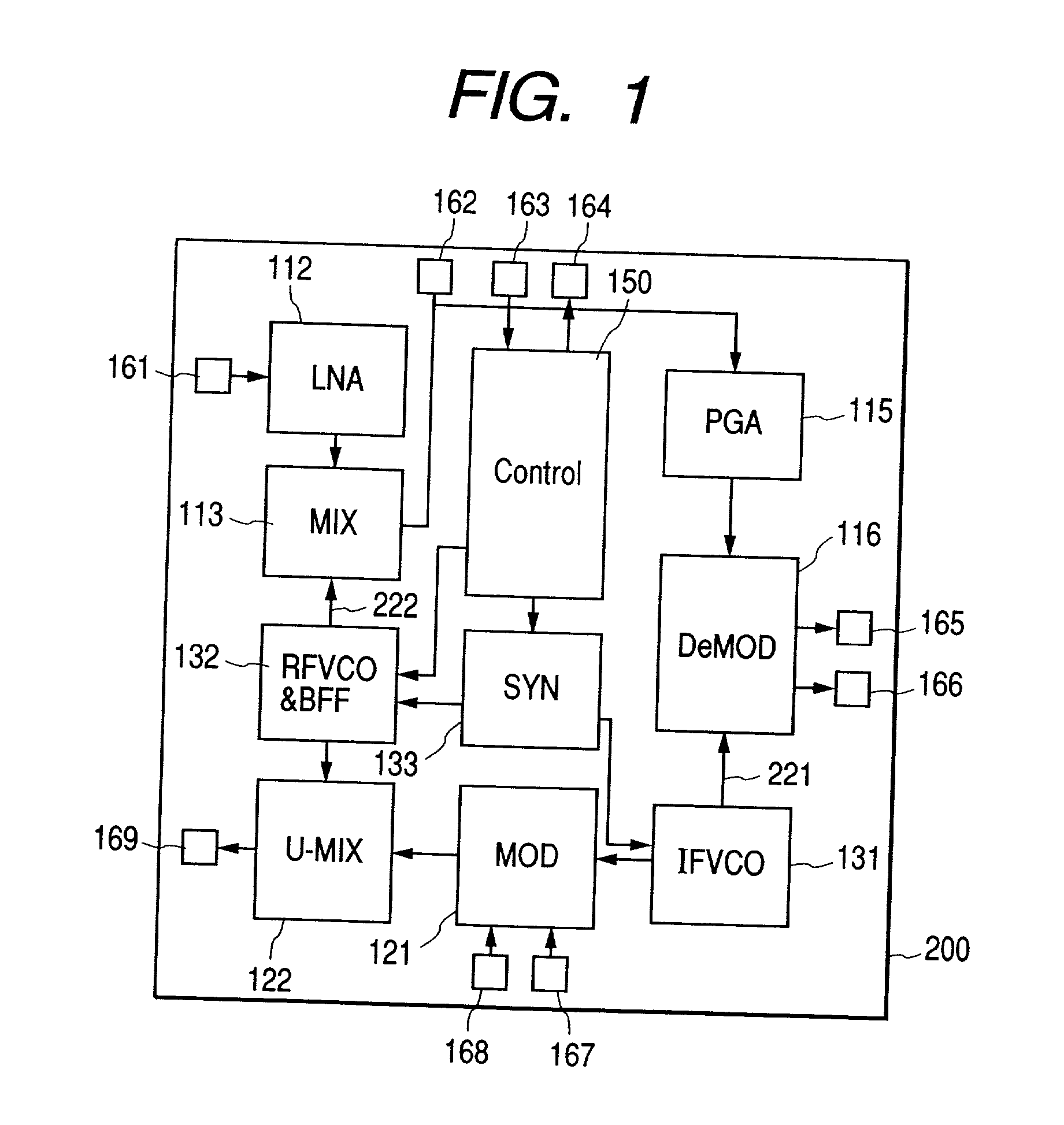

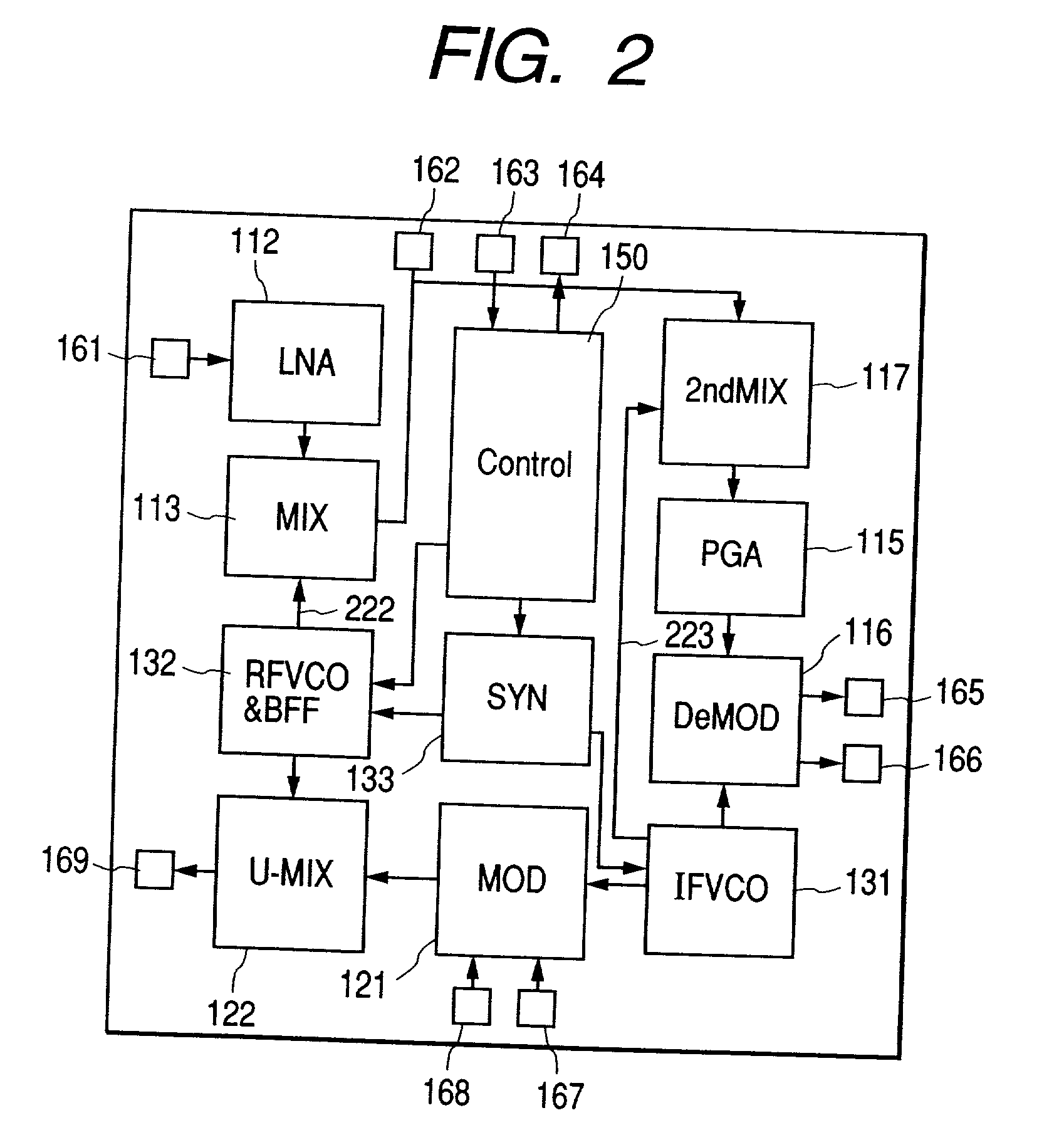

[0052] FIG. 1 is an explanatory diagram referred to in a description of a layout of an embodiment applying the present invention to a signal-processing semiconductor integrated circuit employed in a radio-communication system adopting a single super-heterodyne technique. The signal-processing semiconductor integrated circuit comprises the circuit blocks shown in FIG. 11. To be more specific, a single chip 200 implementing the signal-processing semiconductor integrated circuit includes the reception-system circuit 110 (excluding the band-limiting filter (FLT) 111 and the band-pass filter (BPF) 114), the transmission-system circuit 120 (excluding the power amplifier (PA) 123, the oscillation-system circuit 130 and the system controller 150). The layout of the circuit blocks is devised to reduce the number of spurious noises. The band-limiting filter (FLT) 111 and the band-pass f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More