Method and apparatus for reducing on-chip memory in vertical video processing

a technology of video processing and memory, applied in the field of video processing, can solve the problems of inability to achieve any kind of processing, no longer providing the data needed, and no longer being done at all, so as to achieve the effect of significantly reducing the memory requirements of the system, reducing the cost of the system, and reducing the requirement of on-chip memory for high-quality vertical processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] An invention for a method and apparatus for reducing on-chip memory in vertical video processing is disclosed. In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be understood, however, to one skilled in the art, that the present invention may be practiced without some or all of these specific details. In other instances, well known process operations have not been described in detail in order not to unnecessarily obscure the present invention.

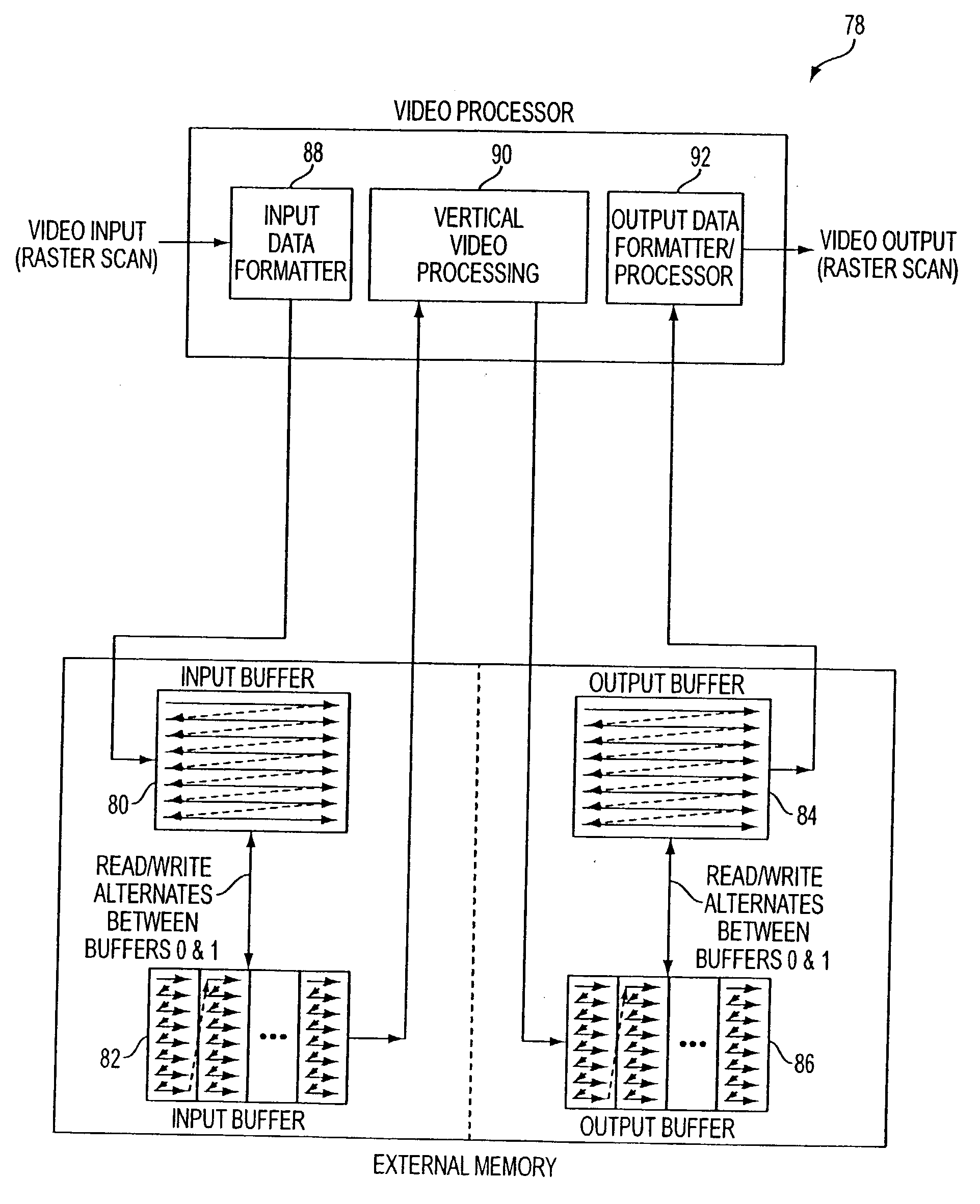

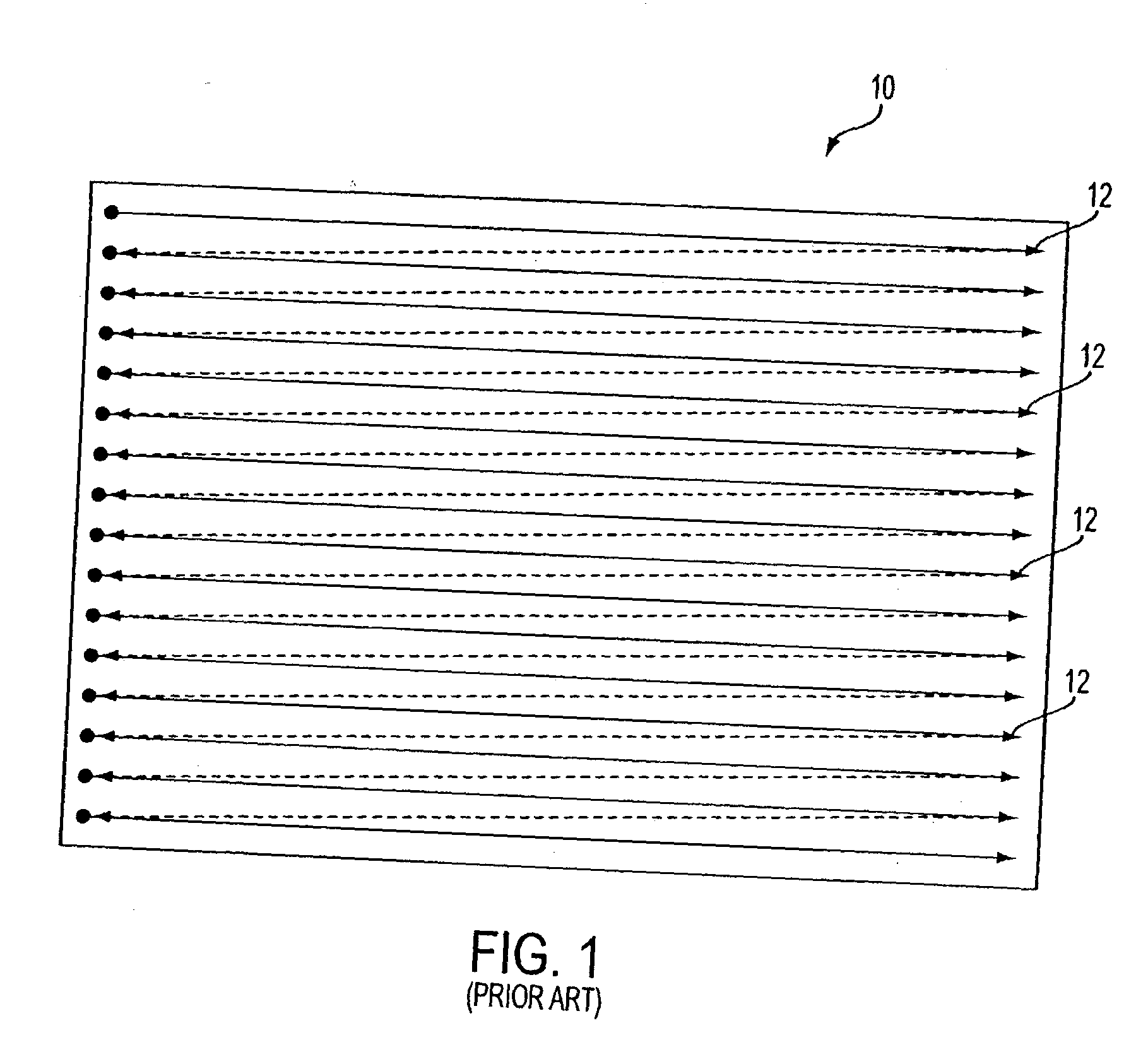

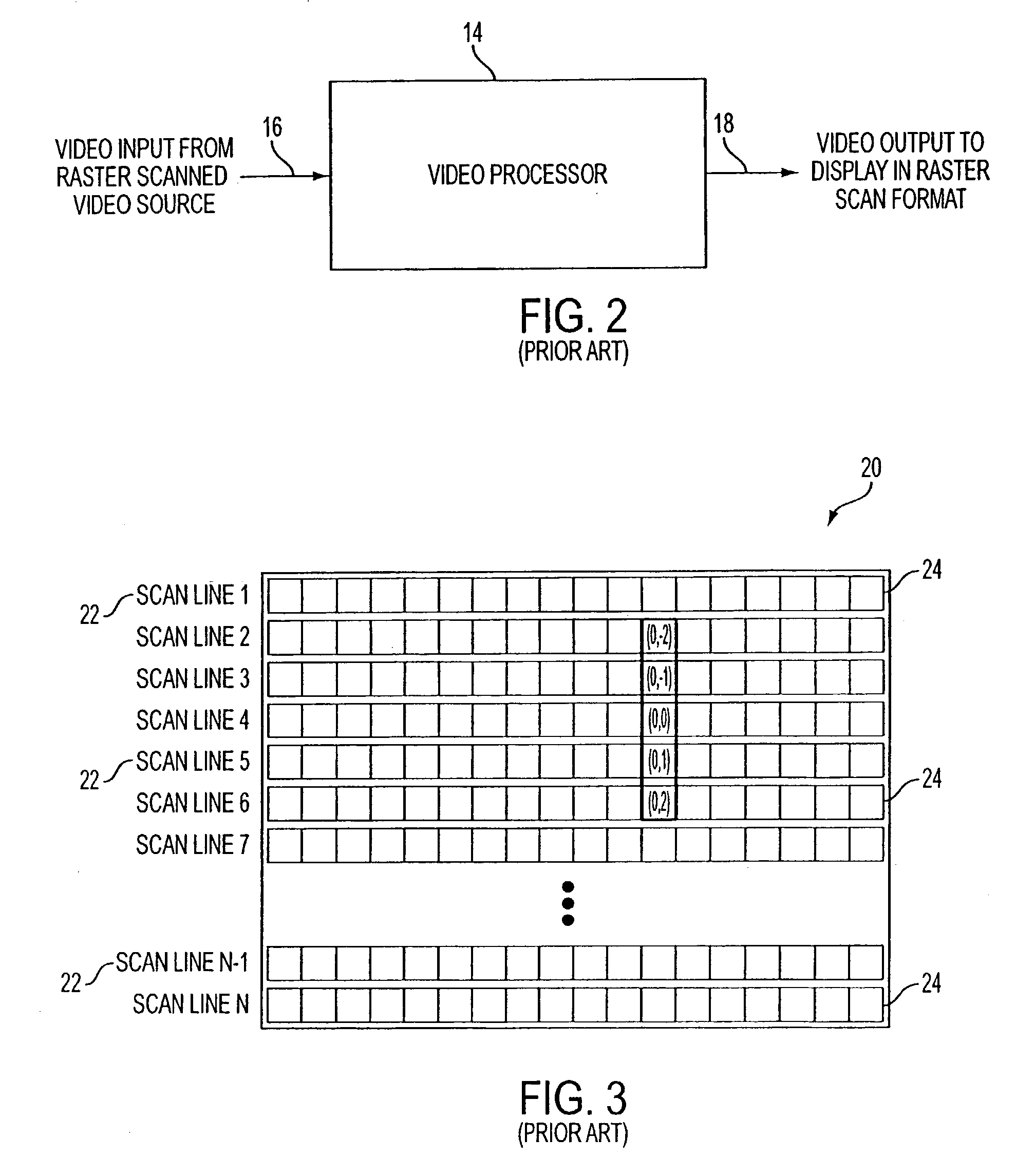

[0031]FIGS. 1-3 were described in terms of the prior art. FIG. 4 illustrates a video frame 25 of the present invention subdivided into a number of vertical slices 26 for a slice scanning sequence exemplified by a corresponding number of scan lines 28. Each slice 26 is scanned in a format similar to that used in a conventional raster-scanned sequence, with the scanning sequence proceeding to the subsequent slice when the end of a given slic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More