Semiconductor device and manufacturing metthod thereof

a technology of semiconductor devices and semiconductor chips, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of difficult uniform and stable mounting of elastomers, inability to conduct stably bonding steps to semiconductor chips, and restricted packaging number of pins, so as to achieve low cost and improve sealing properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

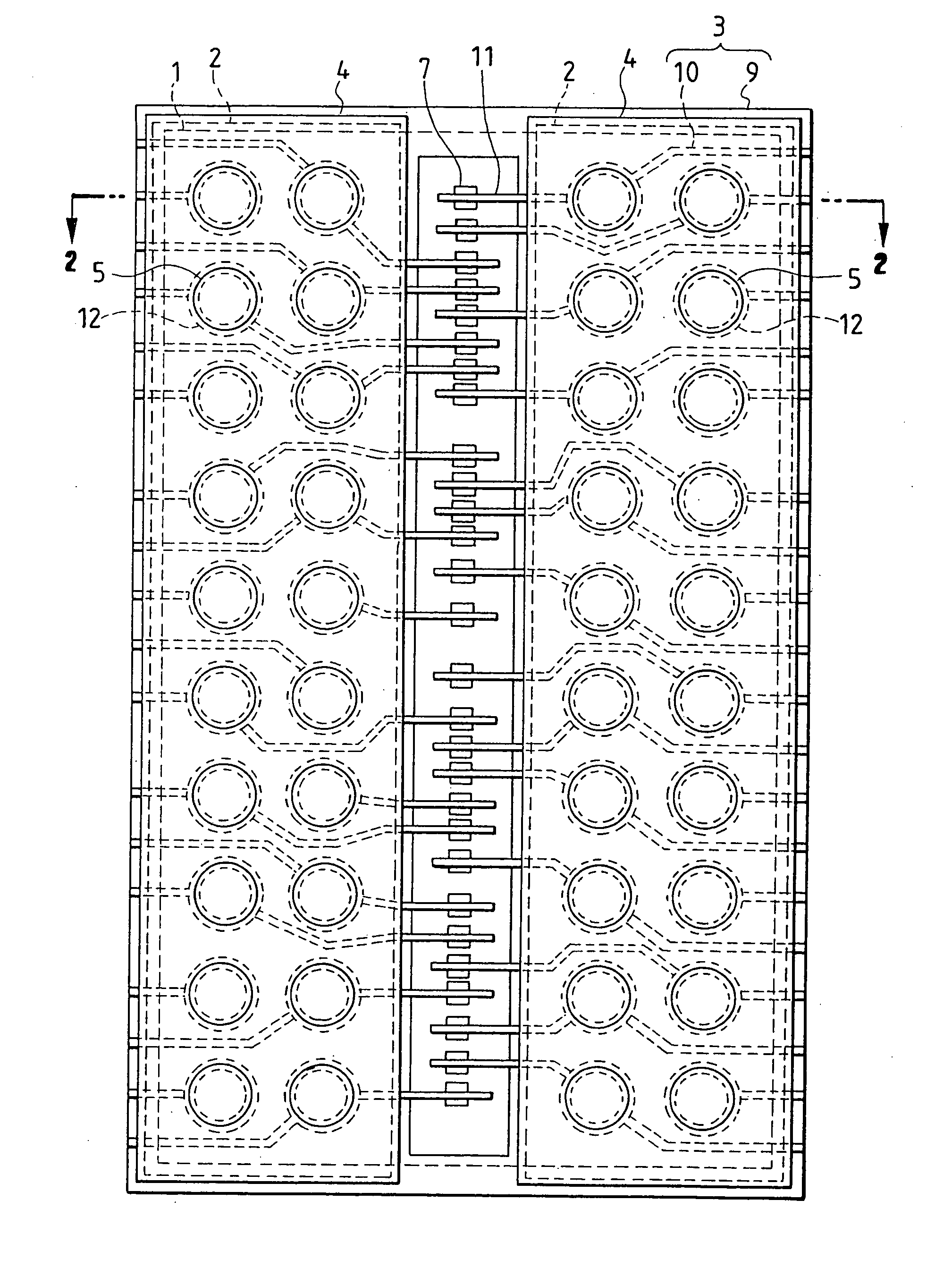

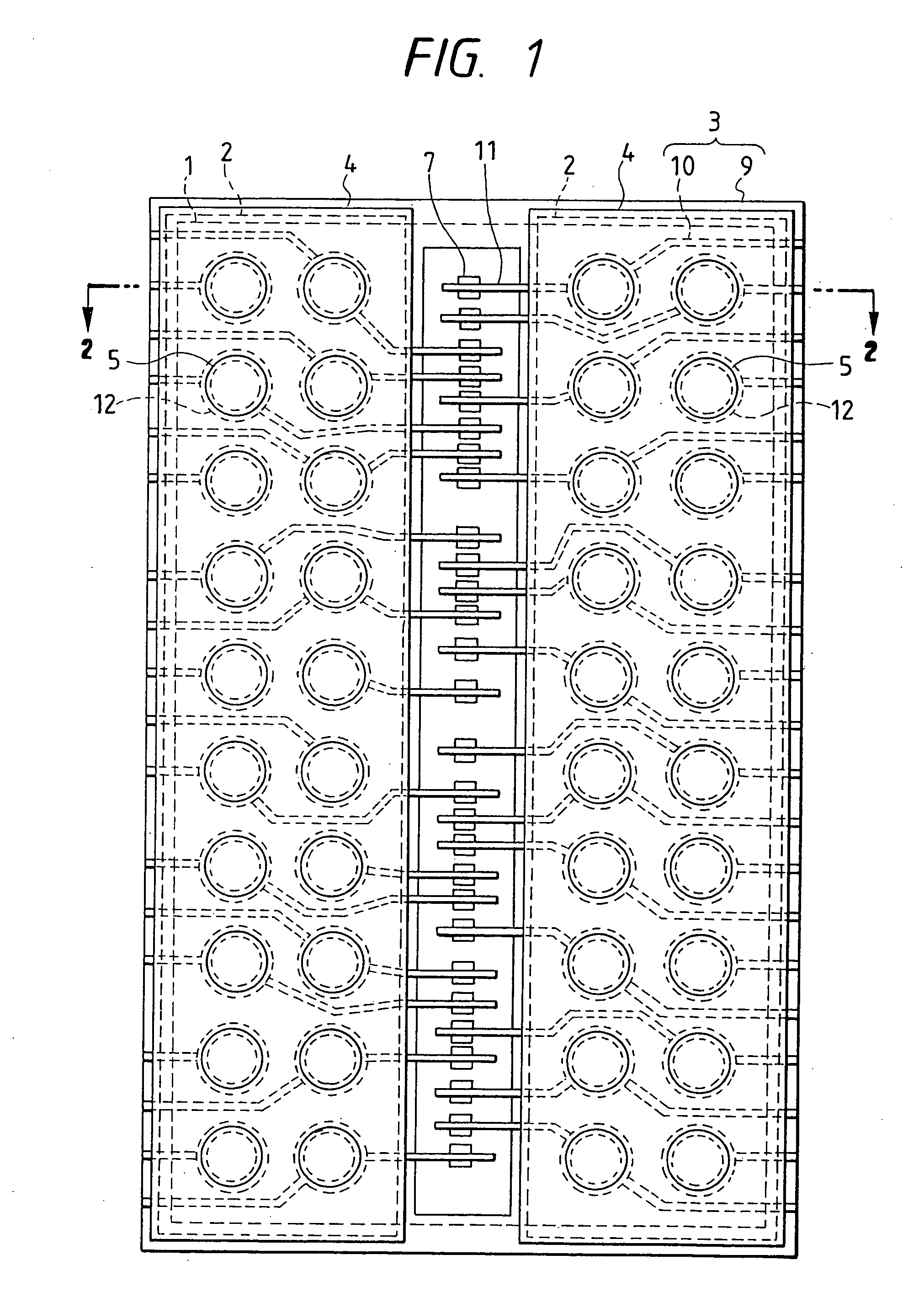

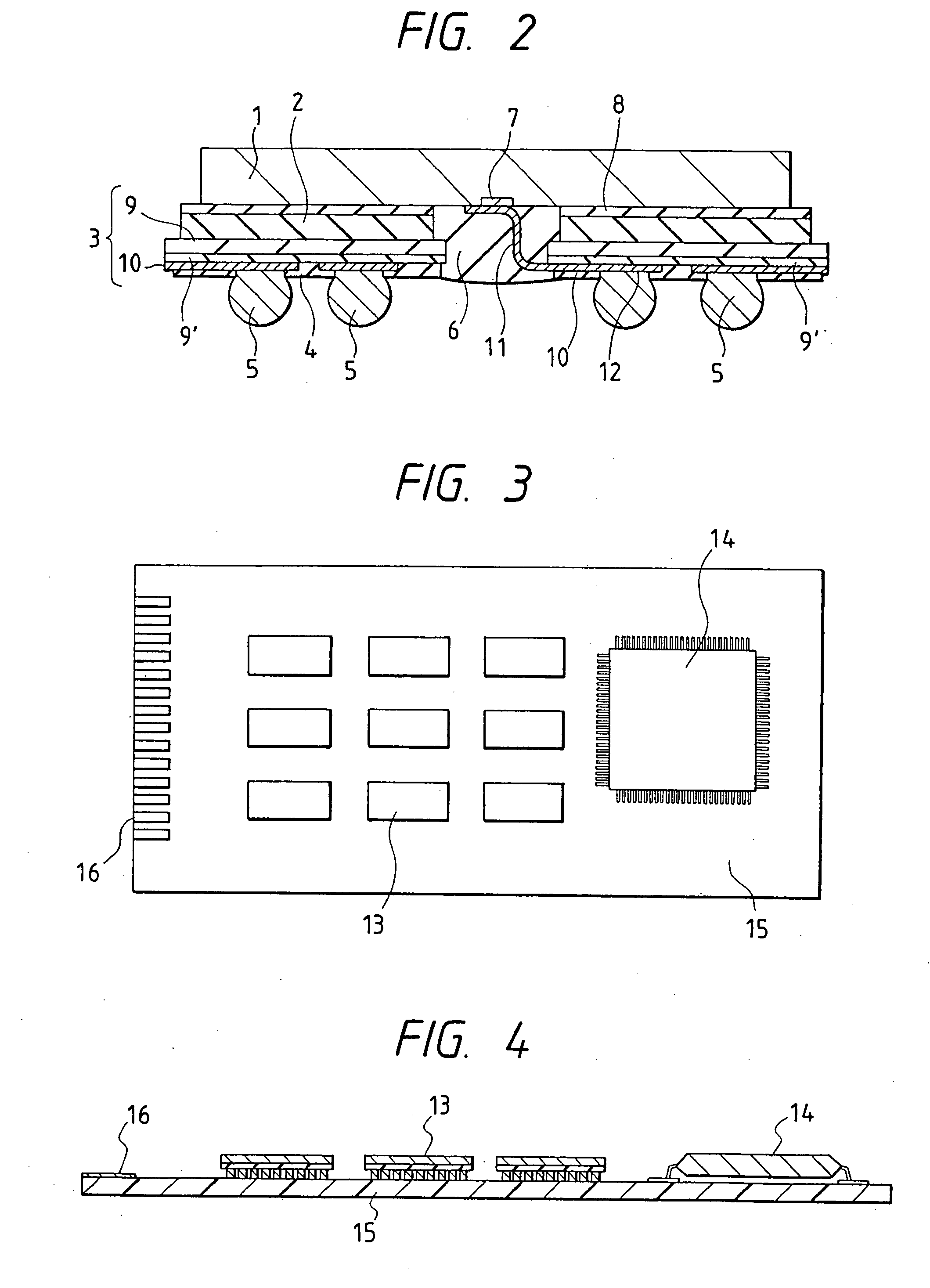

[0219]FIG. 1 is a plan view illustrating a semiconductor integrated circuit device representing an Embodiment 1 according to the present invention, FIG. 2 is a cross sectional view taken along line 2-2 in FIG. 1, FIG. 3 and FIG. 4 are a plan view and a cross sectional view illustrating a state of mounting a semiconductor integrated circuit device to a mounting substrate, FIG. 5 is a flow chart illustrating the steps (process) of assembling a semiconductor integrated circuit device, and FIG. 6 to FIG. 58 and FIG. 76 to FIG. 81 are views for comparative explanation between the feature of the semiconductor integrated circuit device representing the Embodiment 1 of the present invention and a semiconductor integrated circuit device representing a comparative example studied by the present inventors. At first, an explanation will be given as to the constitution of a semiconductor integrated circuit device of an Embodiment 1 with reference to FIG. 1 and FIG. 2.

[0220] The semiconductor in...

embodiment 2

[0355]FIG. 59 and FIG. 60 are a cross sectional view and a perspective view, respectively, illustrating a rear face wiring solder resist structure in the semiconductor integrated circuit device of Embodiment 2 according to the present invention.

[0356] The semiconductor integrated circuit device of the Embodiment 2 is a ball grid array type semiconductor package like that of the Embodiment 1, but it is different from the Embodiment 1 in that it is not based on the surface wiring technique, but is based on and provided for improving a rear face wiring structure. For instance, as shown in FIG. 59 and FIG. 60, in a structure comprising an elastomer 2 (elastic structural material) bonded on a main surface of a semiconductor chip (not shown) and a flexible wiring substrate 3 (wiring substrate) bonded to a main surface of the elastomer 2, a solder resist 56 (insulation film) is formed on the rear face of the flexible wiring substrate 3.

[0357] That is, the flexible wiring substrate 3 comp...

embodiment 3

[0365]FIG. 61 is a plan view of a semiconductor integrated circuit device forming an Embodiment 3 according to the present invention, as viewed from the rear face of a semiconductor chip, FIG. 62 is a plan view thereof, FIG. 63 is a cross sectional view thereof, FIG. 64 is an enlarged cross sectional view of a portion A in FIG. 63 and FIG. 65 is a plan view for explaining the wiring structure of the wiring substrate.

[0366] A semiconductor integrated circuit device in the Embodiment 3 adopts, instead of a semiconductor package having a structure in which the bonding pad is formed approximately at the center of the chip, as in the Embodiments 1 and 2 described above, a packaging structure using a semiconductor chip 1a in which a pad is formed to the periphery of the chip, as shown in FIG. 61 to FIG. 65, and in which bumps 5a connected to the bonding pads to the semiconductor chip 1a are disposed in a region inward of the outer circumference of the semiconductor chip 1a. The Embodimen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More