Address generators integrated with parallel FFT for mapping arrays in bit reversed order

a technology of address generator and mapping array, which is applied in the field of address generator integrated with parallel fft for mapping array in bit reversed order, can solve the problems of inefficient conventional ipbr method, inability to justify additional data memory requirements of oopbr, and hidden cycle penalties of fft using oopbr, so as to improve the in-place bit reversal (ipbr) process, improve processing efficiency, and optimize fft software

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

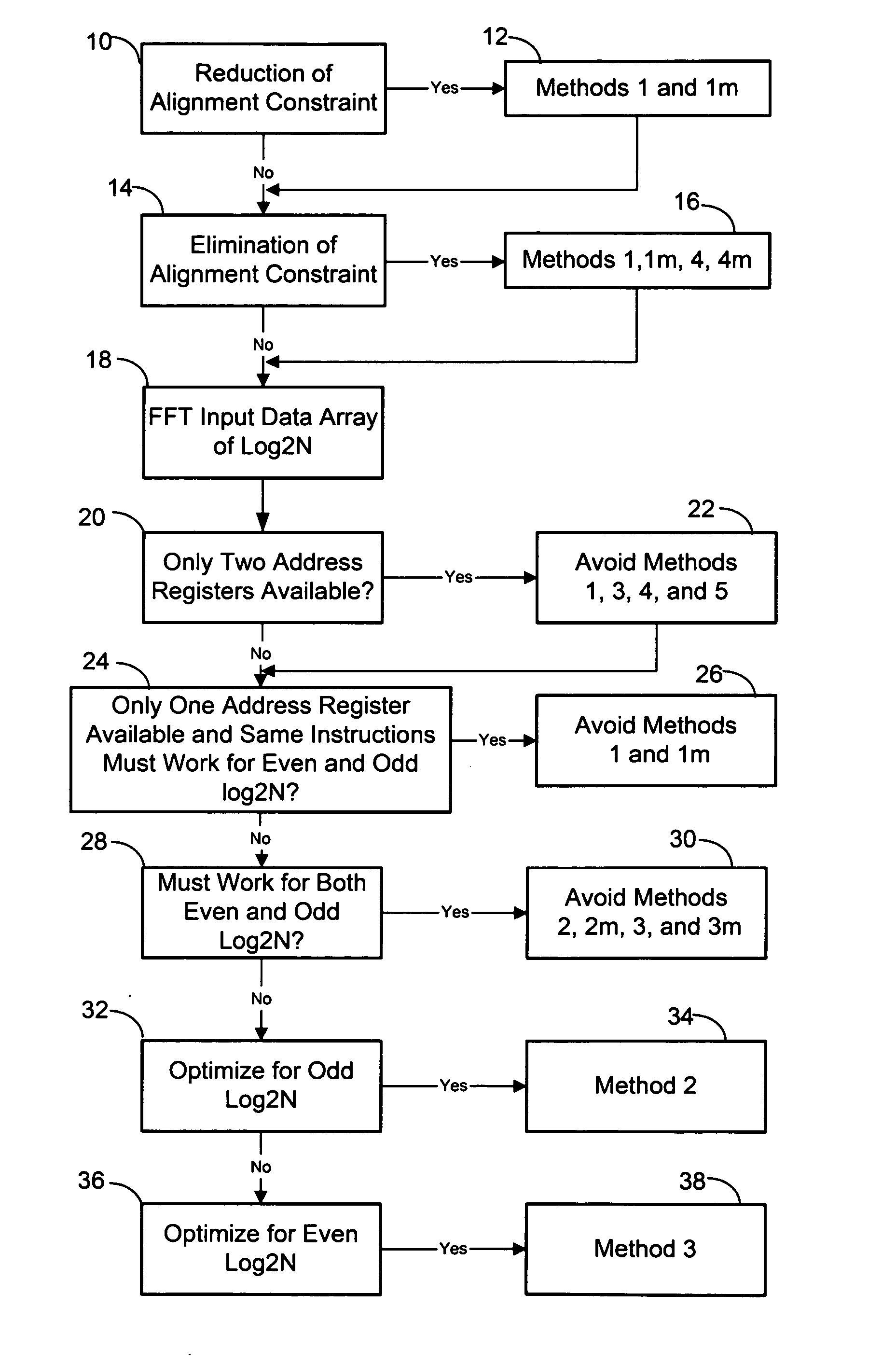

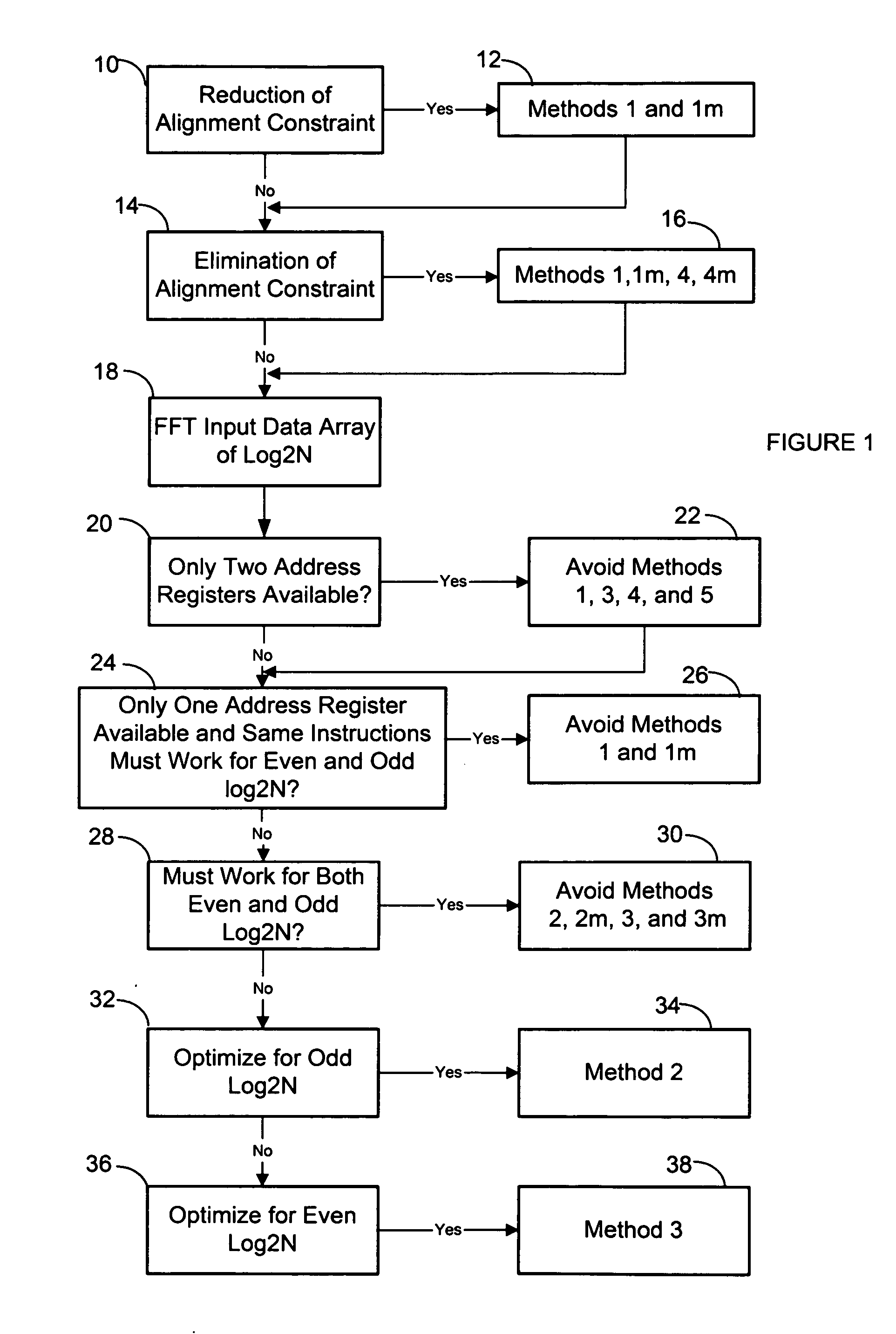

[0044] The preferred and alternative exemplary embodiments of the present invention include methods of in place bit reversal (IPBR) that are computationally efficient patterns to generate sequential address pairs for computing fast Fourier transforms (FFTs) in parallel with the address pair generation, in a processor. To decide which IPBR methods is most efficient for a specific application, reference is made to the decisional flowchart of FIG. 1. Assume an input array 10 is stored in 2{circumflex over ( )}(log2N+M) contiguous words of memory, beginning at start address S_in. The array has 2{circumflex over ( )}log2N elements and each element is stored in 2{circumflex over ( )}M contiguous words of data memory. For example, four words of contiguous memory would accommodate two words of precision for both the real and imaginary part of complex input data elements.

[0045] Five new IPBR address generators for mapping arrays in bit reversed order are disclosed. Methods 1m, 2m, 3m, 4m ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More